# Contents

| Chapter           | 1 | Introduction                                            |             |

|-------------------|---|---------------------------------------------------------|-------------|

| 1.1<br>1.2<br>1.3 |   | Purpose of the Book<br>Objectives<br>Prerequisites      | 1<br>2<br>2 |

| 1.3               |   | Overview of the Book                                    | 2           |

| 1.5               |   | Hardware and Software Requirements                      | 4           |

| Chapter           | 2 | What is Assembly Language?                              |             |

| 2.1               |   | Levels of Languages                                     | 5           |

| 2.2               |   | Examples of Different Levels of Languages               | 6           |

| 2.3               |   | Methods of Language Translation                         | 7           |

| 2.4               |   | Procedures for Developing an Assembly Language Programs | 9           |

| 2.5               |   | Main Ideas                                              | 10          |

| Chapter           | 3 | The Structure of Data                                   |             |

| 3.1               |   | Relationship of Data to a Program                       | 11          |

| 3.2               |   | Bit Quantities                                          | 12          |

| 3.3               |   | Number Conversions                                      | 13          |

| 3.4               |   | Data Representation                                     | 25          |

| 3.5               |   | Constants and Variables                                 | 30          |

| 3.6               |   | Main Ideas                                              | 31          |

| Chapter           | 4 | The Structure of the TI Home Computer                   |             |

| 4.1               |   | The Parts of a Computer System                          | 33          |

| 4.2               |   | Main Ideas                                              | 39          |

| Chapter           | 5 | Anatomy of Assembly Language Statements                 |             |

| 5.1               |   | Statement Fields                                        | 41          |

| 5.2               |   | Program Example                                         | 42          |

| 5.3               |   | Statement Syntax                                        | 45          |

| 5.4               |   | Main Ideas                                              | 49          |

|                   |   |                                                         |             |

۷

| 6.4Jump Instructions546.5Arithmetic Instructions556.6Logical Instructions566.7Branch and Subroutine Instructions576.8CRU and External Instructions58Chapter7Addressing Formats: General77.1Addressing Formats: Overview597.2General Addressing Modes607.3Word and Byte Addressing727.4A Look at Another Instruction (Add Words)747.5Summary75Chapter8Addressing Formats: Immediate and PC-Relative8.1Immediate Addressing818.3Building a Program Example 88848.4Summary89Chapter9Introduction to the Editor and Assembler929.1The Editor929.2The Assembler949.3Summary101Chapter 10Introduction to the Loader and Debugger10310.2Using the Loader10310.2Using the Debugger105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Chapter 6             | Instruction Set Overview                      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------|-----|

| 6.3       Compare Instructions       53         6.4       Jump Instructions       54         6.5       Arithmetic Instructions       55         6.6       Logical Instructions       56         6.7       Branch and Subroutine Instructions       57         6.8       CRU and External Instructions       57         6.8       CRU and External Instructions       59         7.1       Addressing Formats: General       71         7.1       Addressing Modes       60         7.2       General Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler       92         9.1       The Editor       92       92       104       9.3       Summary       101         Chapter       10       Introduction to the Loader and                                                                          | 6.1                   | Functional Categories                         | 51  |

| 6.4       Jump Instructions       54         6.5       Arithmetic Instructions       55         6.6       Logical Instructions       56         6.7       Branch and Subroutine Instructions       57         6.8       CRU and External Instructions       58         Chapter       7       Addressing Formats: General       72         7.1       Addressing Formats Overview       59         7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing       77         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       84         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler       92         9.1       The Editor       92       92         9.2       The Assembler       94       9.3         9.3       Summary       103         10.2       Using the Loader                                                                                                           | 6.2                   | Data Movement Instructions                    | 52  |

| 6.5       Arithmetic Instructions       55         6.6       Logical Instructions       56         6.7       Branch and Subroutine Instructions       57         6.8       CRU and External Instructions       58         Chapter       7       Addressing Formats: General       58         7.1       Addressing Formats: Overview       59         7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative       81         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       105         10.3                                                                                   | 6.3                   | Compare Instructions                          | 53  |

| 6.6       Logical Instructions       56         6.7       Branch and Subroutine Instructions       57         6.8       CRU and External Instructions       58         Chapter       7       Addressing Formats: General       59         7.1       Addressing Formats Overview       59         7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative       81         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       89         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler       92         9.1       The Editor       92       92       94         9.3       Summary       101       101         Chapter       10       Introduction to the Loader and Debugger       103         10.2       Using the Loader       103       105         10.3                                                                                      | 6.4 Jump Instructions |                                               | 54  |

| 6.7       Branch and Subroutine Instructions       57         6.8       CRU and External Instructions       58         Chapter       7       Addressing Formats: General       59         7.1       Addressing Formats: Overview       59         7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       105         10.2       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115                                                                                  |                       |                                               | 55  |

| 6.8       CRU and External Instructions       58         Chapter       7       Addressing Formats: General       59         7.1       Addressing Formats Overview       59         7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       105         10.2       Using the Loader       103         10.3       Summary       115         Chapter 11       Data Movement Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB                                                                |                       | -                                             |     |

| Chapter       7       Addressing Formats: General         7.1       Addressing Formats: Overview       59         7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter       9       Introduction to the Editor and Assembler         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter       10       Introduction to the Loader and Debugger       105         10.3       Summary       115       115         Chapter       11       Using the Loader       103         10.2       Using the Debugger       105       105         10.3       Summary       115       115         Chapter       11                                                                                                    | -                     |                                               |     |

| 7.1Addressing Formats Overview597.2General Addressing Modes607.3Word and Byte Addressing727.4A Look at Another Instruction (Add Words)747.5Summary75Chapter 88.1Immediate Addressing8.1Immediate Addressing818.2PC-Relative Addressing818.3Building a Program Example 88848.4Summary89Chapter 9Introduction to the Editor and Assembler9.1The Editor929.2The Assembler949.3Summary101Chapter 10Introduction to the Loader and Debugger10.1Using the Loader10310.2Using the Loader10510.3Summary115Chapter 11Data Movement Instructions11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Immediate Instructions (LWPI and LIMI)12111.4The Sore Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.8                   | GRU and External Instructions                 | 58  |

| 7.2       General Addressing Modes       60         7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter       8       Addressing Formats: Immediate and PC-Relative       81         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       89         Chapter       9       Introduction to the Editor and Assembler       92         9.1       The Editor       92       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       105         10.3       Summary       115         Cluapter 11       Data Movement Instructions       115         Cluapter 11       Data Movement Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Inmediate Instructions (LWI and LIMI)       122         11.5       The Store Internal Registers Instructions (LWPI and STST)       124         11.6       T                                      | Chapter 7             | Addressing Formats: General                   |     |

| 7.3       Word and Byte Addressing       72         7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter 8       Addressing Formats: Immediate and PC-Relative       8.1         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions       118         11.2       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       121         11.4       The Cold Internal                                                       |                       |                                               | 59  |

| 7.4       A Look at Another Instruction (Add Words)       74         7.5       Summary       75         Chapter 8       Addressing Formats: Immediate and PC-Relative       8.1         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       105         10.2       Using the Loader       103         10.3       Summary       115         Chapter 11       Data Movement Instructions       118         11.2       The Swap Bytes Instruction (SWPB)       118         11.2       The Swap Bytes Instruction (LI)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       122         11.4       The Solar Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125 <td></td> <td></td> <td>60</td> |                       |                                               | 60  |

| 7.5       Summary       75         Chapter 8       Addressing Formats: Immediate and PC-Relative       81         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.2       Using the Loader       103         10.3       Summary       115         Chapter 11       Data Movement Instructions       116         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Immediate Instructions (LWPI and LIMI)       121         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                            |                       |                                               |     |

| Chapter 8       Addressing Formats: Immediate and PC-Relative         8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions       118         11.2       The Swap Bytes Instruction (SWPB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       121         11.4       The Store Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                 |                       | · , ,                                         |     |

| 8.1       Immediate Addressing       77         8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       81         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.2       Using the Loader       103         10.3       Summary       115         Chapter 11       Data Movement Instructions       116         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       122         11.4       The Load Internal Registers Instructions (LWPI and STST)       124         11.5       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                     | 7.5                   | Summary                                       | 75  |

| 8.2       PC-Relative Addressing       81         8.3       Building a Program Example 88       89         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions       115         Chapter 11       Data Movement Instruction (SWPB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       122         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                   | Chapter 8             | Addressing Formats: Immediate and PC-Relative |     |

| 8.3       Building a Program Example 88       89         8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions       115         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       122         11.5       The Store Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                      | 8.1                   | Immediate Addressing                          | 77  |

| 8.4       Summary       89         Chapter 9       Introduction to the Editor and Assembler       92         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions       115         Chapter 11       Data Movement Instruction (SWPB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       122         11.5       The Store Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                                                                             | 8.2                   | PC-Relative Addressing                        | 81  |

| Chapter 9       Introduction to the Editor and Assembler         9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions       118         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LWPI and LIMI)       122         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                                                                                                                            | 8.3                   | Building a Program Example 88                 |     |

| 9.1       The Editor       92         9.2       The Assembler       94         9.3       Summary       101         Chapter 10 Introduction to the Loader and Debugger         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11 Data Movement Instructions         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Immediate Instructions (LI)       121         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.4                   | Summary                                       | 89  |

| 9.2The Assembler949.3Summary101Chapter 10Introduction to the Loader and Debugger10.1Using the Loader10310.2Using the Debugger10510.3Summary115Chapter 11Data Movement Instructions11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 9             | Introduction to the Editor and Assembler      |     |

| 9.3       Summary       101         Chapter 10       Introduction to the Loader and Debugger       103         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Internal Registers Instructions (LI)       121         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9.1                   | The Editor                                    | 92  |

| Chapter 10       Introduction to the Loader and Debugger         10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Immediate Instructions (LI)       121         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9.2                   | The Assembler                                 | 94  |

| 10.1       Using the Loader       103         10.2       Using the Debugger       105         10.3       Summary       115         Chapter 11       Data Movement Instructions         11.1       The Move Instructions (MOV and MOVB)       118         11.2       The Swap Bytes Instruction (SWPB)       120         11.3       The Load Inmediate Instruction (LI)       121         11.4       The Load Internal Registers Instructions (STWP and STST)       124         11.6       The Shift Instructions (SRL, SRA, SRC, and SLA)       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.3                   | Summary                                       | 101 |

| 10.2Using the Debugger10510.3Summary115Chapter 11Data Movement Instructions11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Inmediate Instruction (LI)12111.4The Load Internal Registers Instructions (STWP and STST)12411.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Chapter 10            | Introduction to the Loader and Debugger       |     |

| 10.2Using the Debugger10510.3Summary115Chapter 11Data Movement Instructions11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Inmediate Instruction (LI)12111.4The Load Internal Registers Instructions (STWP and STST)12411.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10.1                  | Lising the Loader                             | 103 |

| 10.3Summary115Chapter 11Data Movement Instructions11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Inmediate Instruction (LI)12111.4The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |                                               |     |

| 11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Immediate Instruction (LI)12111.4The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                     |                                               | 115 |

| 11.1The Move Instructions (MOV and MOVB)11811.2The Swap Bytes Instruction (SWPB)12011.3The Load Immediate Instruction (LI)12111.4The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Chapter 11            | Data Movement Instructions                    |     |

| 11.2The Swap Bytes Instruction (SWPB)12011.3The Load Immediate Instruction (LI)12111.4The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |                                               |     |

| 11.3The Load Immediate Instruction (LI)12111.4The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |                                               |     |

| 11.4The Load Internal Registers Instructions (LWPI and LIMI)12211.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |                                               |     |

| 11.5The Store Internal Registers Instructions (STWP and STST)12411.6The Shift Instructions (SRL, SRA, SRC, and SLA)125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |                                               |     |

| 11.6 The Shift Instructions (SRL, SRA, SRC, and SLA) 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |                                               |     |

| 11.7 Program Example 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       | Program Example                               |     |

| Chapter 12                                                   | Compare instructions                                                                                                                                                                                                                                                                                                                                                        |                                               |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 12.1<br>12.2<br>12.3<br>12.4                                 | The Compare Values Instructions (C, CB, and CI)<br>Using the Jump if Low or Equal Instruction (JLE)<br>The Compare Bits Instructions (COC and CZC)<br>Program Example                                                                                                                                                                                                       | 139<br>142<br>142<br>146                      |

| Chapter 13                                                   | The Jump Instructions                                                                                                                                                                                                                                                                                                                                                       |                                               |

| 13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7<br>13.8 | The Equal Testing Instructions (JEQ and JNE)<br>The Carry Testing Instructions (JOC and JNC)<br>The Jump if No Overflow Instruction (JNO)<br>The Jump if Odd Parity Instruction (JOP)<br>The Logical Evaluation Instructions (JH, JHE, JLE, JL)155<br>The Arithmetic Evaluation Instructions (JGT and JLT)<br>The Jump Unconditionally Instruction (JMP)<br>Program Example | 152<br>153<br>154<br>154<br>156<br>157<br>158 |

| Chapter 14                                                   | The Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                 |                                               |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6                 | The Add Instructions (AI, A, and AB)<br>The Subtract Instructions (S and SB)<br>The Increment and Decrement Instructions (INC, INCT, DEC, and<br>DECT)<br>The Negate Instruction (NEG)<br>The Absolute Value Instruction (ABS)<br>The Multiply and Divide Instructions (MPY and DIV)                                                                                        | 164<br>168<br>169<br>171<br>171<br>172        |

| 14.7<br>Chapter 15                                           | Program Example<br>The Logical Instructions                                                                                                                                                                                                                                                                                                                                 | 175                                           |

| 15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6                 | The Logical Instructions<br>The AND Operation Instructions (ANDI, SZC, and SZCB)<br>The OR Operation Instructions (ORI, SOC, and SOCB)<br>The Exclusive Or Instruction (XOR)<br>The Invert Instruction (INV)<br>The Initialize to Constant Instructions (CLR and SETO)<br>Program Example                                                                                   | 180<br>183<br>186<br>188<br>188<br>188        |

| Chapter 16                                                   | Branch and Subroutine Instructions                                                                                                                                                                                                                                                                                                                                          |                                               |

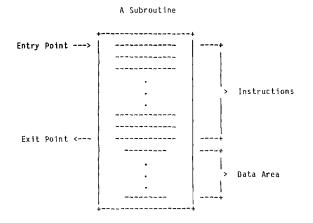

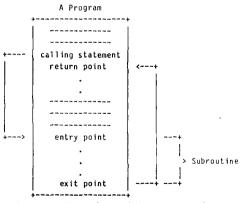

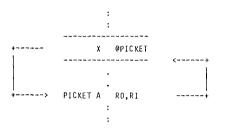

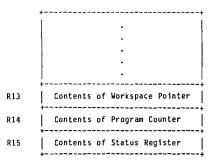

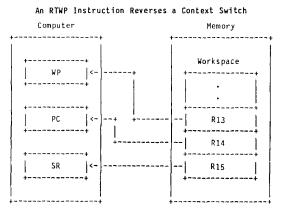

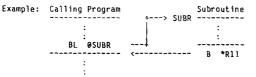

| 16.1<br>16.2<br>16.3<br>16.4<br>16.5                         | Subroutines<br>Non-Context Switching Subroutine Calls<br>Context Switching Subroutine Calls<br>Context Switching and Interrupts<br>Program Example                                                                                                                                                                                                                          | 193<br>195<br>198<br>202<br>202               |

•

vii

ç

standing anyon.

į

2010-01-02-000

| Ghapter I                            |                                                                                                                                                                                                                              |                                 |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

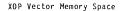

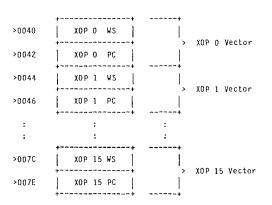

| 17.1<br>17.2<br>17.3<br>17.4<br>17.5 | The Communication Register Unit (CRU)<br>The CRU Single-Bit Instructions (SBO, SBZ, TB)<br>The CRU Multi-Bit Instructions (LDCR and STCR)<br>The External Instructions (IDLE, RSET, LREX, CKON, and CKOF)<br>Program Example | 209<br>210<br>214<br>217<br>218 |

| Chapter 18                           | Other Assembly Language Concepts                                                                                                                                                                                             |                                 |

| 18.1                                 | Expressions                                                                                                                                                                                                                  | 221                             |

| 18.2                                 | Relocation                                                                                                                                                                                                                   | 222                             |

| 18.3                                 | Assembler Directives                                                                                                                                                                                                         | 223                             |

| 18.4                                 | Assembler Errors                                                                                                                                                                                                             | 232                             |

| 18.5                                 | Comparison of Utility Packages                                                                                                                                                                                               | 233                             |

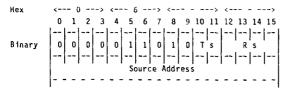

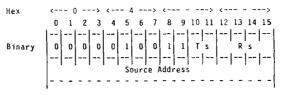

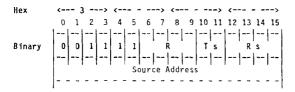

| Chapter 19                           | Machine Code Formats                                                                                                                                                                                                         |                                 |

| 19.1                                 | Relationship of Machine Code to Assembly Language                                                                                                                                                                            | 237                             |

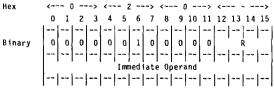

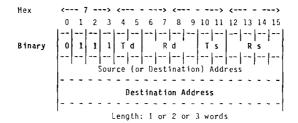

| 19.2                                 | Determining the Number of Words of Machine Code                                                                                                                                                                              | 238                             |

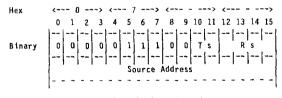

| 19.3                                 | Machine Code Fields                                                                                                                                                                                                          | 238                             |

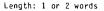

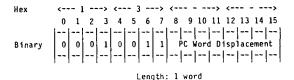

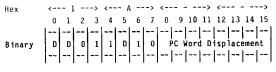

| 19.4                                 | The R Field                                                                                                                                                                                                                  | 240                             |

| 19.5                                 | The C Field                                                                                                                                                                                                                  | 240                             |

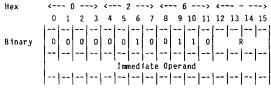

| 19.6                                 | The IOP Field                                                                                                                                                                                                                | 241                             |

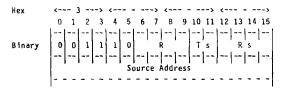

| 19.7                                 | General Addressing Mode Fields                                                                                                                                                                                               | 242                             |

| 19.8                                 | The Displacement Field                                                                                                                                                                                                       | 247                             |

| 19.9                                 | The PC Word Displacement Field                                                                                                                                                                                               | 248                             |

| Chapter 20                           | Summary                                                                                                                                                                                                                      | 25 <b>3</b>                     |

|                                      |                                                                                                                                                                                                                              | 0                               |

| Appendix A                           | Instruction Summaries                                                                                                                                                                                                        | 255                             |

| Appendix B                           | Number Tables                                                                                                                                                                                                                | 326                             |

| Appendix C                           | ASCII Character Table                                                                                                                                                                                                        | 327                             |

| Index                                |                                                                                                                                                                                                                              | 331                             |

### Chapter 17 CRU and External Instructions

# **CHAPTER 1**

## **INTRODUCTION**

This book introduces assembly language programming with the TI Home Computer.

### 1.1 Purpose of the Book

Texas Instruments offers a variety of hardware (equipment) and software to use for running and developing assembly language programs. The software includes the Editor/Assembler package, the line-by-line assembler and the debugger which come with the Mini Memory Module, and the software available with the UCSD p-System.

The specific operation and unique features of these products are described in the documentation that accompanies each one. A lot of this documentation assumes that you have previous assembly language experience and already know the assembly language of the TI Home Computer. If you don't have that kind of experience or knowledge, this book is for you. This book doesn't replace the existing documentation but, rather, supplements it.

The purpose of this book is to help you learn the basic concepts of assembly language programming using the Texas Instruments Home Computer. It's designed to help you learn the TI Home Computer's assembly language instruction set and the structure of assembly language programs. With this knowledge, you can

- · understand existing programs

- customize programs

- · create your own assembly language programs

With an understanding of assembly language, you begin to know the detailed architecture of the TI Home Computer and can apply your understanding to directly control the computer's programmable components.

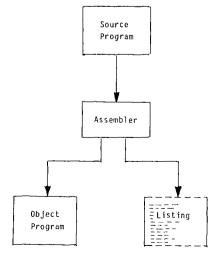

language, the translation program is called either an interpreter or a compiler. For an assembly language program, the translation program is called an assembler.

Here are a few "buzzwords" associated with the assembly process. They are:

- source program

- object program

- listing

A "source" program is the collection of assembly language statements which is translated by the assembler. The machine language program that results is called an "object" program. The assembler usually also produces a "listing." A listing is a printed document that shows:

- the assembly language statements that were given to the assembler

- the resulting machine code into which they were translated

- the locations in memory for the machine code

- other information such as a list of symbols used in the program

The listing also contains error messages if the assembler can't understand the assembly language statements, or if for some other reason, it can't produce the correct machine code. You can visualize the assembly process this way.

What is Assembly Language?

### 2.4 Procedures for Developing an Assembly Language Program

The steps for developing an assembly language program aren't that much different from the steps used to develop a high-level language program. The steps are as follows:

- 1. Define the program.

- 2. Compose the source program.

- 3. Assemble the source program into an object program.

- 4. Load the (object) program into memory.

- 5. Run the program.

- 6. Test the program.

- 7. Modify the program.

- 8. Document the program.

First, define what you want the program to do and how you want it to do its job.

When writing a program in BASIC, you can type in the statements of a program, compose the statements in the right order, and run the program. The BASIC interpreter translates and performs the instructions at one time.

When developing a program in assembly language, you perform these separate steps:

- compose the statements in the source program

- · have the source program assembled into an object program

- run the object program

With assembly language, you write the statements of your program and compose them into a source program. Usually, there is an Editor to help in composing the source program. An Editor is a program that lets you type in statements, collect them, and arrange them in the right order. After creating the source program, you use an Assembler to translate the source program into an object program and to produce a listing. Next, you load the object program into memory using a Loader. A loader is a program that reads an object program and stores the object code in memory. Then you run the program.

When you run your program, a Debugger is sometimes available to help you test your program and remove "bugs", or mistakes in the logic of a program. Often, as a result of testing a program, you modify it to fix bugs or change features.

Documentation is an important part of developing any program. By describing a program clearly and completely, you can more easily debug and modify it when necessary. Good documentation helps others understand your program, or, more importantly, helps you understand your program after being away from it.

This description provides an overview of the steps that are used to develop an assembly language program. Other chapters describe these steps in more detail.

### 2.5 Main Ideas

Computer languages are used to give directions to a computer. There are three levels: high-level language, assembly language, and machine language.

A high-level language is more oriented to human language than machine language. A high-level language is less efficient in terms of the required memory storage and the time required to run the program.

Assembly language is used to express machine language by using characters that people understand.

An assembler is a program that translates the assembler language statements of a source program into the machine code of an object program. The assembler usually produces a printed document called a listing that shows the result of the assembly process.

## THE STRUCTURE OF DATA

An assembly language program, like a high-level language program, consists of a collection of statements. The main purpose of these statements is to give an instruction to the computer or to define data. This chapter examines the structure of data and its relationship to a program.

### 3.1 Relationship of Data to a Program

Consider the following BASIC language program.

```

100 DATA 3,-8

110 READ A,8

120 C = A + B

```

Statement 100 defines two data items: a value of 3 and a value of -8. Statement 110 assigns the name A to the value 3 and the name B to the value -8. Statement 120 directs the computer to add the value called A and the value called B and call the sum C.

Consider a similar assembly language program for the TI Home Computer.

A'6, DATA 3 B DATA -8 C BSS 2 MDV @A,RO MDV @B,R1 A RO,R1 MDV R1,@C

The first three statements define data. The last four statements are instructions that specify an action for the computer to perform.

The first statement assigns the name A to the value 3. The second statement assigns the name B to the value -8. The third statement assigns the name C to a storage location. The BSS is an abbreviation for "Block Starting with Symbol". It reserves a block of memory and assigns a name to the beginning of that block. The 2 in the statement specifies

the number of bytes of memory to reserve. Memory is measured in bytes. A byte is a group of 8 bits.

The fourth statement is an instruction that moves, or copies, the number called A to a register numbered zero. A register is a special storage location that can be accessed faster than other storage locations. The fifth statement is an instruction that moves the number called B to a register numbered one.

The sixth statement is an instruction that adds the number in Register 0 to the number in Register 1 and replaces the number in Register 1 with the sum. The seventh statement is an instruction that moves the number in Register 1 (the sum) to the storage location called C.

The point is, an assembly language program, like a high-level language program, includes statements that define data and statements that direct the computer to perform some action. One step that you must take in assembly language programming is to allocate memory for data and define the structure of that data.

### 3.2 Bit Quantities

To the computer, all data is simply a collection of one and zero bits. With assembly language, you can directly manipulate individual bits.

The most basic unit of data that a computer can access is a bit. A bit is a single binary digit: a zero or a one. A single bit is usually too small a unit of data to be very useful by itself. More commonly, bits are grouped together to form larger numbers.

Just like a group of 12 doughnuts is called a dozen, names are also given to groups of bits. A group of 8 bits is called a "byte." A group of 4 bits is called a "nibble." Sometimes, it's convenient to refer to a pair of bits by a name. Let's call a two-bit quantity a "niblet" (a petite nibble).

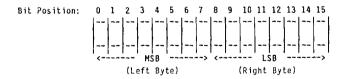

Another name given to a quantity of bits is "word." It's a term given to the maximum number of bits that a computer can handle at one time. The number of bits in a word depends upon the computer. Different computers have different word sizes. If someone asks you how many bits are in a word, you must first know what computer that person is talking about.

### Note

The word size of the TI Home Computer is 16 bits.

Sometimes, the expression "double word" is used. Just as you might expect, a double word contains twice as many bits as a word. The number of bits in a double word depends upon the number of bits in a word which, in turn, depends upon the computer.

Here's a summary list of these bit quantities.

| Bit         | A single binary digit (0 or 1)                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------|

| Niblet      | Two bits                                                                                                           |

| Nibble      | Four bits                                                                                                          |

| Byte        | Eight bits                                                                                                         |

| Word        | The number of bits in a word varies with the computer. For<br>the TI Home Computer, it's 16 bits.                  |

| Double Word | The number of bits in a double word depends upon the word size of the computer and equals two times the word size. |

### 3.3 Number Conversions

When writing programs in assembly language, you often deal with word and byte quantities and, sometimes, even smaller quantities of bits. Bits, of course, represent binary numbers. You need to be familiar with the binary number system; because you need to be able to convert a binary number into a decimal value and a decimal value into a binary value.

When reading or writing assembly language programs for the TI Home Computer, you also need to be familiar with the hexadecimal number system. The hexadecimal, or "hex", number system expresses binary values more concisely. For example, rather than writing out a 16-bit number like 1010011110011100, it's more concise to simply write the hexadecimal equivalent value, A79C.

Most of the time, binary numbers are expressed as hex numbers. If you can convert binary numbers to hex equivalents and hex numbers to binary equivalents, it is helpful. Additionally, knowing how to convert hex numbers into decimal equivalents and decimal numbers into hex equivalents is helpful as well.

In summary, knowing how to perform six kinds of number conversions is helpful when learning to program using assembly language. These conversions are:

- 1. a binary number number to a decimal equivalent

- 2. a hexadecimal number to a decimal equivalent

- 3. a binary number to a hexadecimal equivalent

- 4. a hexadecimal number to a binary equivalent

- 5. a decimal number to a binary equivalent

- 6. a decimal number to a hexadecimal equivalent

Let's explore some techniques for performing these number conversions. These are not the only ways to convert numbers, but they'll get you started.

Binary, decimal, and hexadecimal number systems use positional notation. With positional notation, the value of an individual digit in a number depends upon its position in the number.

For example, in comparing the decimal number 735 and the number 357, the 5 digits have different positions and have different values in the two numbers. In the number 735, the 5 digit has a value of 5; in the number 357, the 5 digit has a value of 50. The position of the 5 in these decimal numbers determines its value.

With positional notation, the position of each digit determines its value. To be more specific, the position of a digit determines the power of the radix by which the digit is multiplied. The radix, or the base, of a number system is the number of digits that can be used to express values. For example, the decimal number system has a radix of ten; there are ten digits, 0 through 9, that can be used to express values. The binary number system has a radix of two since there are only two digits, 0 and 1, that can be used to express values.

The value of an individual digit in a number can be determined by this procedure.

- Start at the position of that digit and count the number of other digits to the *right* of it.

- Use this count as an exponent for the radix of the number.

- Multiply the digit times the radix raised to that exponent.

For example, to determine the value of the digit 3 in the decimal number 6357:

• Start at the position of the 3 digit and count the number of digits to the right of it. There are 2 digits to the right of the 3.

ă

```

1 2

+----->

|

6 3 5 7

```

- Use this count (2) as an exponent for the radix of the number. A decimal number has a radix of 10. The number 10 raised to the 2nd power is 100.

- 2 = 10 X 10 = 100 10

- Multiply the digit (3) times 100.

$3 \times 100 = 300$

The value of the digit 3 in 6357 is 300.

Using the same procedure with 6357, you can determine that the value of the 6 digit is 6 10<sup>9</sup>, or 6000; the value of the 5 digit is 5 10<sup>9</sup>, or 50; and the value of the 7 digit is 7 10<sup>9</sup>, or 7.

#### Note

Any number with a zero exponent equals one. For example,

0=1 10 0=1 53 0=1 18927

The value of a complete number can be calculated by adding the values of the individual digits. For example, the value of the number 6357 is 6000 + 300 + 50 + 7, or 6357.

Knowing how to perform these calculations with decimal numbers helps you calculate the value of numbers that use other number systems.

### 3.3.1 Converting a Binary Number to a Decimal Equivalent

The binary number system is the one used by digital computers. The two digits in the binary number system (0 and 1) are used to represent the on/off or true/false states of binary data in a computer.

The binary number system is the "natural" number system for a computer. The natural number system for people is decimal. When confronted with a binary number, you may want to convert it to decimal so you can think about it more easily.

The binary number system uses positional notation just like the decimal number system. You can take advantage of this common element to convert a binary number to an equivalent decimal value. You can use the same technique to evaluate a binary number as you use to evaluate a decimal number.

For example, suppose you want to convert the binary number 10101 into a decimal equivalent. First, determine the value of each digit in the number. Specifically, you only need to determine the value of each 1 digit since the value of each 0 digit is zero.

In the binary number 10101, the leftmost 1 digit has 4 digits to the right of it.

Use this count (4) as an exponent for the radix of the number. The radix of a binary number is 2. The number 2 raised to the 4th power is 16.

4 = 2 X 2 X 2 X 2 = 16 2

Therefore, the value of the leftmost 1 bit is decimal 16.

The value of the middle 1 bit is 4 and the value of the rightmost 1 bit is 1. The value of the entire binary number is 16 + 4 + 1, or decimal 21.

### 3.3.2 Converting a Hexadecimal Number to a Decimal Equivalent

The hexadecimal number system is a radix-16 number system. There are 16 unique digits in the hexadecimal number system. The 16 hexadecimal digits are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. In the hexadecimal number system, the digits 0 through 9 have the same value as the digits 0 through 9 in the decimal number system. The digits A through F represent the decimal values 10 through 15.