TEXAS INSTRUMENTS

TMS:995 16-Bit Microcomputer

MICROPROCESSOR SERIES

Post Charles in Artist Texas 1911.

Some and actions and

Printed in U.S.A.

CLOCK MISM 5 \$ 32

Preliminary Data Manual

# **ADVANCE INFORMATION**

This document contains information on a new product. Specifications are subject to change without notice.

Copyright © 1981

Texas Instruments Incorporated

Carry Estageards

Allewin Air.

At. #211/11/01/15

CEUBE-71025

# **TABLE OF CONTENTS**

| 1 1 1 3 5 5                            |

|----------------------------------------|

| 1 1 3 5 5                              |

| 1 3 5 5                                |

| 1<br>3<br>5<br>5                       |

| 1<br>3<br>5<br>5                       |

| 3<br>5<br>5                            |

| 5<br>5<br>8                            |

| 5<br>8                                 |

| 8                                      |

|                                        |

| 8                                      |

| 15                                     |

| 20                                     |

| 25                                     |

| 27                                     |

| 21                                     |

| 27                                     |

| 27                                     |

| 31                                     |

| 31                                     |

| 31                                     |

| 32                                     |

| 32                                     |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

| 34                                     |

|                                        |

|                                        |

| 34                                     |

| 34                                     |

| 34                                     |

| 34                                     |

| 34<br>39<br>40<br>41                   |

| 34<br>39<br>40<br>41                   |

| 34<br>39<br>40<br>41<br>42             |

| 34<br>39<br>40<br>41<br>42<br>43       |

| 34<br>39<br>40<br>41<br>42<br>43<br>43 |

| 34 39 40 41 42 43 43 44                |

| 34 39 40 41 42 43 43 44                |

| 34 39 40 41 42 43 43 44 45 45          |

| 34 39 40 41 42 43 43 45 45 46          |

| 34 39 40 41 42 43 43 45 45 46 46       |

| 34 39 40 41 42 43 43 45 45 46 46 46    |

| 34 39 40 41 42 43 43 45 45 46 46 46    |

| 34 39 40 41 42 43 44 45 46 46 46 47 47 |

| 34 39 40 41 42 43 43 45 45 46 46 46    |

|                                        |

# TABLE OF CONTENTS (Concluded)

| 5.               | ELE  | CTRICAL CHARACTERISTICS                                               | 54             |

|------------------|------|-----------------------------------------------------------------------|----------------|

|                  | 5.1  | Absolute Maximum Ratings                                              | 54             |

| ,                | 5.2  | Recommended Operating Conditions                                      | 54             |

|                  | 5.3  | Electrical Characteristics                                            | 54             |

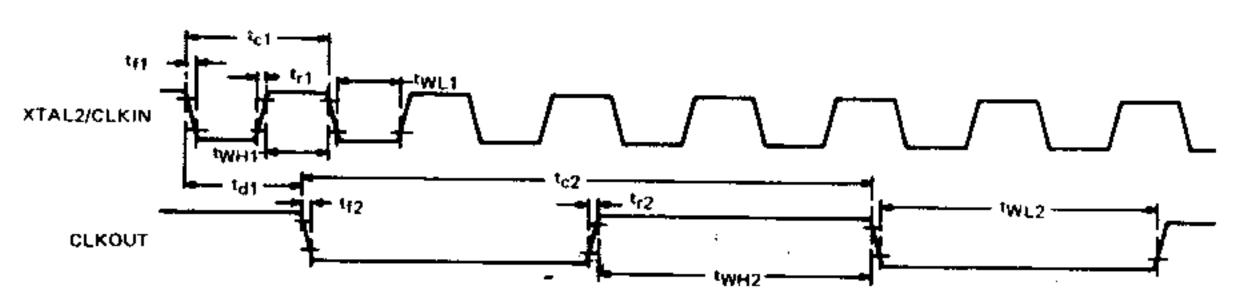

|                  | 5.4  | Clock Characteristics                                                 | 55             |

|                  |      | 5.4.1 Internal Clock Option                                           | 55             |

| <b>\</b>         |      | 5.4.2 External Clock Option                                           | 55             |

|                  | 5.5  | Timing Requirements                                                   | 56             |

|                  | 5.6  | Switching Characteristics                                             | 56             |

| _                |      |                                                                       |                |

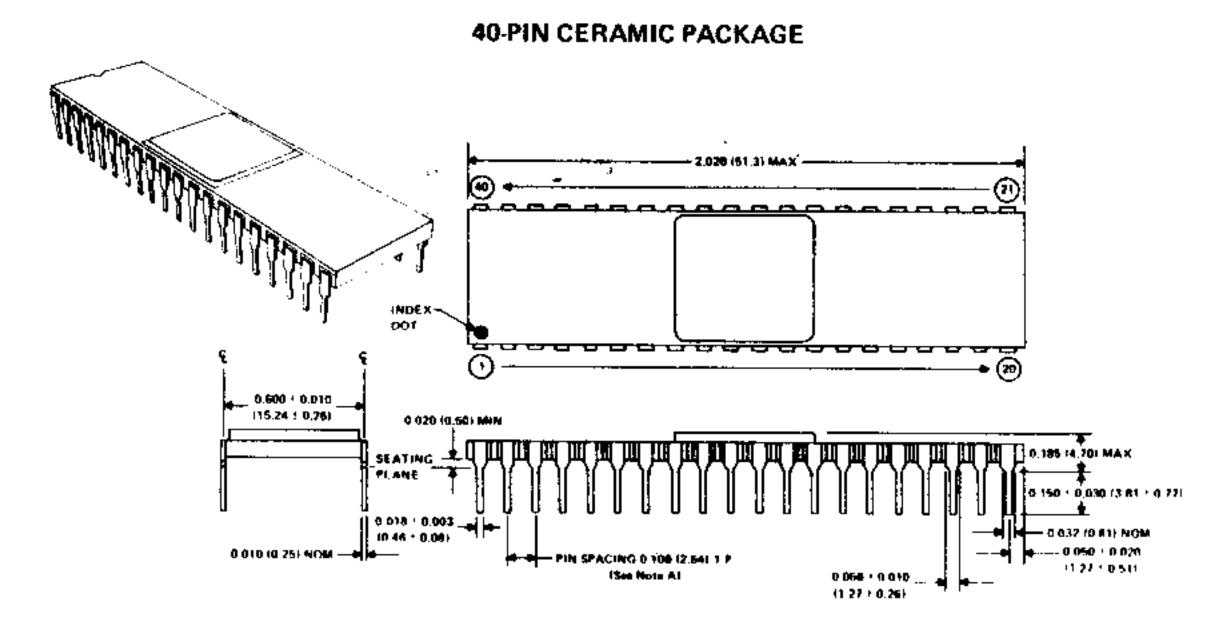

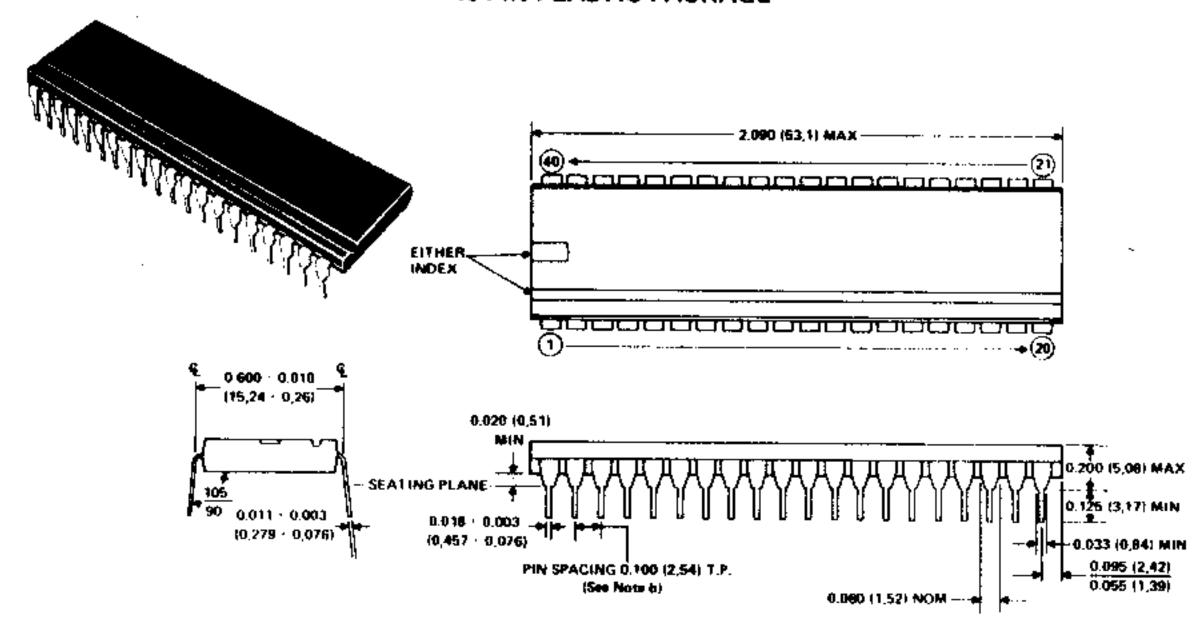

| 6.               | MEC  | CHANICAL SPECIFICATIONS                                               | <b>61</b>      |

|                  |      | LIST OF ILLUSTRATIONS                                                 |                |

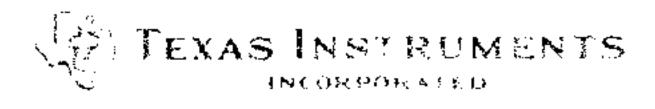

| Figur            | e 1  | Word and Byte Formats                                                 | •              |

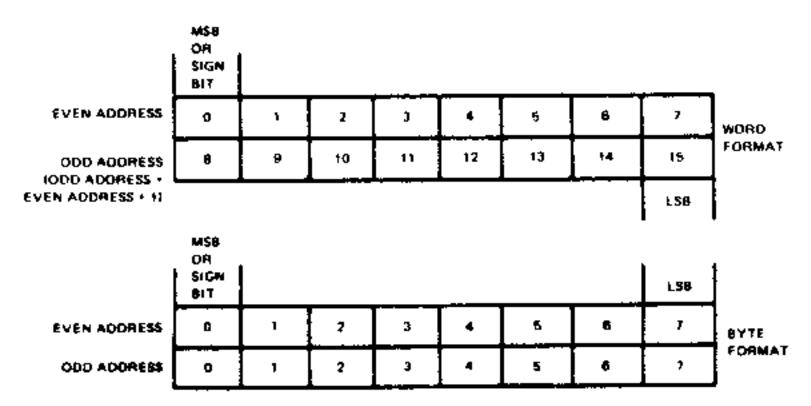

| Figur            |      | TMS 9995 Memory Map                                                   | 2              |

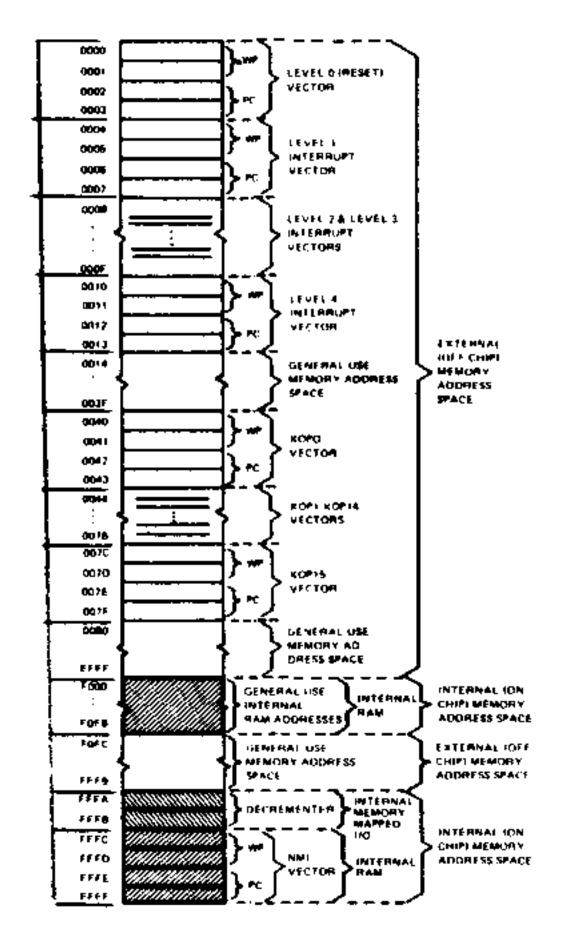

| Figur            |      | TMS 9995 Block Diagram                                                | 2              |

| Figur            |      | TMS 9995 Flow Chart                                                   | 3              |

| Figure           | e 5  | Status Register Bit Assignments                                       | 4              |

| Figure           | e 6  | Workspace Registers Usable As Index Registers                         | 5<br>6         |

| Figur            | e 7  | Workspace Pointer and Registers                                       | 7              |

| Figure           | e 8  | TMS 9995 Memory Interface                                             | ,              |

| Figure           | e 9  | TMS 9995 Memory Read Cycle                                            | 8<br>9         |

| Figure           | e 10 | Memory Write Cycle                                                    | 10             |

| Figure           | e 11 | TMS 9995 Hold State                                                   | 11             |

| Figure           | e 12 | Decrementer Functional Block Diagram                                  | 12             |

| Figure           | e 13 | Wait State Generation for External Memory, External CRU Cycles,       | 12             |

|                  |      | and External Instruction Cycles                                       | 14             |

| Figure           | e 14 | External Circuitry for Invoking/Inhibiting Automatic First Wait State | , ,            |

|                  |      | Generation Feature                                                    | 14             |

| Figure           | e 15 | TMS 9995 Reset Signal Timing Relationships                            | 17             |

| Figure           | e 16 | TMS 9995 NMI Signal Timing Relationships                              | 18             |

| Figur            | e 17 | Functional Block Diagram of Internal Interrupt Request Latch          | 18             |

| Figure           |      | MS 9995 CRU Interface                                                 | 20             |

| Figure           |      | CRU Address Map                                                       | 21             |

| Figure           |      | TMS 9995 CRU Input Cycle                                              | 22             |

| Figure           |      | TMS 9995 CRU Output Cycle                                             | 23             |

| Figure           |      | Single Bit CRU Address Development                                    | 24             |

| Figure           |      | LDCH/STCR Data Transfers                                              | 24             |

| Figure           |      | Pin Assignments                                                       | 27             |

| Figure           |      | Internal Oscillator                                                   | 55             |

| Figure           |      | External Oscillator                                                   | 56             |

| Figure           |      | TMS 9995 Clock Timing                                                 | 57             |

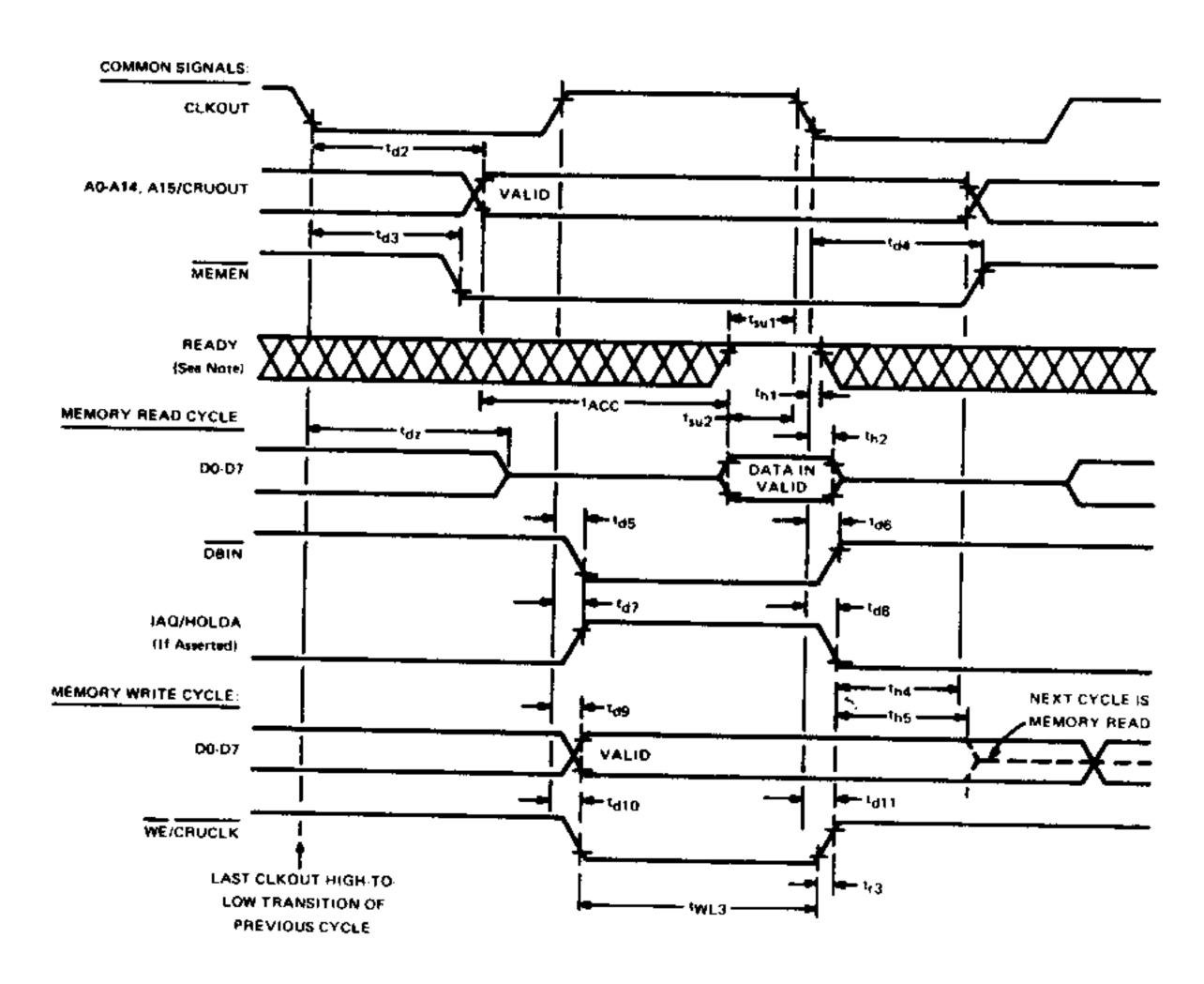

| Figure<br>Figure | _    | TMS 9995 Memory Interface Timing                                      | 57             |

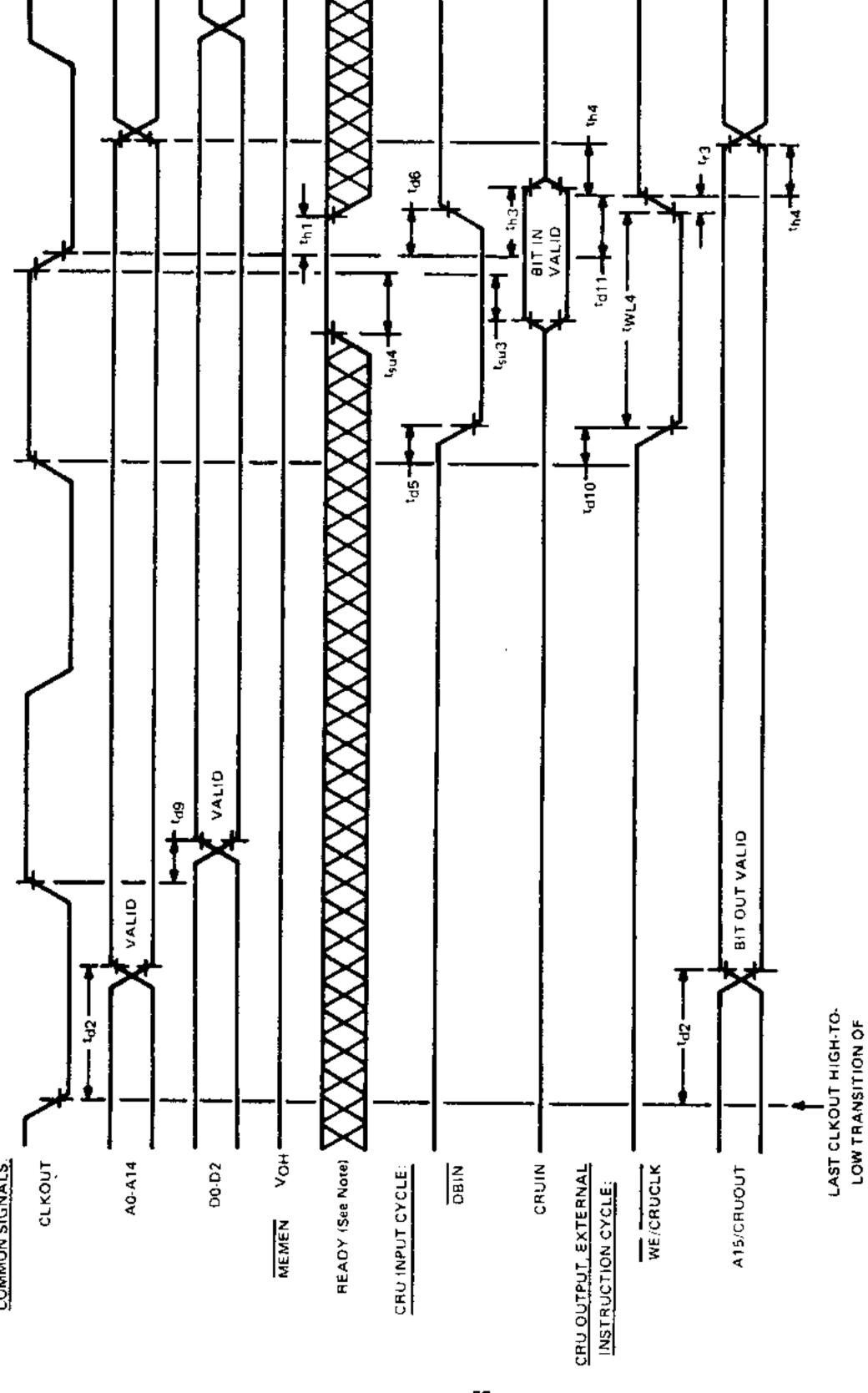

| Figure           |      | TMS 9995 CRU External Instruction Timing                              | 58             |

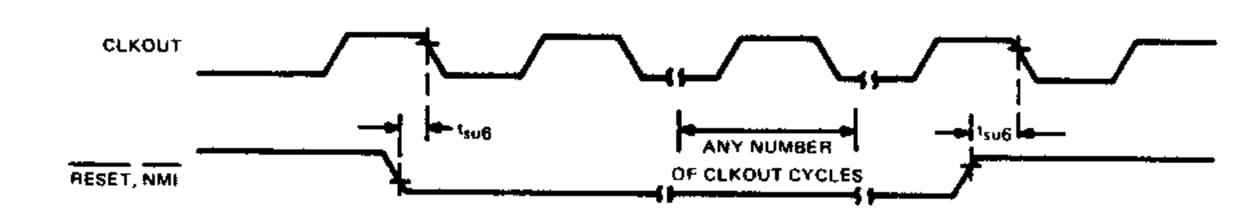

| Figure           |      | TMS 9995 RESET and NMI Timing                                         | 5 <del>9</del> |

| Figure           |      | TMS 9995 HOLD Timing                                                  | 59             |

| Figure           |      | TMS 9995 Interrupt Input Timing                                       | 59             |

| Figure           |      | TMS 9995 Event Counter Input Timing                                   | 59             |

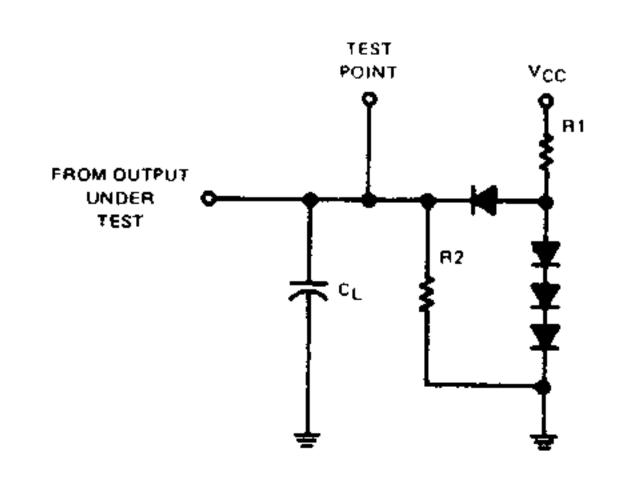

| Figure           |      | Measurement Points for Switching Characteristics                      | 60             |

| · igui e         |      | Switching Characteristics Test Load Circuit                           | 60             |

# LIST OF TABLES

| lable 1   | Dedicated Workspace Registers                                          |

|-----------|------------------------------------------------------------------------|

| Table 2   | Interrupt Level Data                                                   |

| Table 3   | Flag Register Bit Definitions                                          |

| Table 4   | TMS 9995 External Instruction Codes                                    |

| Table 5   | TMS 9995 Pin Description                                               |

| Table 6   | Definition of Terminology                                              |

| Table 7   | Status Register Bit Definitions 36                                     |

| Table 8   | Execution Sequence Example 48                                          |

| Table 9   | Instruction Execution Times 50                                         |

| Table 10  | Operation Address Derivation                                           |

| Table 11  | Operation Address Derivation 52 Instruction Execution Time Examples 53 |

| , 0010 11 | 53                                                                     |

í

•

1.1 DESCRIPTION

1.

The TMS 9995 microcomputer is a single-chip 16-bit central processing unit (CPU) with 256 bytes of on-chip random access memory (RAM). A member of the TMS 9900 family of microprocessor and peripheral circuits, the TMS 9995 is fabricated using N-channel silicon-gate MOS technology. The rich instruction set of the TMS 9995 is based upon a unique memory-to-memory architecture that features multiple register files resident in memory. Memory-resident register files allow faster response to interrupts and increased programming flexibility. The inclusion of RAM, timer function, clock generator, interrupt interface, and a flexible flag register on-chip facilitates support of small system implementations.

All members of the TMS 9900 family of peripheral circuits are compatible with the TMS 9995, Providing a performance upgrade to the TMS 9900 microprocessor, the TMS 9995 instruction set is an opcode-compatible superset of the TMS 9900 processor family.

#### 1.2 KEY FEATURES

16-Bit instruction word

INTRODUCTION

- Memory-to-Memory architecture

- 65,536 byte/32,768 word directly addressable memory address space

- Minicomputer instruction set including signed multiply and divide instructions

- Multiple 16-word register files (Workspaces) residing in memory

- 256 bytes of on-chip RAM

- Separate memory and interrupt bus structures

- 8-Bit memory data bus

- 7 prioritized hardware interrupts

- 16 software interrupts (XOPS)

- Programmed and DMA I/O capability

- Serial I/O via communication register unit (CRU)

- On-chip time/event counter

- On-chip programmable flags (16)

- Macro instruction detection (MID) feature

- Automatic first wait state generation feature

- Single 5-volt supply

- 40-pin package

- N-Channel silicon gate MOS technology

- On-chip clock generator

## 2. ARCHITECTURE

#### 2.1 MEMORY ALLOCATION

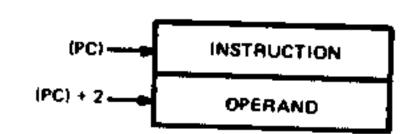

The basic word of the TMS 9995 architecture is 16 bits in length. These 16 bits are divided into 8-bit bytes for external memory in the manner shown in Figure 1. A word is, therefore, defined as two consecutive 8-bit bytes in memory. All words (instruction opcodes, operand addresses, word-length data, etc.) are restricted to even address boundaries, i.e., the most significant half, or 8 bits, resides at an even address and the least significant half resides at the subsequent odd address. Any memory access involving a full word that is directed by software to utilize an odd address will result in the word starting with this odd address minus one to be accessed.

FIGURE 1 - WORD AND BYTE FORMATS

The instruction set of the TMS 9995 allows both word and byte operations, Byte instructions may address either byte as necessary. A byte access of this type will not affect the other byte of the word involved since the other byte will not be accessed during the execution of the byte instruction.

The TMS 9995 memory map is shown in Figure 2. Shown are the locations in the memory address space for the Reset, NMI, other interrupt and XOP trap vectors, and the dedicated address segments for the on-chip RAM and the on-chip memory-mapped I/O.

NOTE: Addresses are byte addresses in hex

FIGURE 2 - TMS9995 MEMORY MAP

#### 2.2 TMS 9995 ORGANIZATION

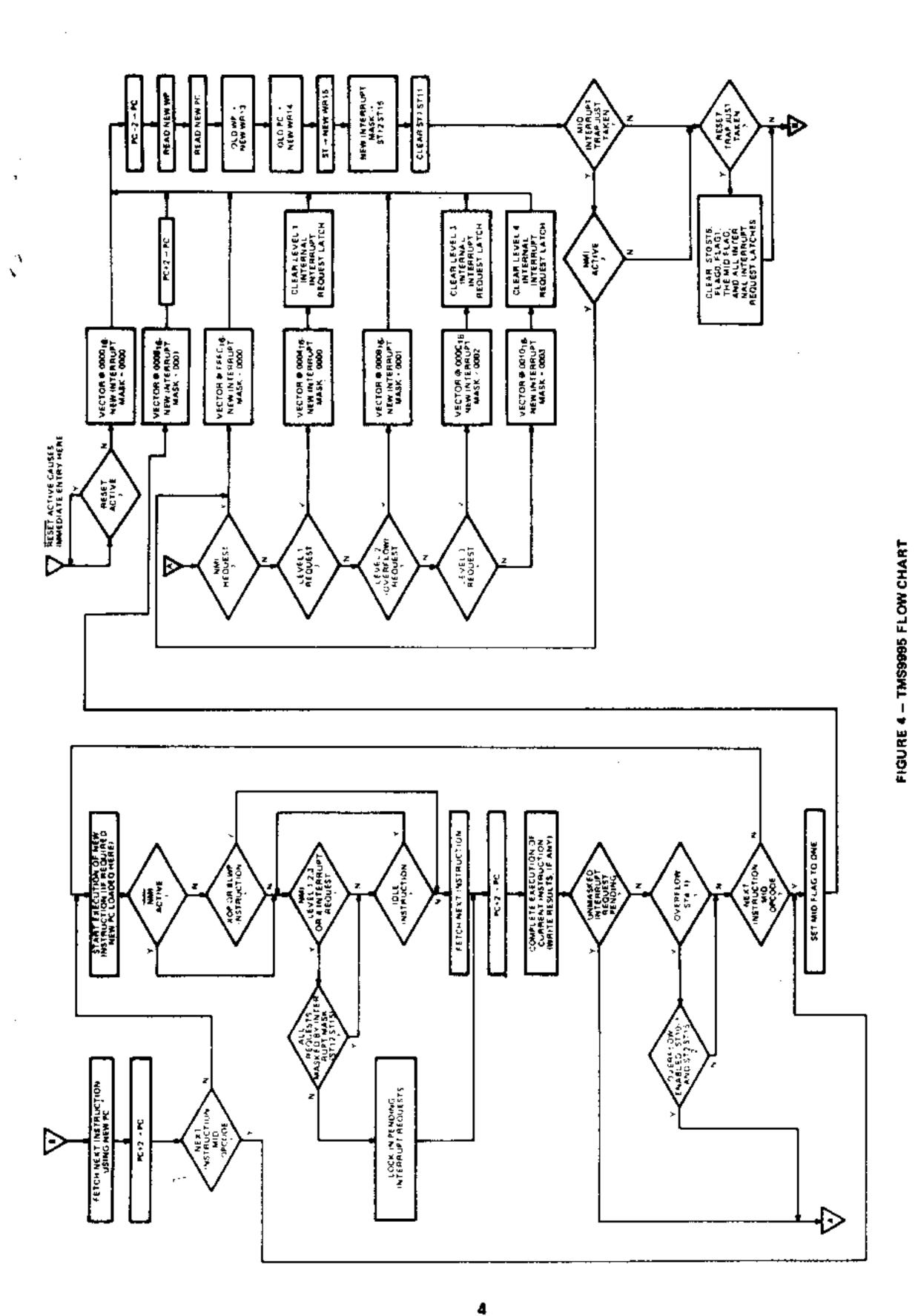

The block diagram of the TMS 9995 is shown in Figure 3. A flow chart, representative of the TMS 9995 functional operation, is shown in Figure 4.

FIGURE 3 -- TMS9996 BLOCK DIAGRAM

2,2.1 Arithmetic Logic Unit

> The arithmetic logic unit (ALU) is the computational component of the TMS 9995. It performs all arithmetic and logic functions required to execute instructions. The functions include addition, subtraction, AND, OR, exclusive OR, and complement. A separate comparison circuit performs the logic and arithmetic comparisons to control bits O through 2 of the status register. The ALU is arranged in two 8-bit halves to accommodate byte operations, Each half of the ALU operates on one byte of the operand. During word operand operations, both halves of the ALU function in conjunction with each other. However, during byte operand processing, results from the least significant half of the ALU are ignored. The most-significant half of the ALU performs all operations on byte operands so that the status circuitry used in word operations is also used in byte operations.

Internal Registers

#### 2.2.2

The following three (3) internal registers are accessible to the user (programmer):

Program Counter (PC)

Status Register (ST)

Workspace Pointer (WP)

#### Program Counter 2,2,2,1

The program counter (PC) is a 15-bit counter that contains the word address of the next instruction following the instruction currently executing. The microprocessor references this address to fetch the next instruction from memory and increments the address in the PC when the new instruction is executing. If the current instruction in the microprocessor alters the contents of PC, then a program branch occurs to the location specified by the altered contents of PC. All context switching (see Section 2.2.2.3.2) operations plus simple branch and jump instructions affect the contents of PC.

#### 2.2.2.2 Status Register

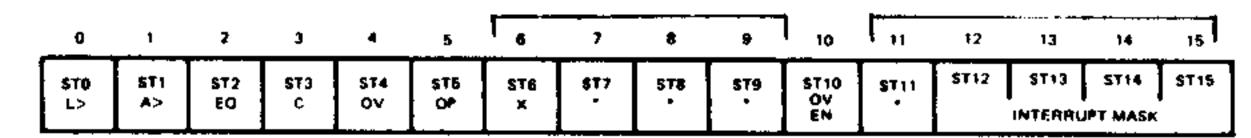

The status register (ST) is a fully implemented 16-bit register that reports the results of program comparisons, indicates program status conditions, and supplies the arithmetic overflow enable and interrupt mask level to the interrupt priority circuits. Each bit position in the register signifies a particular function or condition that exists in the microprocessor. Figure 5 illustrates the bit position assignments. Some instructions use the status register to check for a prerequisite condition; others affect the values of the bits in the register; and others load the entire status register with a new set of parameters. Interrupts also modify the status register. The description of the instruction set later in this document details the effect of each instruction on the status register (see Section 3),

\*NOTE: ST7, ST8, ST9, and ST11 are not used in the TMS9995, but still physically exist in the register. These bits could therefore be used as flag bits, but softwers transportability should be kept in mind when doing so as these bits are defined in other 9900 microprocessor family and 990 minicomputer family products.

Logical Greater Than Cerry Out : XOP in Progress Arithmetic Greater Than Overflow Overflow interrupt Enable

FIGURE 5 -- STATUS REGISTER BIT ASSIGNMENTS

Parity (Odd No. of Bits)

## 2,2.2.3 Workspace

Equal/TB Indicator

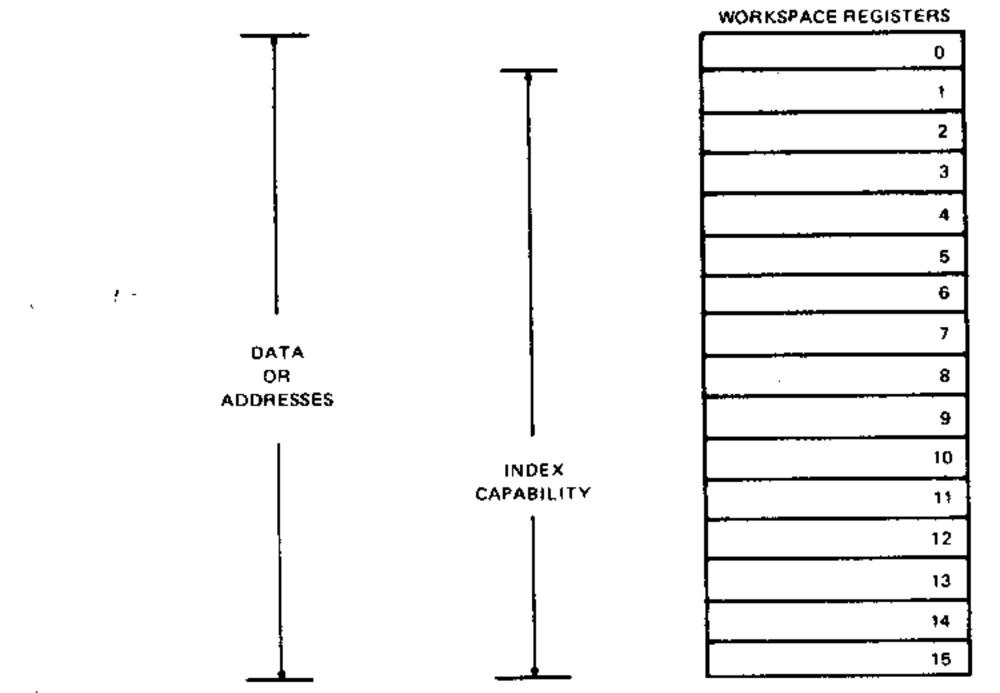

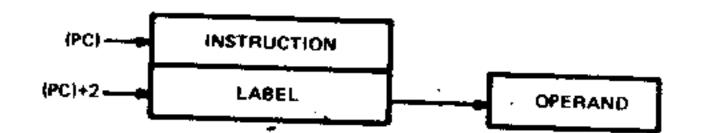

The TMS 9995 uses blocks of memory words called workspaces for instruction operand manipulation. A workspace occupies 16 contiguous words in any part of memory that is not reserved for other use. The individual workspace registers may contain data or address? of function as operand registers, accumulators, address registers, or index registers. Some workspace registers take on special significance during execution of certain instructions. Table 1 lists each of these dedicated workspace registers and the instructions that use them. Figure 6 defines the workspace registers that are allowed to be used as index registers.

TABLE 1 - DEDICATED WORKSPACE REGISTERS

| REGISTER NO. | CONTENTS                       | USED DURING                                        |

|--------------|--------------------------------|----------------------------------------------------|

| 0            | Shift count (optional)         | Shift instructions (SLA, SRA, SRC, and SLC)        |

|              | Multiplicand and MSW of result | Signed Multiply                                    |

|              | MSW of dividend and quotient   | Signed Divide                                      |

| 1            | LSW of result                  | Signed Multiply                                    |

|              | LSW of dividend and remainder  | Signed Divide                                      |

| 11           | Return Address                 | Branch and Link Instruction (BL)                   |

|              | Effective Address              | Extended Operation (XOP)                           |

| 12           | CRU Base Aridress              | CRU instructions (SBO, SBZ, TB,<br>LDCR, and STCR) |

| 13           | Saved WP register              | Context switching (BLWP, ATWP, XQP, interrupts)    |

| 14           | Saved PC register              | Context switching (BLWP, RTWP, XOP, interrupts)    |

| 15           | Saved ST register              | Context switching (BLWP, RTWP, XOP, interrupts)    |

NOTE: The WP register contains the address of workspace register zero.

FIGURE 6 - WORKSPACE REGISTERS USABLE AS INDEX REGISTERS

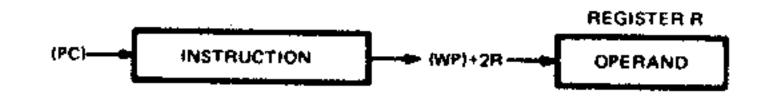

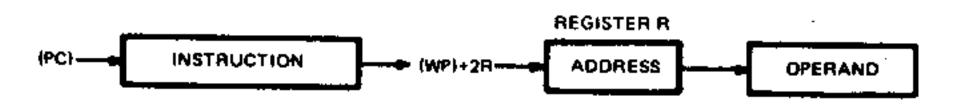

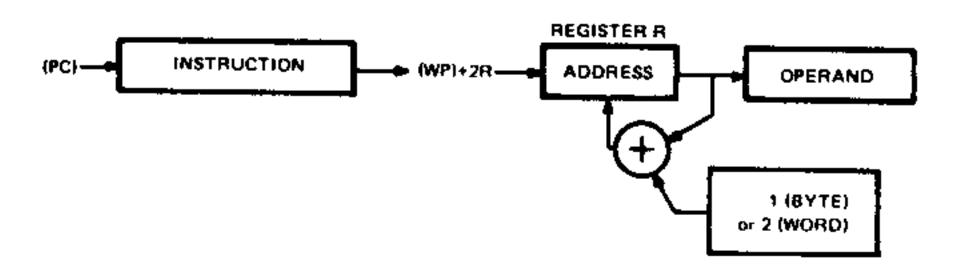

2.2.2.3.1 Workspace Pointer

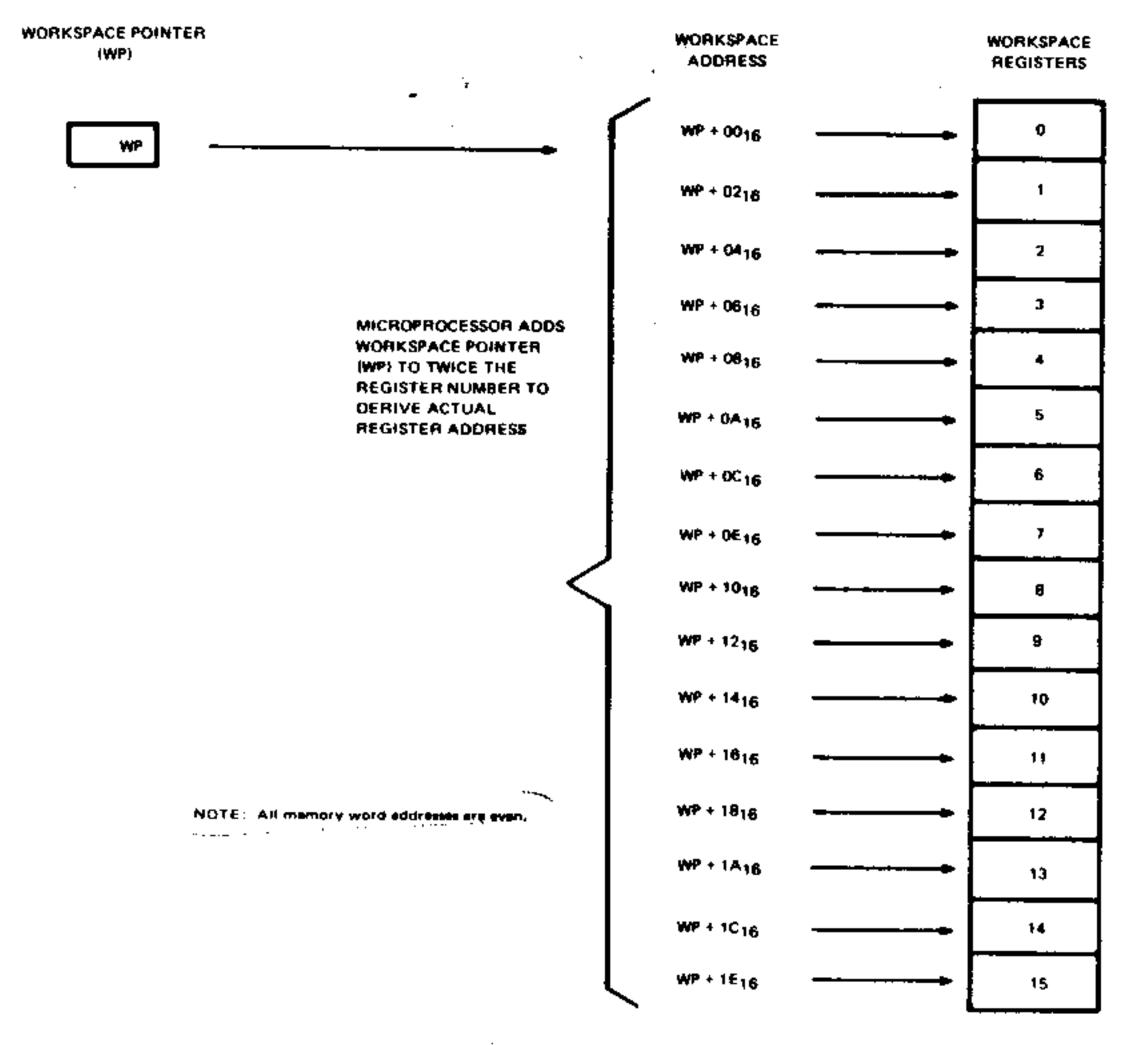

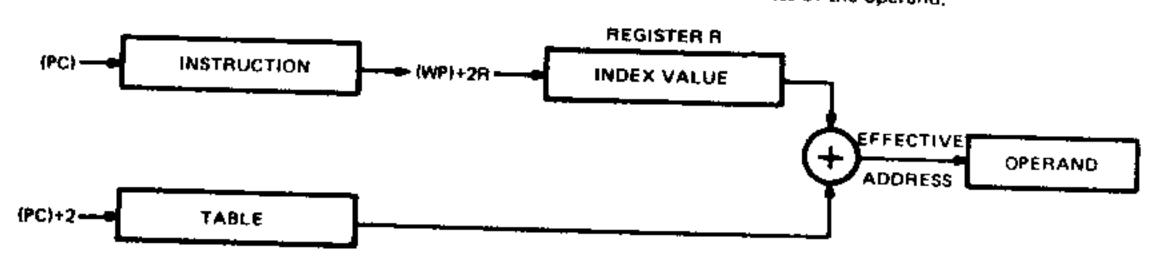

To locate the workspace in memory, a hardware register called the workspace pointer (WP) is used. The workspace pointer is a 16-bit register that contains the memory address of the first word in the workspace. The address is left-justified with the 16th bit (LSB) hardwired to logic zero. The TMS 9995 accesses each register in the workspace by adding twice the register number to the contents of the workspace pointer and initiating a memory request for that word. Figure 7 illustrates the relationship between the workspace pointer and its corresponding workspace in memory

FIGURE 7 - WORKSPACE POINTER AND REGISTERS

For instructions performing byte operations, use of the workspace register addressing mode (see Section 3.2) will result in the most significant byte of the workspace register involved to be used as the operand for the operation. Since the workspace is also addressable as a memory address, the least significant byte may be directly addressed using any one of the general memory addressing modes.

## 2.2.2.3.2 Context Switching

The workspace concept is particularly valuable during operations that require a context switch, which is a change from one program environment to another, as in the case of a subroutine or an interrupt service routine. Such an operation using a conventional multi-register arrangement requires that at least part of the contents of the register

file be stored and reloaded using a memory cycle to store or fetch each word. The TMS 9995 accomplishes this operation by changing the workspace pointer. A context switch requires only three store cycles and two fetch cycles, exchanging the program counter, status register and workspace pointer. After the switch, the workspace pointer contains the starting address of a new 16-word workspace in memory for use in the new routine. A corresponding time saving occurs when the original context is restored. Instructions in the TMS 9995 that result in a context switch include: Call subroutine (BLWP), Return from Subroutine (RTWP) and the Extended Operation (XOP) instruction. All interrupts also cause a context switch by forcing the TMS 9995 to trap to a service subroutine.

## , Y 2.3 TMS 9995 INTERFACES

Each TMS 9995 system interface uses one or more of the signals from one or more of the signal groupings given in the pin description list in Section 3. Each interface is described in detail in the following paragraphs.

#### 2.3.1 TMS 9995 Memory Interface

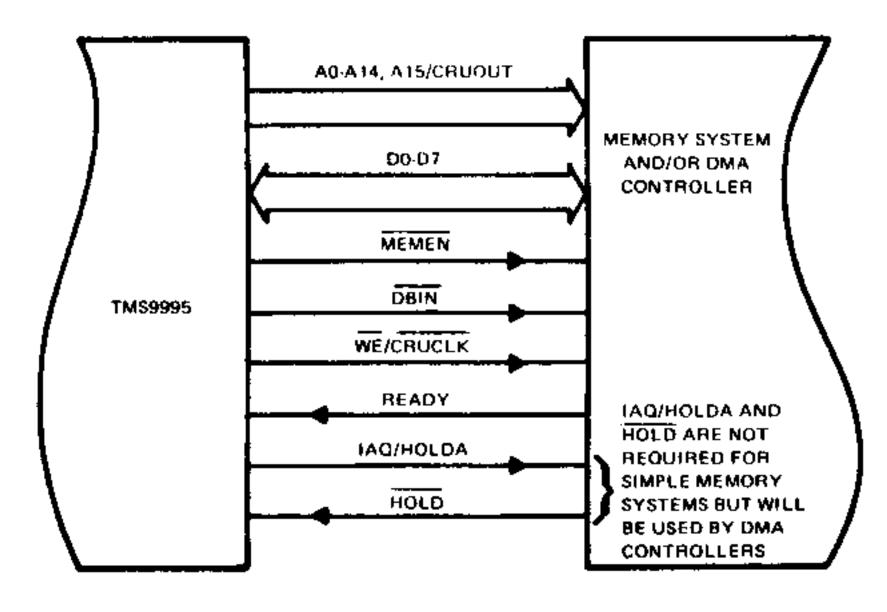

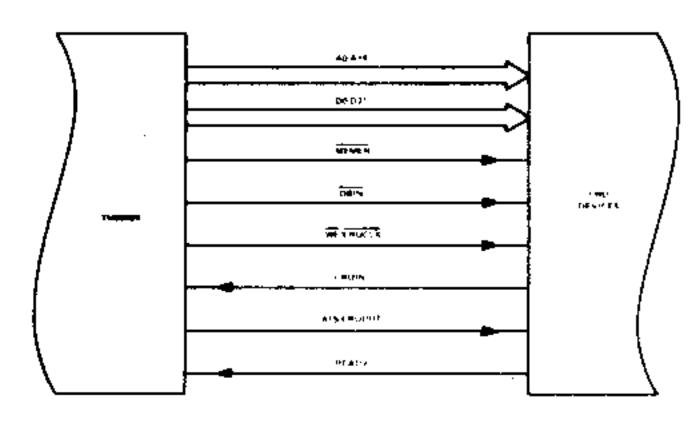

The signals used in the TMS 9995 interface to system memory are shown in Figure 8.

FIGURE 8 - TMS9995 MEMORY INTERFACE

#### 2.3.1.1 External Memory Address Space

The details of memory accesses that are external to the TMS 9995 (off-chip accesses) are given in the following paragraphs. (See Figure 2 for the addresses that are in the external memory-address space.)

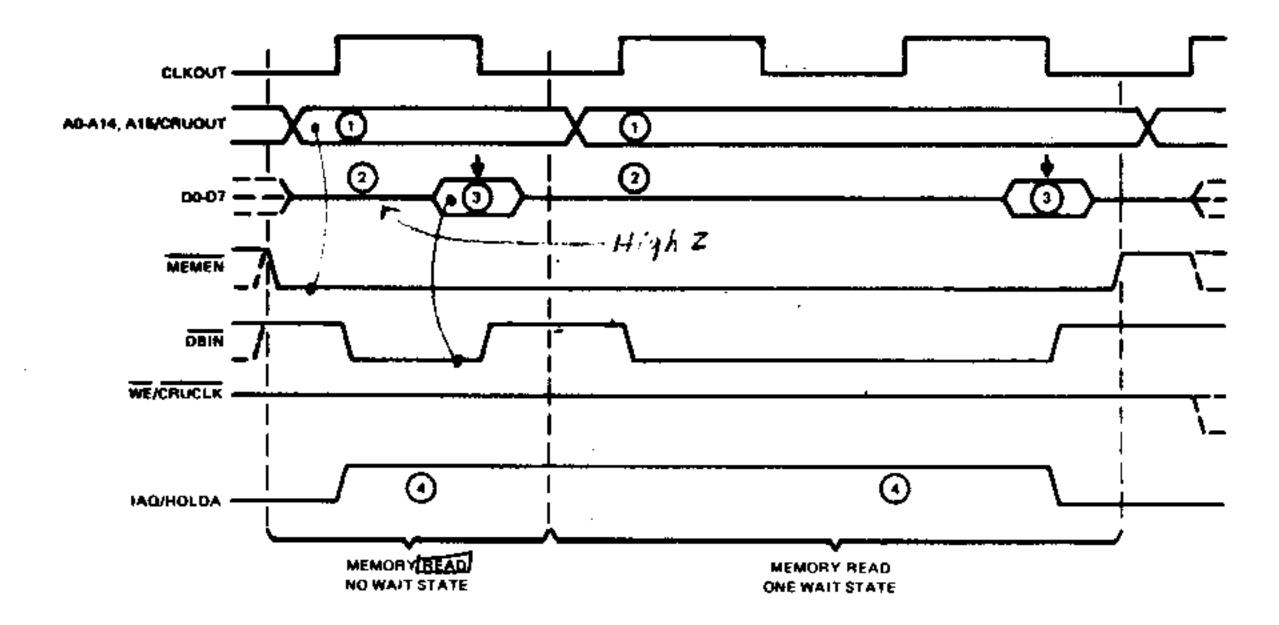

# 2.3.1.1.1 Memory Read Operations

To perform a memory read operation, the TMS 9995 first outputs the appropriate address on A0-A14 and A15/CRUOUT, and asserts MEMEN. The TMS 9995 then places its data bus drivers in the high impedance state, asserts DBIN, and then reads in the data byte. Completion of the memory read cycle and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.1.3. Timing relationships of the memory read sequence are shown in Figure 9. Note that MEMEN remains active (low) between consecutive memory operations.

NOTES:

- (1) Valid address

- 2) In input mode (drivers # High-Z)

- (3) Memory Read Date must be valid at CLKOUT edge indicated.

- (4) IAQ/HOLDA will only be asserted during memory read cycles if an instruction opcode is being read (timing shown is for an instruction fetch from external memory —, i.e., two consecutive byte reads).

# FIGURE 9 - TMS8995 MEMORY READ CYCLE

Although not explicitly shown in Figure 9, reading a word (two 8-bit bytes) from external memory requires two memory read cycles that occur back-to-back (a Hold state request will not be granted between cycles). If an instruction directs that a byte read from external memory is to be performed, only the byte specifically addressed will be read (one memory read cycle). External words are accessed most-significant (even) byte first, followed by the least-significant (odd) byte.

During memory read cycles in which an instruction opcode is being read, IAQ/HOLDA is asserted as shown in Figure 9. Note that since an instruction opcode is a word in length, IAQ/HOLDA remains asserted between the two byte read operations involved when an instruction opcode is read from the external memory address space.

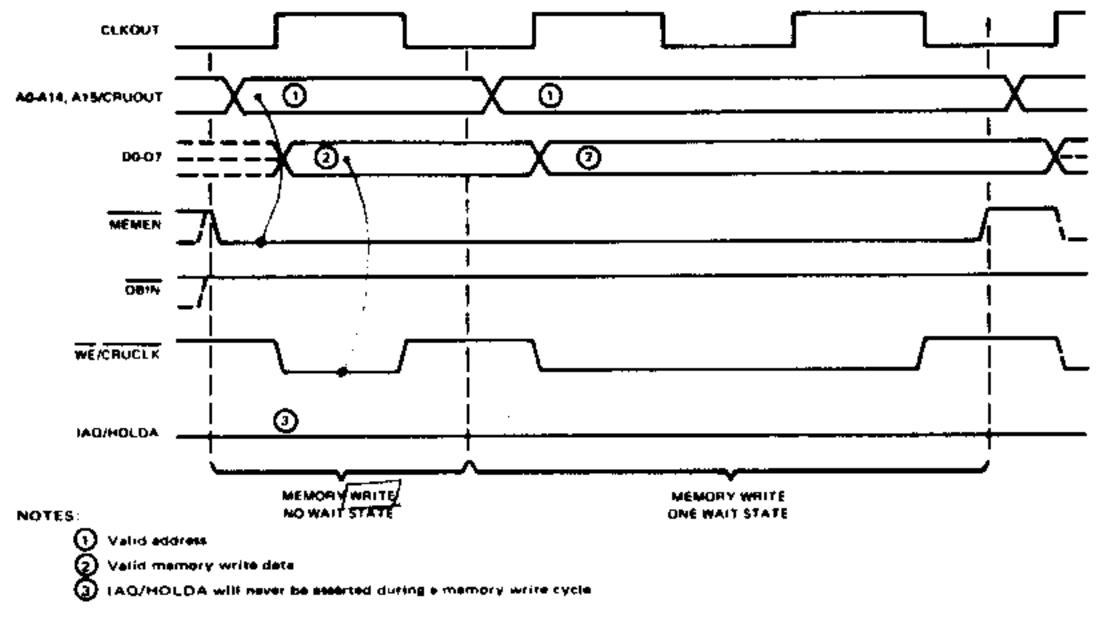

# 2,3,1,1,2 Memory Write Operations

To perform a memory write operation, the TMS 9995 first outputs the appropriate address on A0-A14 and A15/CRUOUT, and asserts MEMEN. The TMS 9995 then outputs the data byte being written to memory on pins D0 through D7, and then asserts WE/CRUCLK. Completion of the memory write cycle and/or generation of Wait states is determined by the Ready input as detailed in Section 2.3.1.3. Timing relationships of the memory write sequence are shown in Figure 10. Note that MEMEN remains active (low) between consecutive memory operations.

FIGURE 10 - TMS9995 MEMORY WRITE CYCLE

Writing a word (two 8-bit bytes) to external memory requires two memory write cycles that occur back-to-back. (A Hold state request will not be granted between cycles.) If an instruction directs that a byte write to external memory is to be performed, only the byte specifically addressed will be written (one memory write cycle). External words are accessed most-significant (even) byte first followed by the least-significant (odd) byte,

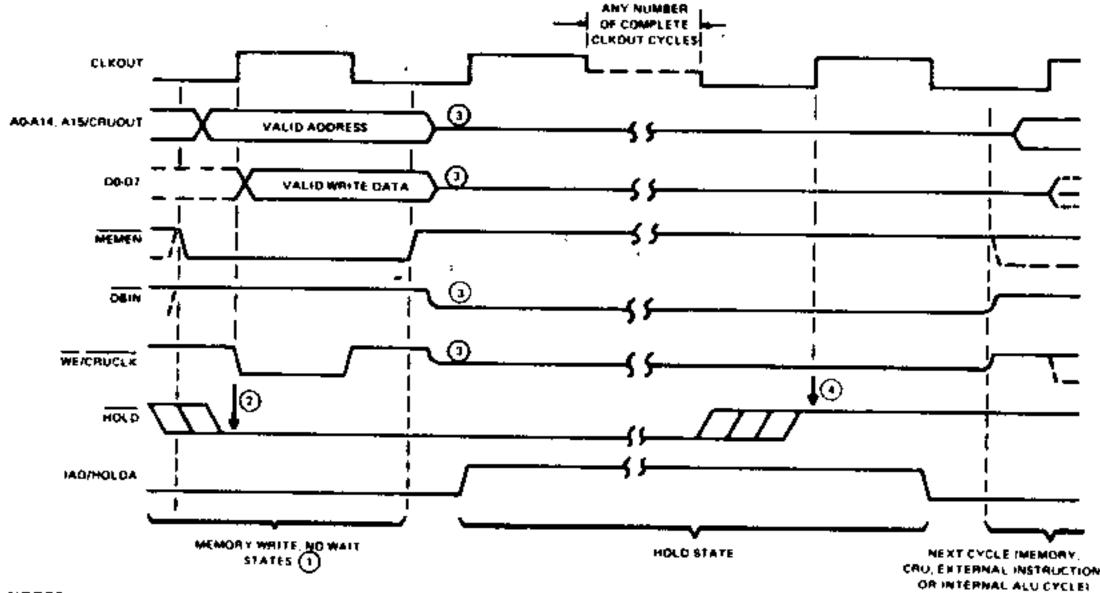

## 1.3 Direct Memory Access

The TMS 9995 Hold state allows both external devices and the TMS 9995 to share a common external memory. To gain direct memory access (DMA) to the common memory, the external device first requests the TMS 9995 to enter a Hold state by asserting (taking low) the HOLD input. The TMS 9995 will then enter a Hold state following completion of the cycle (either memory, CRU, external Instruction, or internal ALU cycles) that it is currently performing. Note, however, that a Hold state is not entered between the first and second byte accesses of a full word in the external memory address space, and a Hold state is not entered between the first and second clock cycles of a CRU cycle.

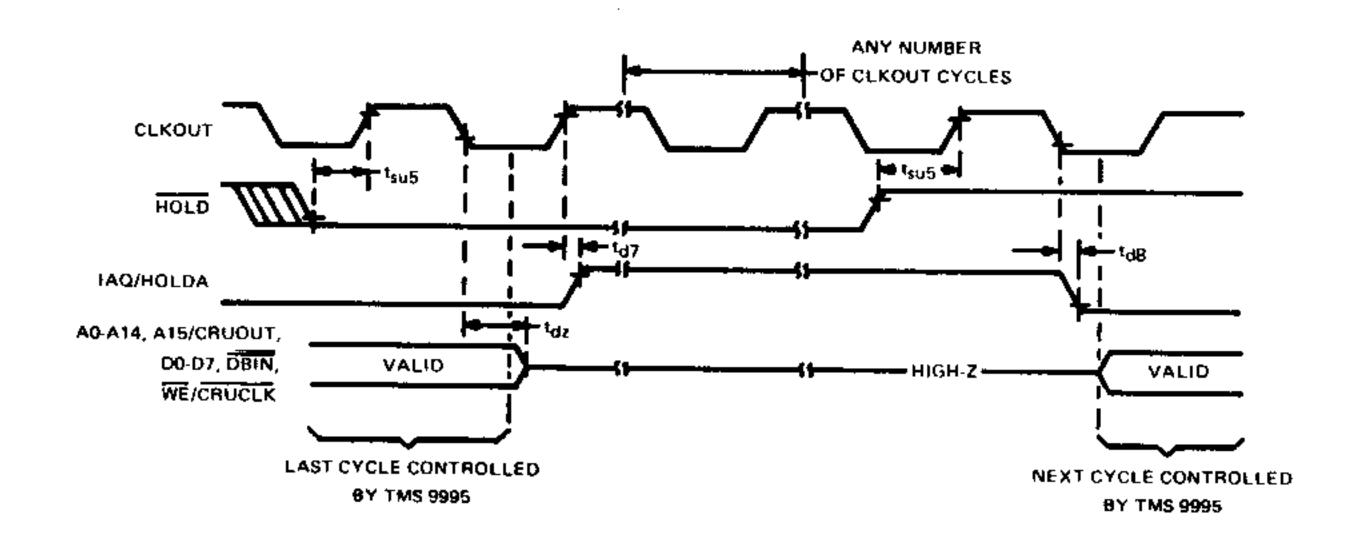

Upon entry of a Hold state, the TMS 9995 puts its address, data, DBIN, and WE/CRUCLK drivers in the high impedance mode, and asserts IAQ/HOLDA. The external device can then utilize these signal lines to communicate with the common memory. After the external device has completed its memory transactions, it releases HOLD, and the TMS 9995 continues instruction execution at the point where it had been suspended. Timing relationships for this sequence are shown in Figure 11.

NOTES:

- (1) Cycle before the hold state could have been memory (with any number of wait states), CRU, external instruction, or insernal ALU

- (3) In high impedance mode fourput drivers)

- Next cycle will begin after first low to high CLKOUT transition at which HOLD is high

FIGURE 11 - TM\$9995 HOLD STATE

To allow DMA loading of external memory on power-up, the TMS 9995 does not begin instruction execution after a Reset state until HOLD has been removed if HOLD was active (low) at the time RESET was taken from low to high RESET released).

External devices cannot access the internal (on-chip) memory address space of the TMS 9995 when it is in the Hold state.

Since IAQ (Instruction Opcode Acquisition) and HOLDA (Hold Acknowledge) are multiplexed on a single signal, IAQ/HOLDA, this signal must be gated with MEMEN using external logic to separate IAQ and HOLDA. When MEMEN = 0, IAQ/HOLDA can indicate IAQ, and when MEMEN = 1, IAQ/HOLDA can indicate HOLDA.

#### 2.3.1.2 Internal Memory Address Space

Access of the internal (on-chip) memory address space is transparent to the TMS 9995 instruction set. That is, operands can be read from and written into locations in the internal memory space simply by using the appropriate addresses via any of the addressing modes in the TMS 9995 instruction set, and instructions can even be executed from the internal memory space by loading the appropriate address into the program counter of the TMS 9995.

10

The TMS 9995 indicates to the external world when these internal memory address space accesses are occurring by asserting the same signals used for accessing external memory (see Figure 8) in a manner very similar to an external memory address space access. There are a few differences in these cycles, however, and these differences are detailed in the following paragraphs.

When performing an internal memory address space access, the TMS 9995 outputs the same signals that it would for an external memory space access, with the same timing (see Figures 9 and 10) except for the following:

- (1) A single cycle (read or write) is output as both internal bytes are accessed simultaneously. (Externally, it appears as though a single byte memory access cycle to an internal address is occurring.)

- The cycle always has no Wait states, and the READY input is ignored by the TMS 9995 (see Section 2.3.2.3).

- During read cycles, the data bus (D0-D7) output drivers are put in the high-impedance mode. During write cycles, the data bus outputs non-specific data.

During read cycles to the internal memory address space, the TMS 9995 does not make the read data available to the external world. If an instruction is executed from the internal memory address space, IAQ/HOLDA is still asserted, but only during the one read cycle shown externally while the full word is read internally.

When in a Hold state, external devices are not able to access the internal memory address space.

#### 2.3.1.2.1 Internal RAM

The 256 bytes of internal random-access read/write memory (RAM), the memory addresses of which are shown in Figure 2, are organized internally as 128 16-bit words. Since the TMS 9995 has 16-bit internal data paths, two 8-bit bytes are accessed each time a memory access is made to the internal RAM.

Byte accesses are transparent to the internal RAM. That is, when an instruction addresses a byte in the internal RAM, the TMS 9995 will: (1) read the entire word but only use the byte specifically addressed for a read operation and, (2) only write to the specifically addressed byte and not alter the contents of the other byte in the word during a write operation.

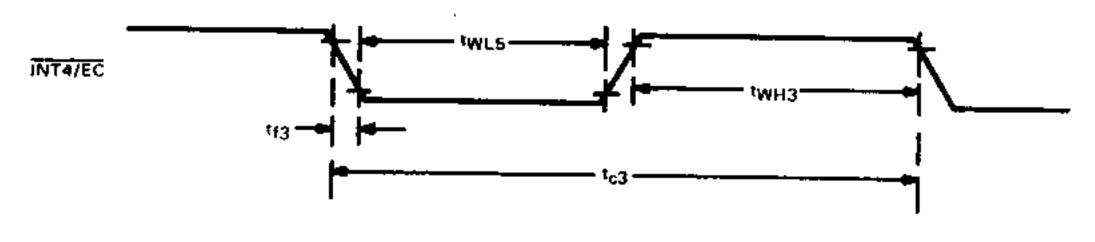

#### 2.3.1.2.2 Decrementer (Timer/Event Counter)

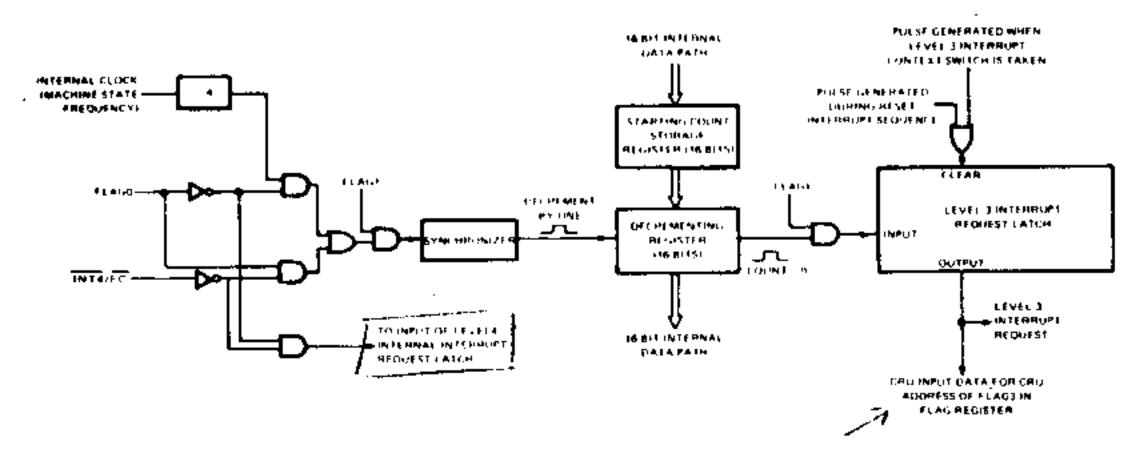

Accessible via one of the word addresses (see Figure 2) of the internal memory-mapped I/O address space is the decrementer. The on-chip decrementer logic can function as a programmable real-time clock, an event timer, or as an external event counter. A block diagram of the decrementer that is representative of its functional operation (but not necessarily representative of its specific logic implementation) is shown in Figure 12.

NOTE: FLAGO and FLAGE are bits in the Flag Register

FIGURE 12 - DECREMENTER FUNCTIONAL BLOCK DIAGRAM

The decrementer is enabled/disabled using bit FLAG1 of the internal Flag register. (See Section 2.3.3.2.1 for details of the Flag register and accessing the bits in it.) When FLAG0 is set to zero, the decrementer will function as a timer. When FLAG0 is set to one, the decrementer will function as a timer. When FLAG0 is set to one, the decrementer will function as an event counter. When FLAG1 is set to zero, the decrementer is disabled and will not be allowed to decrement and request level 3 interrupt traps. When FLAG1 is set to one, the decrementer is enabled and will decrement and request level 3 interrupt traps. It should be noted that when the decrementer is configured as a timer, INT4/EC will be usable as an external interrupt level 4 trap request. When the decrementer is configured as an event counter, INT4/EC is the input for the "event counter" pulses, and an interrupt level 4 trap request input is no longer available externally or internally.

The general operation of the decrementer is as follows. FLAGO of the Flag register is first set to select the desired mode of operation. The desired start count is then loaded into the Starting Count Storage Register by performing a memory write of the count word to the dedicated internal memory mapped I/O address of the decrementer. (This also loads the Decrementing Register with the same count.) The decrementer is then enabled and allowed to start decrementing by setting FLAG1 of the Flag Register to one. (Both FLAG0 and FLAG1 are set to zero when the TMS 9995 is reset. (See Section 2.3.2.1.1.) When the count in the Decrementing Register reaches zero, the level 3 internal interrupt request latch is set (see Section 2.3.2.2.3), the Decrementing Register is reloaded from the Starting Count Storage Register, and decrementing continues. Note that writing a start count of 000016 to the decrementer will disable it.

When configured as a timer, the decrementer functions as a programmable real-time clock by decreasing the count in the Decrementing Register by one for each fourth CLKOUT cycle. Loading the decrementer with the appropriate start count causes an interrupt to be requested every time the count in the Decrementing Register reaches zero. The decrementer can also be used as an event timer when configured as a timer by reading the decrementer (which is accomplished by performing a memory read from the dedicated internal memory mapped I/O address of the decrementer) at the start and stop points of the event of interest and comparing the two values. The difference will be a measurement of the elapsed time.

When configured as an event counter, operation is as previously discussed except that each high-to-low transition on INT4/EC will cause the Decrementing Register to decrement. These INT4/EC high-to-low transitions can be asynchronous with respect to CLKOUT. Note that INT4/EC can function as a negative edge-triggered interrupt by loading a start count of one.

The decrementer should always be accessed as a full word (two 8-bit bytes). Reading a byte from the decrementer does not present a problem since only the byte specifically addressed will be read. Writing a single byte to either of the bytes of the decrementer will result in the data byte being written into the byte specifically addressed and random bits being written into the other byte of the decrementer.

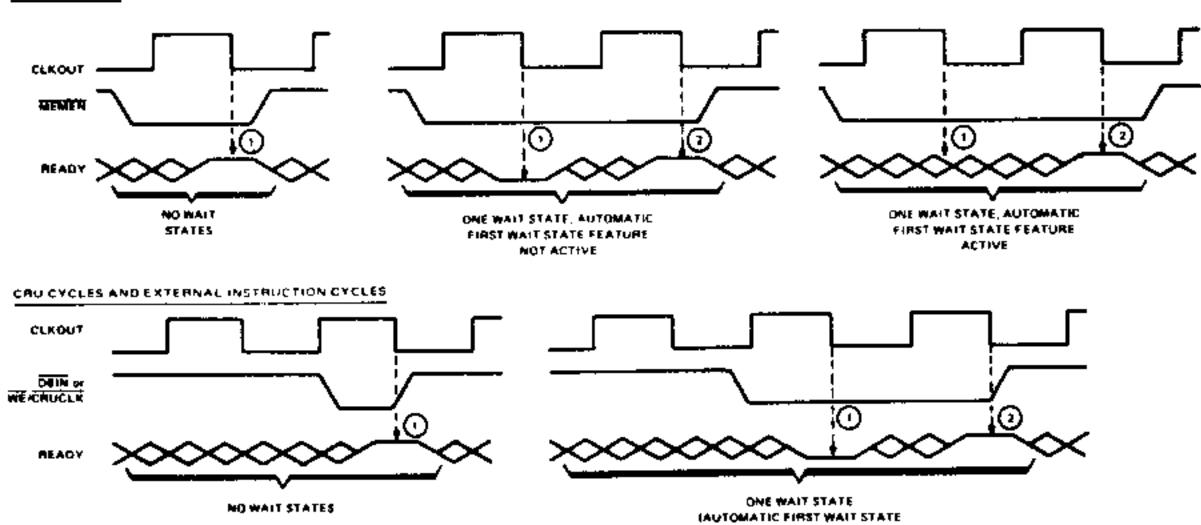

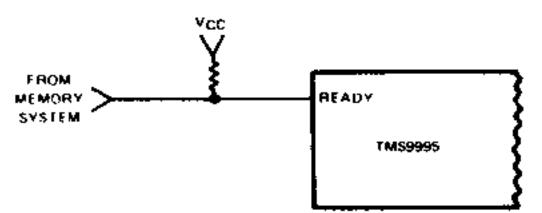

#### 2.3.1.3 Wait State Generation

Wait states can be generated for external memory cycles, external CRU cycles and external instruction cycles for the TMS 9995 using the READY input. A Wait state is defined as extension of the present cycle by one CLKOUT cycle. The timing relationships of the READY input to the memory interface and the CRU interface signals are shown in Figure 13. Note that Wait states cannot be generated for memory cycles that access the internal memory address space or for CRU cycles that access the internal CRU address space, as the READY input will be ignored during these cycles.

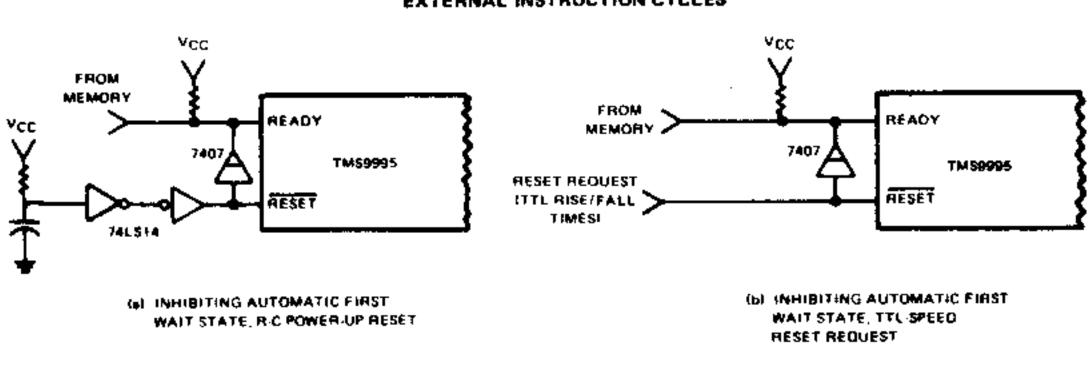

The Automatic First Wait State Generation feature of the TMS 9995 allows a Wait state to be inserted in each external memory cycle, regardless of the READY input, as shown in Figure 13. The Automatic First Wait State Generation feature can be invoked when RESET is asserted. If READY is active (high) when RESET goes through a low-to-high transition, the first Wait state in each external memory cycle will be automatically generated. If READY is inactive (low) when RESET goes through a low-to-high transition, no Wait state will be inserted automatically in each external memory cycle. There is a one and one-half CLKOUT cycle time minimum setup time requirement on READY before the RESET low-to-high transition. The recommended external circuitry for invoking or inhibiting the Automatic First Wait State Generation feature is shown in Figure 14. Note that this feature does not apply to internal memory address space accesses, external instruction cycles, or any CRU cycles. Wait states cannot be generated during internal ALU/other operation cycles. The READY input is ignored during these cycles.

#### **WEMORY CYCLES**

#### NOTES:

- First sample time of READY in cycle

- 2 Second sample time of READY in cycle. Additional wait states can be generated by keeping READY low at this and subsequent sample times.

TO CRU CYCLES!

XXXX denotes "don't care"

# FIGURE 13 – WAIT STATE GENERATION FOR EXTERNAL MEMORY, EXTERNAL CRU CYCLES, AND EXTERNAL INSTRUCTION CYCLES

(c) INVOKING AUTOMATIC FIRST WAIT STATE (RESET CAN BE RIC POWER-UP OR OTHER-

FIGURE 14 – EXTERNAL CIRCUITRY FOR INVOKING/INHIBITING

AUTOMATIC FIRST WAIT STATE GENERATION FEATURE

#### 2.3.2 TMS 9996 Interrupts

The TMS 9995 implements seven prioritized, vectored interrupts, some of which are dedicated to predefined functions and the remaining are user-definable. Table 2 defines the source (internal or external), assignment, priority level, trap vector location in memory, and enabling/resulting status register interrupt mask values for each interrupt.

TABLE 2 -- INTERRUPT LEVEL DATA

| PRIORITY  LEVELS  (In Order of Priority) | LEVELS (Memory |                                                      | MASK VALUE AFTER TAKING THE INTERRUPT (ST12 THRU ST15) | SOURCE AND<br>ASSIGNMENT                    |

|------------------------------------------|----------------|------------------------------------------------------|--------------------------------------------------------|---------------------------------------------|

| 0<br>{Highest Priority}                  | <u></u>        | 0 <sub>16</sub> thru F <sub>16</sub><br>(see Note 1) | 0000                                                   | External: Reset<br>(RESET Signal)           |

| MID                                      | (see Note 2)   | 0 <sub>16</sub> thru F <sub>16</sub><br>(see Note 1) | 0001<br>(see Note 2)                                   | Internal MID                                |

| NMI                                      | (FFFC)         | 0 <sub>16</sub> thru F <sub>16</sub><br>(see Note 1) | 0000                                                   | External: User-<br>define LINMI<br>Signal)  |

|                                          | 0004           | 116 thru F16                                         | 0000                                                   | External: User-<br>defined (INT1<br>Signal) |

| 2                                        | (see Note 2)   | 2 <sub>16</sub> thru F <sub>16</sub> (see Note 3)    | 0001<br>(see Note 2)                                   | Internal: Arithmetic Overflow               |

| 3                                        | (300C)         | 316 thru F16                                         | 0002                                                   | Internal:<br>Decrementer                    |

| 4                                        | <u>(0010)</u>  | 416 thru F16                                         | 0003                                                   | defined (INT4/EC<br>Signal; see Note 4).    |

NOTES: 1. Level 0, MID, and NMI cannot be disabled with the Interrupt Mask.

- 2. MID and Level 2 use the same trap vector and change the interrupt Mask to the same value,

- 3. Generation of a Level 2 request by an Arithmetic Overflow condition (ST4 set to 1) is also enabled/disabled by bit \$110 of the Status Register.

- 4. INTA/EC is not an input for Level 4 interrupt trap requests (Level 4 is not usable) when the Decrementer is configured as an Event Counter.

The TMS 9995 will grant interrupt requests only between instructions (except for Level 0 Reset), which will be granted whenever it is requested, i.e., in the middle of an instruction). The TMS 9995 performs additional functions for certain interrupts, and these functions will be detailed in subsequent sections. The basic sequence that the TMS 9995 performs to service all interrupt requests is as follows:

- (1) Prioritize all pending requests and grant the request for the highest priority interrupt that is not masked by the current value of the interrupt mask in the status register or the instruction that has just been executed. (See Section 4.5 for these instructions.)

- (2) Make a context switch using the trap vector specified for the interrupt being granted.

- (3) Reset ST7 through ST11 in the status register to zero, and change the interrupt mask (ST12 through ST15) as appropriate for the level of the interrupt being granted.

- (4) Resume execution with the instruction located at the new address contained in the PC, and using the new WP.

All interrupts will be disabled until after this first instruction is executed, unless: (a) RESET is requested, in which case it will be granted, or (b) the interrupt being granted is the MID request and the NMI interrupt is requested simultaneously (in which case the NMI request will be granted before the first instruction indicated by the MID trap vector is executed.)

This sequence has several important characteristics. First of all, for those interrupts that are maskable with the interrupt mask in the status register, the mask will get changed to a value that will permit only interrupts of higher priority to interrupt their service routines. Secondly, status bit ST10 (overflow interrupt enable) is reset to zero by the servicing of any interrupt so that overflow interrupt requests cannot be generated by an unrelated program segment. Thirdly, the disabling of other interrupts until after the first instruction of the service routine is executed permits the routine to disable other interrupts by changing the interrupt mask with the first instruction. (The exception with MID and NMI is explained in Section 2.3.2.2.1.) Lastly, the vectoring and prioritizing scheme of the TMS 9996 permits interrupts to be automatically nested in most cases. If a higher priority interrupt occurs while in an interrupt service routine, a second context switch occurs to service the higher priority interrupt. When that routine is complete, a return instruction (RTWP) restores the saved context to complete processing of the lower priority interrupt. Interrupt routines should, therefore, terminate with the return instruction to restore original program parameters.

Additional details of the TMS 9995 interrupts are supplied in the following paragraphs.

#### 2.3.2.1 External Interrupt Requests

1.

\_

Each of these interrupts is requested when the designated signal is supplied to the TMS 9995.

#### 2.3.2.1.1 Interrupt Level 0 (RESET)

Interrupt Level 0 is dedicated to the RESET input of the TMS 9995. When active (Jow), BESET causes the TMS 9995 to stop instruction execution and to inhibit (take to logic level high) MEMEN, DBIN, and WE/CRUCLK. The TMS 9995 will remain in this Reset state as long as RESET is active.

When RESET is released (low-to-high transition), the TMS 9995 performs a context switch with the Level 0 interrupt trap vector (WP and PC of trap vector are in memory word addresses 000016 and 000216, respectively.) Note that the old WP, PC and ST are stored in registers 13, 14, and 15 of the new workspace. The TMS 9995 then resets all status register bits, the internal interrupt request latches (see Sections 2.3.2.1.3 and 2.3.2.2.3 for details of these latches), Flag Register bits FLAGO and FLAG1 (see Section 2.3.3.2.1 for details of the Flag Register), and the MID Flag (see Section 2.3.3.2.2). After this, the TMS 9995 starts execution with the new PC.

If HOLDA is active (high) due to HOLD being active (low) when RESET becomes active, RESET will cause HOLDA to be released (taken low) at the same time as MEMEN, DBIN, and WE/CRUCLK are taken inactive (high). HOLD can remain active as long as RESET is active and HOLDA will not be asserted. If HOLD is active when RESET is released (low-to-high transition), HOLDA will be asserted before the RESET context switch occurs and the TMS 9995 will remain in this hold state until HOLD is released. This RESET and HOLD priority scheme facilitates DMA loading of external RAM upon power-up.

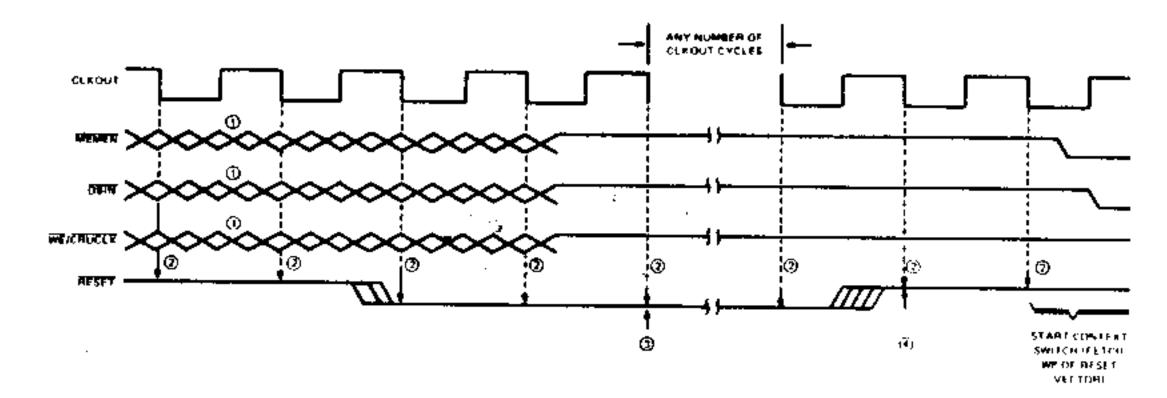

Timing relationships of the RESET signal are shown in Figure 15.

Release of the RESET signal is also the time at which the Automatic First Wait State function of the TMS 9995 can be invoked (see Section 2.3.1.3).

#### NOTES:

- (1) Oon't care XXX indicates that any type of TMS9995 cycle can be taking place

- (2) RESET is sampled at every high-to-low CLKOUT transition

- (3) RESET is required to be active (low) for a minimum of two samples to initiate the sequence. The contest switch would begin one CLKOUT cycle after (3) if RESET were Inactive (high) at (3)

- The context switch using the Reset trap vector begins one CLKOUT cycle after RESET is sampled as having returned to the inactive (high) sevel.

FIGURE 15 - TMS9995 RESET SIGNAL TIMING RELATIONSHIPS

#### 2.3.2.1.2 Non-Maskable Interrupt (NMI)

The NMI signal is the request input for the NMI level interrupt and allows ROM loaders, single-step/breakpoint/maintenance panel functions, or other user-defined functions to be implemented for the TMS 9995. This signal and its associated interrupt level are named "LOAD" in previous 9900 family products.

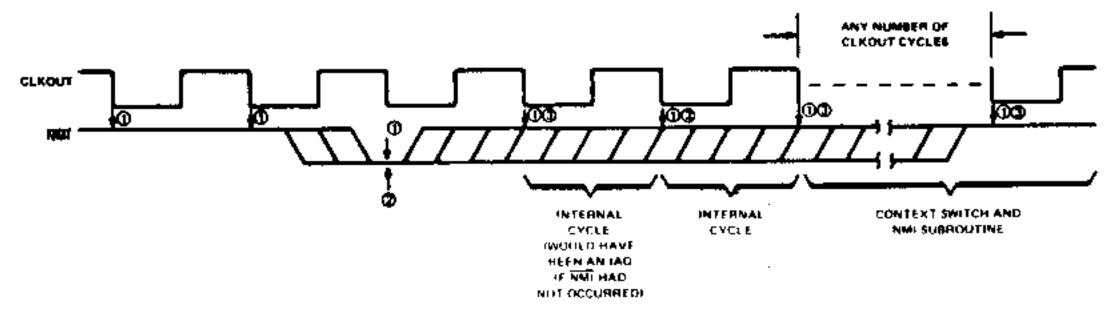

NMI being active (low) according to the timing illustrated in Figure 16 constitutes a request for the NMI level interrupt. The TMS 9995 services this request exactly according to the basic sequence previously described, with the priority level, trap vector location, and enabling/resulting status register interrupt mask values as defined in Table 2. Note that the TMS 9995 will always grant a request for the NMI level interrupt immediately after execution of the currently executing instruction is completed since NMI is exempt from the interrupt-disabling-after-execution characteristic of certain instructions and also the current value of the interrupt mask.

It should also be noted that the TMS 9995 implements four bytes of its internal RAM at the memory address of the NMI vector. This allows usage of the NMI level in minimum-chip TMS 9995 systems. It also requires, however, that this vector must be initialized, upon power-up, before the NMI level interrupt can be requested.

NOTES:

- 1 NMI is sampled at every high-to-low CLKOUT transition

- To be recognized, NMS must be ective (low) at the end of an instruction. Since instructions are variable in length, the minimum active time for NMI is variable according to the instruction being executed. Shown by ② is the last possible time that NMI must be recognized at or by before execution of the next instruction will commance. The NMI context switch begins three CLKOUT cycles after execution of the current instruction is complete.

- After an NMI context switch sequence has been initiated, NMI can remain active flow) (ndefinitely without causing consecutive NMI trap requests. To enable another NMI trap request, NMI must be taken inactive (high) and be sampled at least once at the inactive level.

FIGURE 16 - TMS9995 NMI SIGNAL TIMING RELATIONSHIPS

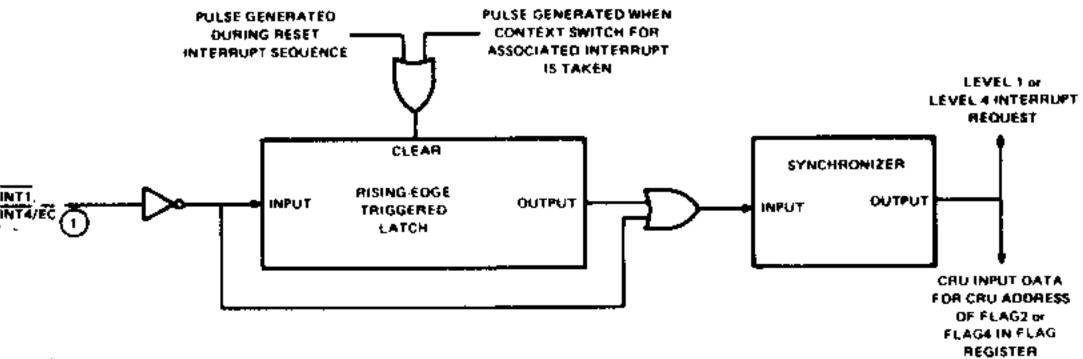

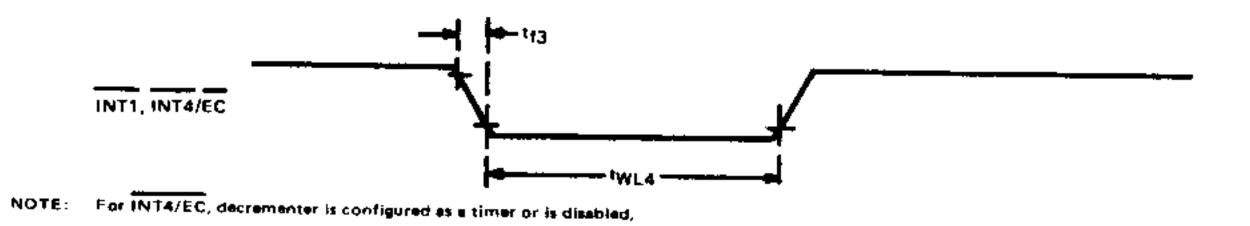

# 2.3.2.1.3 Interrupt Levels 1 and 4 (INT1 and INT4/EC)

The INT1 and INT4/EC signals are the request inputs for the Level 1 and Level 4 interrupts, respectively. (Note that if the decrementer is configured as an event counter, INT4/EC is no longer a Level 4 interrupt request input, however. See Section 2.3.1.2.2). Levels 1 and 4 are maskable, user-definable interrupts.

The INT1 and INT4/EC interrupt inputs can accept either asynchronous pluses or asynchronous levels as input signals. An internal interrupt request latch stores the occurrence of a pulse. A block diagram of the TMS 9995 internal logic for these request latches that is representative of their functional operation (but not necessarily representative of their specific logic implementation) is shown in Figure 17. Note that with this implementation only a single interrupt source is allowed if the input signal is a pulse, but multiple interrupt sources can be wired-ORed together provided that each source supplies a level as the input signal. (The levels are then removed one at a time by a hardware/software mechanism activated by the interrupt subroutine as each interrupting source is serviced by the subroutine.)

A separate latch and synchronizer is implemented for Level 1 (INT1) and Level 4 (INT4/EC). For Level 1, the input shown here is directly from the INT1 pin. For Level 4 the input shown here is from the geting shown in Figure 12.

FIGURE 17 - FUNCTIONAL BLOCK DIAGRAM OF INTERNAL INTERRUPT REQUEST LATCH

18

The TMS 9995 services each of these requests exactly according to the basic sequence previously described with the priority levels, trap vector locations, and enabling/resulting status register interrupt mask values as defined in Table 2. Each interrupt request latch will get reset when the context switch for its associated interrupt level occurs.

#### 2,3,2.2 Internally Generated Interrupts

Each of these interrupts is requested when the designated condition has occurred in the TMS 9995.

#### 2.3.2.2.1 Macro Instruction Detection (MID) Interrupt

The acquisition and attempted execution of an MID interrupt opcode will cause the MID level interrupt to be requested before execution of the next instruction begins (MID interrupt opcodes are defined in Section 4.5.15). In addition to requesting the MID level interrupt, the MID flag is set to one "1" (see Section 2.3.3.2.2). The TMS 9995 services this request exactly according to the basic sequence previously described, with the priority level, trap vector location, and enabling/resulting status register interrupt mask values as defined in Table 2. Note that the TMS 9995 will always grant a request for the MID level interrupt since MID is not affected by the interrupt mask and is higher in priority than any other interrupt except for Level 0, Reset. If the NMI interrupt is requested during an MID interrupt context switch, the MID interrupt context switch will be immediately followed by the NMI interrupt service sequence before the first instruction indicated by the MID interrupt is executed. This is done so that the NMI interrupt can be used for a single-step function with MID opcodes. Servicing the MID interrupt request is viewed as "execution" of an MID interrupt opcode, NMI allows the TMS 9995 to be halted immediately after encountering an MID opcode.

It should also be noted that the MID interrupt shares its trap vector with Level 2, the Arithmetic Overflow interrupt. (See Section 2.3.2.2.2.) The interrupt subroutine beginning with the PC of this vector should examine the MID Flag to determine the cause of the interrupt. If the MID Flag is set to "1", an MID interrupt has occurred, and if the MID Flag is set to "0", an Arithmetic Overflow interrupt has occurred. The portion of this interrupt subroutine that handles MID interrupts should always, before returning from the subroutine, reset the MID Flag to "0".

The MID interrupt has basically two applications. The MID opcodes can be considered to be illegal opcodes. The MID interrupt is then used to detect errors of this nature. The second, and primary application of the MID interrupt, is to allow the definition of additional instructions for the TMS 9995. MID opcodes are used as the opcodes for these macro instructions. Software in the MID interrupt service routine emulates the execution of these instructions. The benefit of this implementation of macros is that the macro instructions can be implemented in microcode in future processors and software will then be directly transportable to these future processors.

Note that the TMS 9995 interrupt request processing sequence does create some difficulties for re-entrant usage of MID interrupt macro instructions. In general, to avoid possible errors, MID interrupt macro instructions should not be used in the NMI and Level 1 interrupt subroutines, and should only be used in the Reset subroutine if Reset is a complete initialization of the system.

#### 2.3.2.2.2 Arithmetic Overflow Interrupt

The occurrence of an arithmetic overflow condition, defined as status register bit 4 (ST4) getting set to one (see Table 7, for those conditions that set ST4 to one), can cause the Level 2 interrupt to be requested. Note that this request will be granted immediately after the instruction that caused the overflow condition. The TMS 9995 services this request exactly according to the basic sequence previously described with the priority level, trap vector location, and enabling/resulting status register interrupt mask values as defined in Table 2.

In addition to being maskable with the interrupt mask, the Level 2 overflow interrupt request is enabled/disabled by status register bit 10 (ST10), the Arithmetic Overflow Enable Bit (i.e., ST10 = 1 enables overflow interrupt request; ST10 = 0 disables overflow interrupt request). If servicing the overflow interrupt request is temporarily overridden by servicing of a higher priority interrupt, the occurrence of the overflow condition will be retained in the contents of the status register, i.e., ST4 = 1, which is saved by the higher priority context switch. Returning from the higher priority interrupt subroutine via an RTWP instruction causes the overflow condition to be reloaded into status register bit ST4 and the overflow interrupt to be requested again (upon completion of RTWP instruction). The arithmetic overflow interrupt subroutine must reset ST4 or ST10 to zero in the status word saved in register 15 before the routine is complete to prevent generating another overflow interrupt immediately after the return.

It should also be noted that the Level 2 arithmetic overflow interrupt shares its trap vector with the MID interrupt. Section 2.3.2.2.1 describes how the interrupt subroutine beginning with the PC of this vector can determine the cause of the interrupt.

#### 2.3.2.2,3 Decrementer Interrupt

The occurrence of an interrupt request by the decrementer (see Section 2.3.1.2.2) will cause the Level 3 internal interrupt request latch to get set. This latch is similar to those for Levels 1 and 4 in that it is reset by servicing a Reset interrupt or when the context switch for its associated interrupt level occurs (Figure 17).

The Level 3 internal interrupt request latch being set constitutes a request for a Level 3 interrupt, and the TMS 9995 services this request exactly according to the basic sequence previously described with the priority level, trap vector location, and enabling/resulting status register interrupt mask values as defined in Table 2.

#### 2.3.3 Communication Register Unit Interface

The TMS 9995 accomplishes bit I/O of varying field width through the use of the Communications Register Unit (CRU). In applications demanding a bit-oriented I/O interface, the CRU performs its most valuable act: transferring a specified number of bits to or from memory and a designated device. Thus, the CRU is simply a linking mechanism between memory and peripherals.

Acting as a shift register, the CRU is a separate hardware structure of the TMS 9995 microprocessor. This structure can serially transfer up to 16 bits of data between the CPU and a specified device in a single operation. The 32768-bit CRU address space may be divided into any combination of devices, each containing any number of input or output bits. When given the bit address of a device, the CRU can test or mortify any bit in that unit. Several consecutive addresses can be occupied by a device. These CRU applications are controlled by single and multiple-bit 9995 instructions.

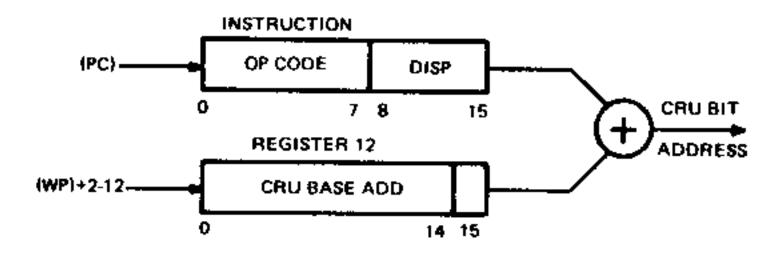

Single-bit instructions facilitate the testing or modification of a particular bit in a device. The device in which a bit is to be tested (TB), set to zero (SBZ), or set to one (SBO) is designated by the sum of the value in Register 12 and an 8-bit signed displacement value included as an operand of that instruction. Details of these instructions are given in Section 4.5.7.

Multiple-bit instructions control the serial transfer of up to 16 bits between memory and peripherals. The device with which communication is to take place is addressed by Register 12. The memory address to or from which data is to be transferred, as well as the number of bits to be transferred are included as operands of the multiple-bit instruction. Details of these instructions are given in Section 4.5.6.

The signals used in the TMS 9995 interface to the CRU are shown in Figure 18. The CRU address map is shown in Figure 19.

PO D2 are used to distinguish derivate (PRV seet existing) outlier to extend the present instructions are not used in a system. (NO) of each operatory in the CRU interfere.

FIGURE 18 - TMS9995 CRU INTERFACE

20

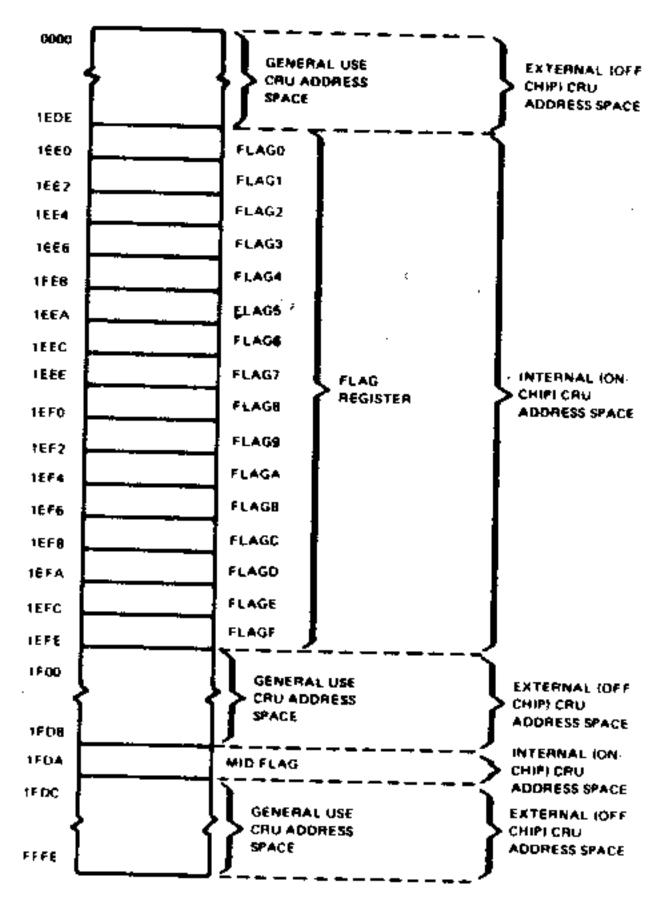

NOTE. These hex addresses are the software base addresses and are obtained by placing the 15-bit Address Bus CRU bit address in a 16-bit field, left-justifying the 15 bits in the field, and setting the LSB of the field to ≥ero.

#### FIGURE 19 - CRU ADDRESS MAP

The concept of "CRU space" is the key to CRU operations. An ideological area exists in which peripheral devices reside in the form of an address. The CRU space is this ideological area; it has monotonically increasing bit addresses. Each bit represents a bistable I/O point which can be read from or written to. CRU address space and memory address space are independent of each other. Memory space is byte-addressable, and CRU space is bit-addressable. Therefore, a desired device is accessed by placing its software base address in Register 12 and exercising the CRU commands.

CRU nomenclature is built around the four address types involved in its operation. The software base address, hardware base address, address displacement, and CRU bit address interact to link memory to peripherals in bit-serial communication via the CRU.

The software base address consists of the entire 16 bits of R12. In R12, the programmer loads twice the value of the CRU hardware address of the device with which he wishes to communicate. Because only bits 0 through 14 of Register 12 are placed on the address bus, the programmer needs to shift the hardware base address left one position (equivalent to multiplying by two).

Bits 0 through 14 of Register 12 form the hardware base address. For the single-bit instructions, the hardware base address is added to the address displacement to obtain the CRU bit address. For multiple-bit instructions the hardware base address is the CRU bit address.

#### 2.3.3.1 External CRU Devices

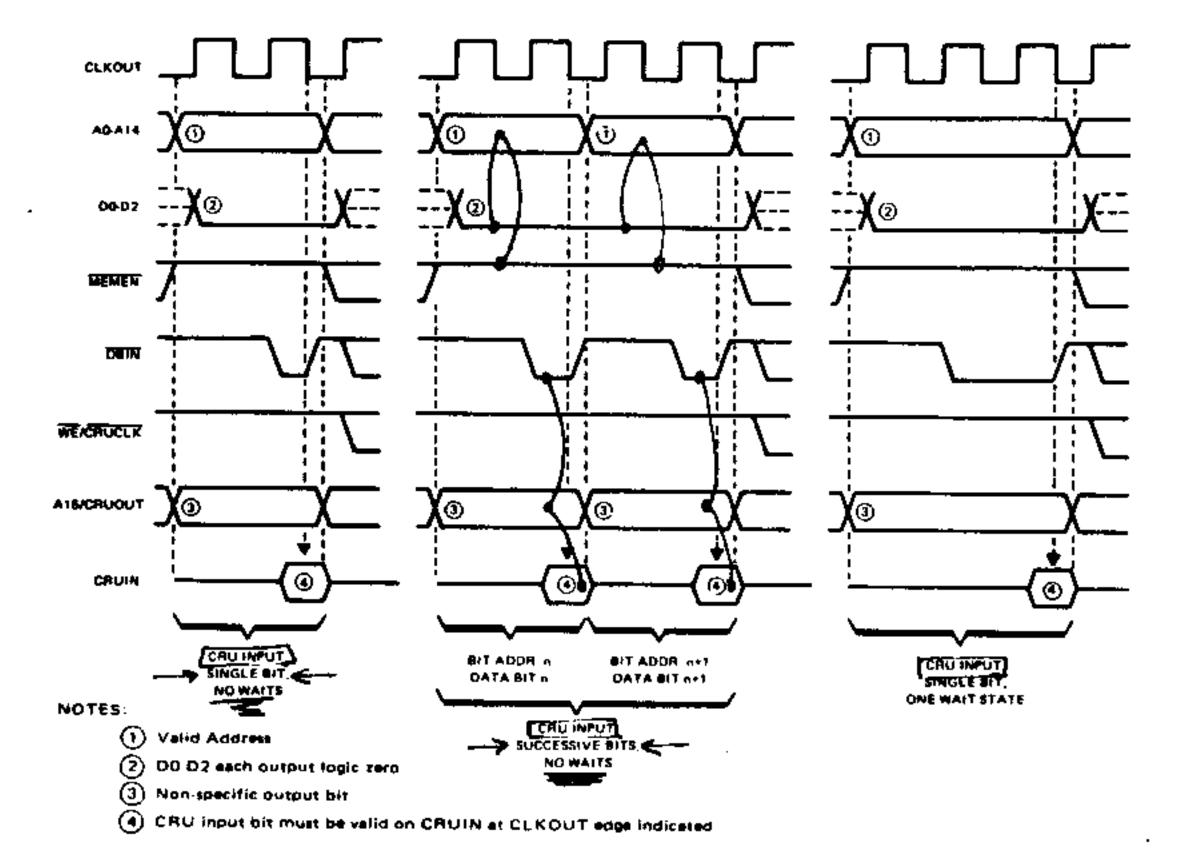

To input a data bit from an external (off-chip) CRU device, the TMS 9995 first outputs the appropriate address on A0-A14. The TMS 9995 leaves MEMEN high, outputs logic zeroes on D0-D2, strobes DBIN, and reads in the data bit on CRUIN. Completion of each CRU input cycle and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.1.3. Timing relationships of the CRU input cycle are shown in Figure 20.

FIGURE 20 - TMS9995 CRU INPUT CYCLE

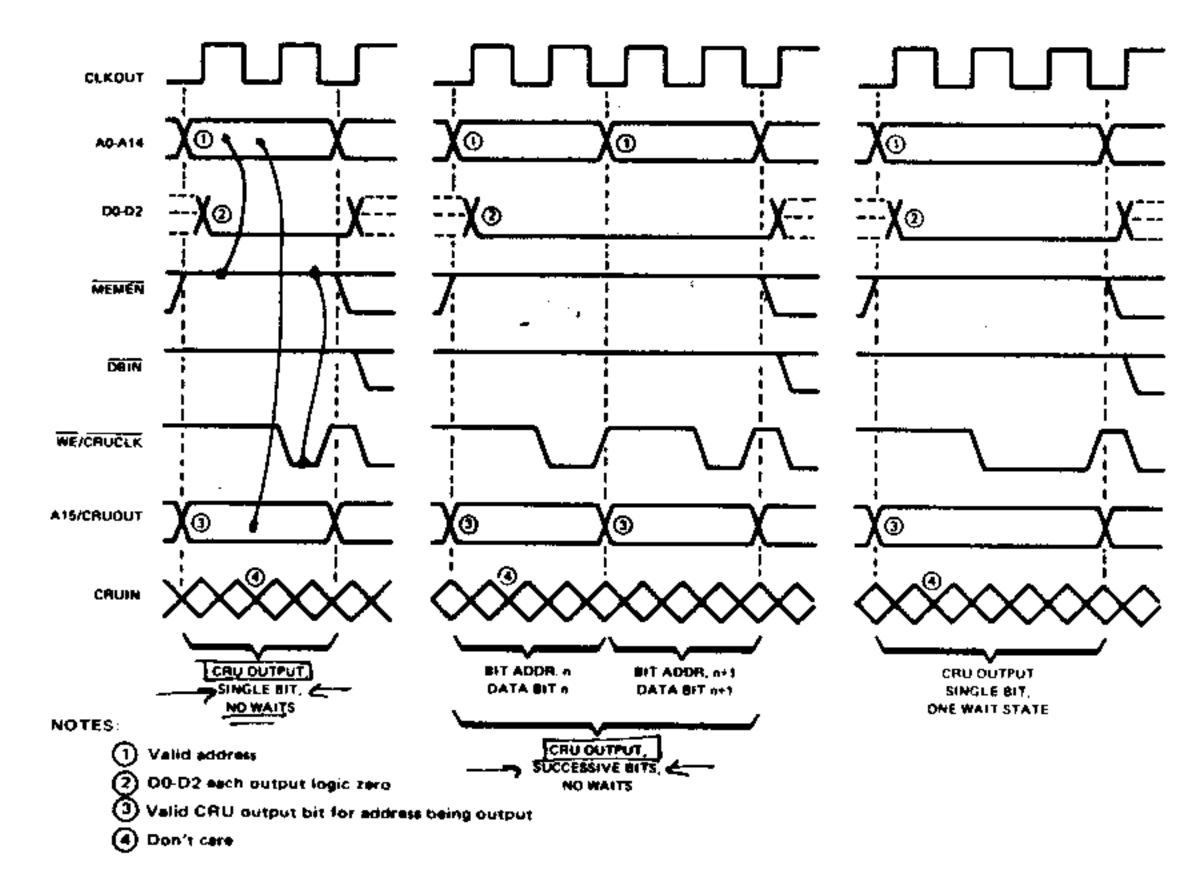

To output a data bit to an external (off-chip) CRU device, the TMS 9995 first outputs the appropriate address on A0-A14. The TMS 9995 leaves MEMEN high, outputs logic zeroes on D0-D2, outputs the data bit on A15/CRUOUT, and strobes WE/CRUCLK. Completion of each CRU output cycle and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.1.3. Timing relationships of the CRU output cycle are shown in Figure 21.

For multiple-bit transfers, these input and output cycles are repeated until transfer of the entire field of data bits specified by the CRU instruction being executed has been accomplished.

FIGURE 21 - TMS9995 CRU OUTPUT CYCLE

#### 2.3.3.1.1 Single-Bit CRU Operations

The TMS 9995 performs three single-bit CRU functions: Test Bit (TB), Set Bit to One (SBO), and Set Bit to Zero (SBZ). The SBO instruction performs a CRU output cycle with logic one for the data bit, and the SBZ instruction performs a CRU output cycle with logic zero for the data bit. A TB instruction transfers the addressed CRU bit from the CRUIN input line to bit 2 of the status register (bit ST2, the EQUAL bit).

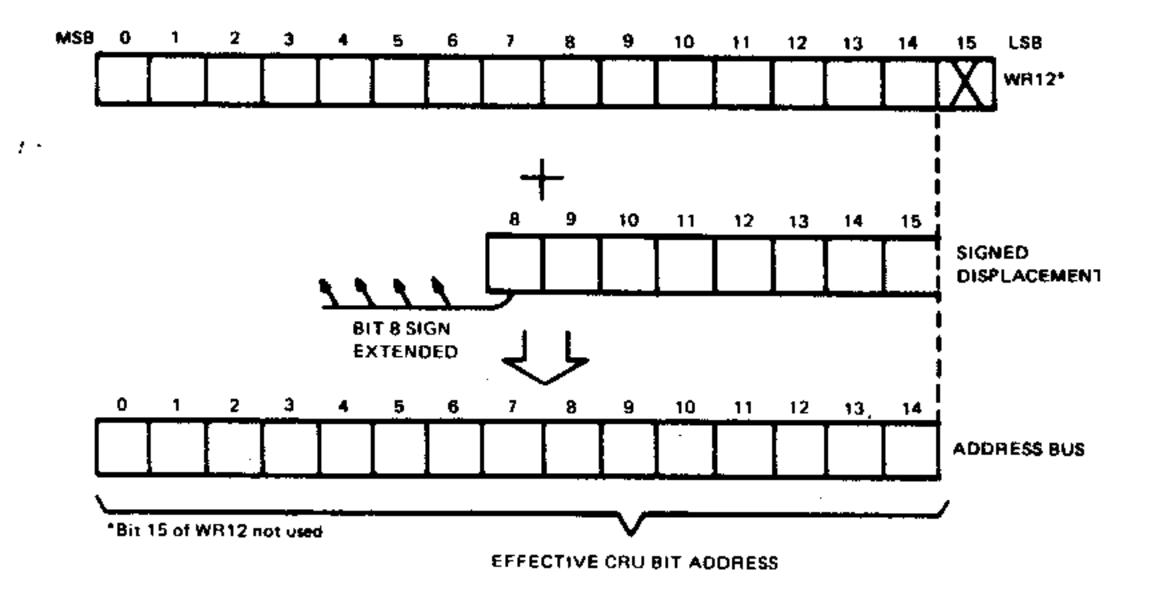

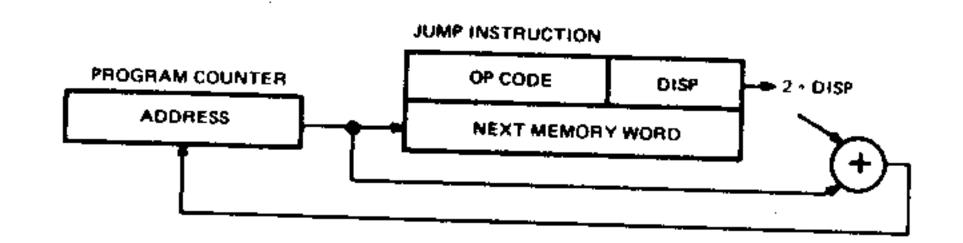

The TMS 9995 develops a CRU bit address for the single-bit operations from the CRU base address contained in workspace register 12 and the signed displacement count contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The base address from WR12 is added to the signed displacement specified in the instruction and the result is placed onto the address bus. Figure 22 illustrates the development of a single-bit CRU address.

FIGURE 22 - SINGLE BIT CRU ADDRESS DEVELOPMENT

#### 2,3.3.1,2 Multiple Bit CRU Operations

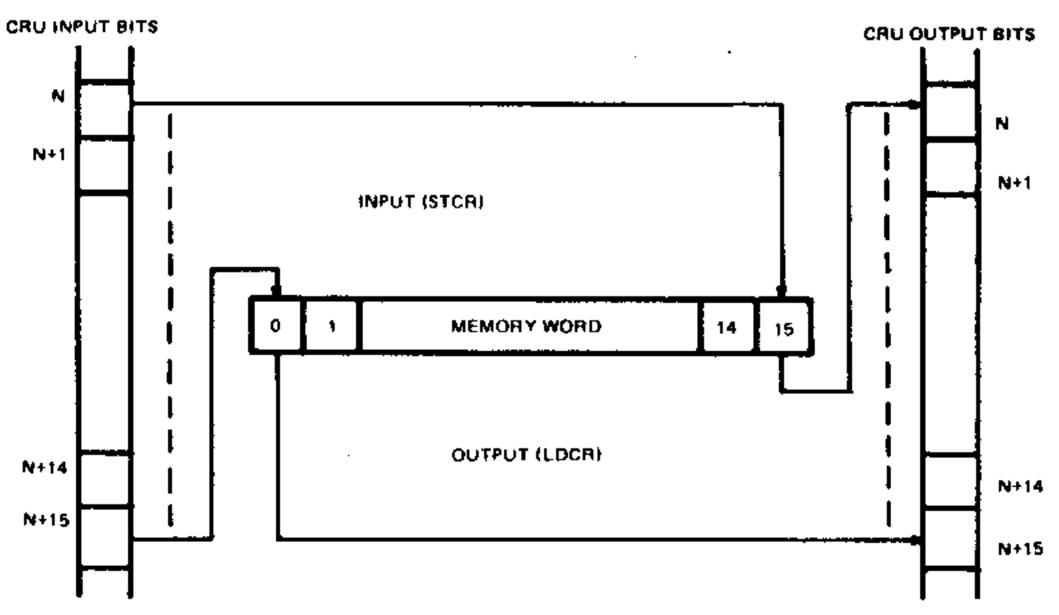

The TMS 9995 performs two multiple-bit CRU operations: store communications register (\$TCR) and load communications register (LDCR). Both operations perform a data transfer from the CRU-to-memory or from memory-to-CRU as illustrated in Figure 23. Although the figure illustrates a full 16-bit transfer operation, any number of bits from 1 through 16 may be involved.

N = BIT SPECIFIED BY CAU BASE REGISTER (WR12)

FIGURE 23 - LDCR/STCR DATA TRANSFERS

24

The LDCR instruction fetches a word from memory and right shifts it to serially transfer it to CRU output bits. If the LDCR involves eight or fewer bits, those bits come from the right-justified field within the addressed byte of the memory word. If the LDCR involves nine or more bits, those bits come from the right-justified field within the whole memory word. Register 12, bits 0 through 14, defines the starting bit address. When transferred to the CRU interface, each successive bit receives an address that is sequentially greater than the address for the previous bit. This addressing mechanism results in an order reversal of the bits; that is, bit 15 of the memory word (or bit 7) becomes the lowest addressed bit in the CRU and bit 0 becomes the highest bit in the CRU field.

A STCR instruction transfers data from the CRU to memory. If the operation involves a byte or less transfer, the transferred data will be stored right-justified in the memory byte with leading bits set to zero. If the operation involves from nine to 16 bits, the transferred data is stored right-justified in the memory word with leading bits set to zero. When the input from the CRU device is complete, the lowest addressed bit from the CRU is in the least-significant bit position in the memory word or byte.

#### 2.3.3.2 Internal CRU Devices

Access of internal (on-chip) CRU devices is transparent to the TMS 9995 CRU instructions. Data can be input from and output to the bits of the internal CRU devices simply by using the appropriate CRU addresses to access these bits.

The TMS 9995 will indicate to the external world when these internal CRU bit accesses are occurring by asserting the same signals used for accessing external CRU devices (see Figure 18). The timing of these signals for internal CRU input and output cycles will be identical to the timing for external CRU input and output cycles (see Figure 20 and 21) except that during internal CRU cycles, the READY input is ignored, i.e., Wait states cannot be generated, and, during internal CRU input cycles, the TMS 9995 will ignore the CRUIN input signal. The internal bit being input will not be available to the external world on CRUIN.

The functional characteristics of the internal CRU devices are described in the following paragraphs.

# 2.3.3.2.1 Flag Register

Accessible via CRU input and output instructions that are executed to dedicated internal CRU bit addresses (see Figure 19) is the internal Flag Register. The 16-bit Flag Register contains both predefined TMS 9995 systems flags and user-definable flags as detailed in Table 3. The predefined system flags are the configuration bit for the Decrementer, the Decrementer enable bit, and the internal interrupt request latch CRU inputs. Note that CRU output operations to the internal interrupt request latch Flag addresses will not cause these latches to be either set or reset. These Flag bits are input only and allow the presence of these interrupt requests to be detected when the occurrence of the interrupts themselves is inhibited by the value of the interrupt mask in the status register.

#### 2.3.3.2.2 MID Flag

Accessible via CRU input and output instructions that are executed to a dedicated internal CRU bit address (see Figure 19) is the MID Flag. The MID Flag is set to one by a MID interrupt, and reset to zero by the software of the MID interrupt routine (see Section 2.3.2.2.1). Note that setting the MID Flag to one with a CRU instruction will not cause the MID interrupt to be requested.

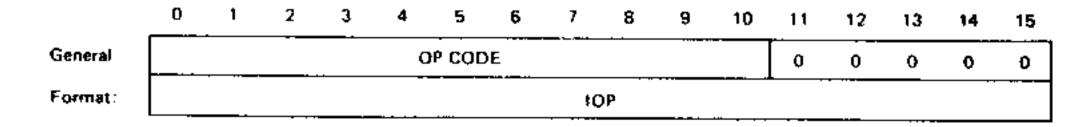

#### 2.3.4 External Instructions

The TMS 9995 has five external instructions (see Table 4) that allow user-defined external functions to be initiated under program control. These instructions are CKON, CKOF, RSET, IDLE, and LREX. These mnemonics, except for IDLE, relate to functions implemented in the 990 minicomputer and do not restrict use of the instructions to initiate various user-defined functions. Execution of an IDLE instruction causes the TMS 9995 to enter the Idle state and remain in this state until a request occurs for an interrupt level that is not masked by the current value of the interrupt mask in the status register. (Note that the Reset and NMI interrupt levels are not masked by any interrupt mask value.) When any of these five instructions are executed by the TMS 9995, the TMS 9995 will use the CRU interface (see Figure 18) to perform a cycle that is identical to a single-bit CRU output cycle (see Figure 21) except for the following: (1) the address being output will be non-specific, (2) the data bit being output will be non-specific, (3) a code, specified in Table 4, will be output on D0-D2 to indicate the external instruction being executed. Note that completion of each external instruction and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.1.3.

TABLE 3 - FLAG REGISTER BIT DEFINITIONS

|          | BIT      | CRU BIT<br>ADDRESS <sup>†</sup> | DESCRIPTION                         |

|----------|----------|---------------------------------|-------------------------------------|

|          | FLAG0    | 1EE0                            | Set to 0: Decrementer configured as |

|          |          |                                 | Interval Timer.                     |

|          |          |                                 | Set to 1: Decrementer configured as |

|          | <u> </u> |                                 | Event Counter,                      |

|          | FLAG1    | 1EE2                            | Set to 0: Decrementer not enabled   |

|          |          |                                 | Set to 1: Decrementer enabled (will |

|          |          |                                 | decrement and can set in-           |

|          |          |                                 | ternal latch that requests a        |

|          |          |                                 | level 3 interrupt).                 |

|          | FLAG2    | 1EE4                            | Level 1 internal interrupt Request  |

| ,        |          |                                 | Latch CRU Input (Input-only).       |

|          |          |                                 | 0: Level 1 request not present      |

|          |          |                                 | 1: Level 1 request present          |

|          | FLAG3    | 1EE6                            | Level 3 internal Interrupt Request  |

|          |          |                                 | Latch CRU Input (Input-only).       |

|          |          |                                 | 0: Level 3 request not present      |

|          |          |                                 | 1: Level 3 request present          |

|          | FLAG4    | 1EE8                            | Level 4 Internal Interrupt Request  |

|          |          |                                 | Latch CRU Input (Input-only).       |

|          |          |                                 | 0: Level 4 request not present      |

|          |          |                                 | 1: Level 4 request present          |

|          | FLAG5    | 1EEA                            |                                     |

| <i>;</i> | FLAG6    | 1EEC                            |                                     |

|          | FLAG7    | 1666                            |                                     |

|          | FLAG8    | 1EF0                            |                                     |

|          | FLAG9    | 1EF2                            | •                                   |

|          | FLAGA    | 1EF4                            | User Defined                        |

|          | FLAGB    | 1EF6                            |                                     |

|          | FLAGC    | 1£F8                            |                                     |

|          | FLAGD    | 1EFA                            |                                     |

|          | FLAGE    | 1EFC                            |                                     |

|          | FLAGF    | \$EFE                           |                                     |

These hax numbers are those obtained by placing the 15-bit Address Bus CRU address in a 16-bit field, left justifying the 15 bits in the field, and setting the LSB of the field to zero,

TABLE 4 - TMS 9995 EXTERNAL INSTRUCTION CODES

| INSTRUCTION                           | CODE DURING CYCLE |    |    |  |

|---------------------------------------|-------------------|----|----|--|

|                                       | D0                | D1 | D2 |  |

| CRU:<br>SBO, SBZ, TB,<br>LDCR or STCR | 0                 | 0  | 0  |  |

| IOLE                                  | 0                 | 1  | 0  |  |

| ASET                                  | 0                 | 7  | t  |  |

| CKON                                  | 1                 | 0  | 1  |  |

| CKOF                                  | 1                 | 1  | 0  |  |

| LREX                                  | 1                 | 1  | 1  |  |

When the TMS 9995 is in the Idle state, cycles with the Idle code will occur repeatedly until a request for an interrupt level that is not masked by the interrupt mask in the status register occurs.

A Hold state can occur during an Idle state, with entry to and return from the Hold state occurring at the Idle code cycle boundaries. (See Section 2.3.1.1.3 for details of entry to and return from the Hold state.)

# 2.3.5 TMS 9995 Internal ALU/Other Operation Cycles

When the TMS 9995 is performing an operation internally and is not using the memory, CRU, or external instruction interfaces<sup>†</sup> or is not in the Hold state, the TMS 9995 will, for as many CLKOUT cycles as needed, do the following with its interface signals:

- Output a non-specific address on A0-A14 and A15/CRUOUT

- Output non-specific data on D0-D7

- Output logic level high on MEMEN, DBIN, and WE/CRUCLK

- Output logic level low on IAQ/HOLDA, and

- Ignore the READY and CRUIN inputs.

The HOLD input is still active, however, as the TMS 9995 can enter a Hold state while performing an internal ALU/other operation. Also, all interrupt inputs are still active.

# TMS 9995 PIN DESCRIPTION

Table 5 defines the TMS 9995 pin assignments and describes the function of each pin. Figure 24 illustrates the TMS 9995 pin assignment information.

| XTAL1<br>XTAL2/CLKIN | 1 <u>[</u>   | <b>D</b> 40   | A15/CRUOUT |

|----------------------|--------------|---------------|------------|

|                      | 2 [          | <b>[</b> ] 39 | A14        |

| CEKOUT               | 3 🛭          | <b>]]</b> 38  | A13        |

| <b>D7</b>            | 4 Q          | 37            | A12        |

| D6                   | 5 🕻          | <b>5</b> 36   | A11        |

| D5                   | 6 🛛          | <b>]</b> 35   | A10        |

| D4                   | 7 🗓          | 34            | A9         |

| D3                   | 8 <b>[</b> ] | <b>5</b> 33   | 8A         |

| D2                   | 9 []         | <b>5</b> 32   | A7         |

| , vcc                | 10 🛛         | <b>5</b> 31   | VSS        |

| D1                   | 11 [         | <b>1</b> 30   | A6         |

| <b>D</b> 0           | 12 [         | 29            | A5         |

| CRUIN                | 13 🛛         | <b>[]</b> 28  | A4         |

| INTA/EC              | 14 🛛         | 27            | A3         |

| , inti               | 15 [         | <b>5</b> 26   | A2         |

| IAQ/HOLDA            | 16 [         | 25            | A1         |

| DBIN                 | 17 🗓         | <b>[</b> ] 24 | A0         |

| HOLD                 | 18 [         | <b>[</b> ] 23 | READY      |

| WE/CRUCLK            | 19 🛚         | D 22          | RESET      |

| MEMEN                | 20 [         | 21            | NMI        |

|                      | ī            | <br>          |            |

FIGURE 24 - PIN ASSIGNMENTS

<sup>†</sup> Internal memory space and internal CRU device accesses are defined as using the memory and CRU interfaces.

TABLE 5 - TMS 9995 PIN DESCRIPTION

| \$IGNAL         | PIN      | 1/0         | DESCRIPTION                                                      |

|-----------------|----------|-------------|------------------------------------------------------------------|

|                 | -        |             | POWER SUPPLIES                                                   |

| Vcc             | 10       | i l         | Supply voltage (+5 V Nom)                                        |

| v <sub>SS</sub> | 31       |             | Ground reference                                                 |

| -               |          |             | CLOCKS                                                           |

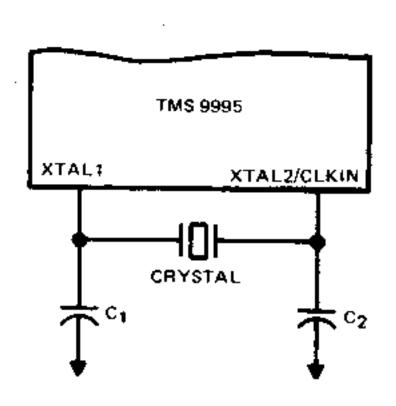

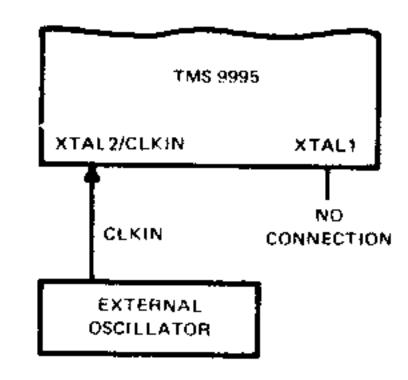

| XTAL2/CLKIN     | 2        | IN          | Crystal input pin for internal oscillator. Also                  |

|                 | -        | '           | input pin for external oscillator.                               |

| XTAL1           | 1        | IN          | Crystal input pin for internal oscillator,                       |

| CLKOUT          | 3        | OUT         | Clock output signal. The frequency of                            |

|                 |          |             | CLKOUT is one fourth the oscillator input                        |

|                 |          |             | (external oscillator) or crystal (internal oscil-                |

|                 |          |             | lator) (requency.                                                |

|                 |          |             | ADDRESS BUS                                                      |

| A0              | 24       | OUT         | Address Bus. A0 is the most significant bit of                   |

| A1              | 25       | DUT         | the 16 bit memory address bus and the 15 bit.                    |

| A2              | 26       | OUT         | CRU address bus. A14 is the 2nd least signifi-                   |

| A3              | 27       | OUT         | cant bit of the 16 bit memory address bus and                    |

| A4              | 28       | OUT         | the LSB of the 15 bit CRU address bus. The                       |

| A5              | 29       | OUT         | address but assumes the high impedance state                     |

| A6              | 30       | 001         | when the TMS 9995 is in the Hold state,                          |

| A7              | 32       | OUT         |                                                                  |

| A8              | 33       | OUT         |                                                                  |

| A9              | 34       | 001         |                                                                  |

| A10<br>A11      | 35       | OUT         |                                                                  |

| A12             | 36<br>37 | OUT         |                                                                  |

| A13             | 38       | OUT         |                                                                  |

| A14             | 39       | OUT         |                                                                  |

|                 | 33       | 001         | •                                                                |

| A15/CRUQUT      | 40       | OUT         | Address bit 15/CRU output data, A15/                             |

|                 |          |             | CRUOUT is the LSB of the 16 bit memory                           |

|                 |          |             | address bus and the output data line for CRU                     |

|                 |          |             | output instructions. A15/CRUOUT assumes                          |

|                 |          |             | the high impedance state when the TMS 9995 is in the Hold state. |

|                 |          | <del></del> | DATA BUS                                                         |

| D <b>0</b>      | 12       | 1/0         | Data Bus. During memory cycles (MEMEN                            |

| D1              | 11       | 1/0         | active) D0 (the MSB) through D7 (the LSB)                        |

| D2              | 9        | 1/0         | ere used to transfer data to/from the external                   |

| D3              | 8        | 1/0         | memory system. During non-memory cycles                          |

| D4              | 7        | 1/0         | (MEMEN inactive) D0, D1 and D2 are used                          |

| D6              | 6        | 1/0         | to indicate whether the TMS 9995 is perform-                     |

| D6              | 5        | 1/0         | ing a CRU cycle or an external instruction.                      |

| D7              | 4        | 1/0         | The date bus essumes the high impedance                          |

|                 |          |             | state when the TMS 9995 is in the Hold state.                    |

|                 |          |             | CRU                                                              |

| CRUIN           | 13       | 10          | CRU input data. During CRU cycles, CRUIN is                      |

|                 |          | ļ <b>1</b>  | the input data line for CRU input data.                          |

TABLE 5 - TMS 9995 PIN DESCRIPTION (Continued)