The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# TMS 9901 Programmable Systems Interface Data Manual

**JULY 1977**

TEXAS INSTRUMENTS

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

Copyright © 1977

Texas Instruments Incorporated

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date.

# **TABLE OF CONTENTS**

| 1.    | INT        | RODUCTION                                                                      |

|-------|------------|--------------------------------------------------------------------------------|

|       | 1.1        | Description                                                                    |

|       | 1.2        | Key Features                                                                   |

| 2.    | FIII       | NCTIONAL DESCRIPTION                                                           |

|       | 2.1        | CPU Interface                                                                  |

|       | 2.2        | GI O III Elide                                                                 |

|       | 2.3        | System Interface                                                               |

|       | 2.4        | Interrupt Control                                                              |

|       | 2.5        | Programmable Real Time Clock                                                   |

|       | 2.6        | Programmable Real Time Clock                                                   |

|       | 2.7        | Pin Definitions                                                                |

|       |            |                                                                                |

| 3.    |            | S 9901 ELECTRICAL SPECIFICATIONS                                               |

|       | 3.1        | Absolute Maximum Ratings Over Operating Free-Air Temperature Range             |

|       | 3.2        | Recommended Operating Conditions                                               |

|       | 3.3        | Electrical Characteristics Over Full Range of Recommended Operating Conditions |

|       | 3.4<br>3.5 | Timing Requirements Over Full Range of Operating Conditions                    |

|       | 3.5        | Switching Characteristics Over Full Range of Recommended Operating Conditions  |

| 4.    | MEG        | CHANICAL DATA                                                                  |

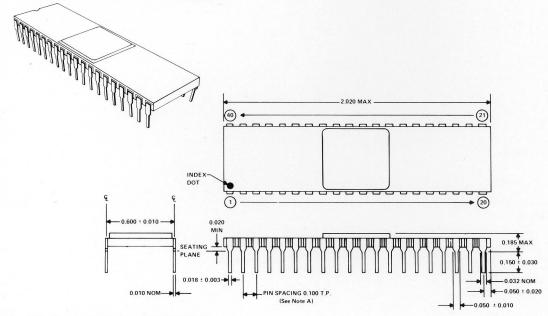

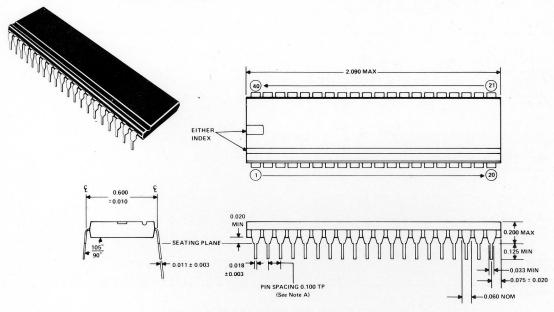

|       | 4.1        | TMS 9901 — 40 Pin Ceramic Package                                              |

|       | 4.2        | TMS 9901 — 40 Pin Plastic Package                                              |

|       |            | INTERFACE                                                                      |

|       |            |                                                                                |

|       |            | LIST OF ILLUSTRATIONS                                                          |

| Figu  | ire 1      | 9900/9980 System                                                               |

|       | re 2       | 9900/9980 System TMS 9901 Block Diagram                                        |

| 0     | re 3       | Interrupt Control Logic                                                        |

| Figu  |            | I/O Interface                                                                  |

| Figu  |            | Real Time Clock                                                                |

| Figu  | re 6       | TMS 9900 — TMS 9901 Interface                                                  |

| Figu  |            | TMS 9980 — TMS 9901 Interface                                                  |

| Figu  | re 8       | Switching Characteristics                                                      |

|       |            |                                                                                |

|       |            | LIST OF TABLES                                                                 |

| Table | e 1        | CRU Bit Assignments                                                            |

| Table | 2          | Interrupt Code Generation                                                      |

| Table |            | Software Examples                                                              |

| Table | 4          | TMS 9980 Interrupt Level Data                                                  |

| Table | e 5        | TMS 9901 Pin Assignments and Functions                                         |

#### 1. INTRODUCTION

#### 1.1 DESCRIPTION

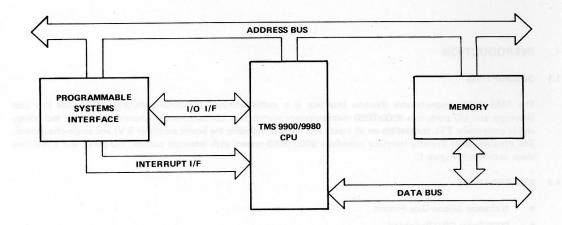

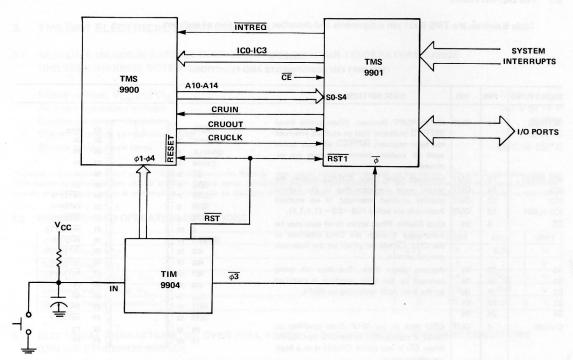

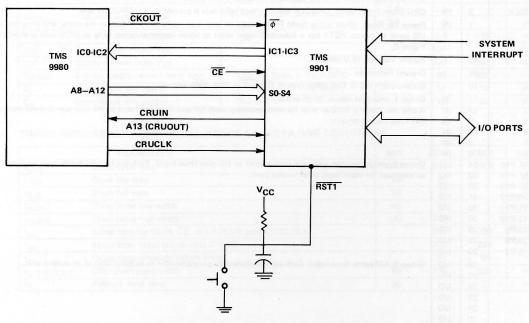

The TMS 9901 Programmable Systems Interface is a multifunctioned component designed to provide low cost interrupts and I/O ports in a 9900/9980 microprocessor system. It is fabricated with N-channel silicon-gate technology and is completely TTL compatible on all inputs and outputs including the power supply (+ 5 V) and single-phase clock. The Programmable Systems Interface provides a 9900/9980 system with interrupt control, I/O ports, and a real-time clock as shown in Figure 1.

#### 1.2 KEY FEATURES

- N-channel Silicon-Gate Process

- 9900 Series CRU Peripheral

- Performs Interrupt and I/O Interface Functions

- 6 Dedicated Interrupt Input Lines

- 7 Dedicated I/O Ports

- 9 Ports Programmable as Interrupts or I/O

- Easily Stacked for Interrupt and I/O Expansion

- Interval and Event Timer

- Single 5 V Supply

#### 2. FUNCTIONAL DESCRIPTION

#### 2.1 CPU INTERFACE

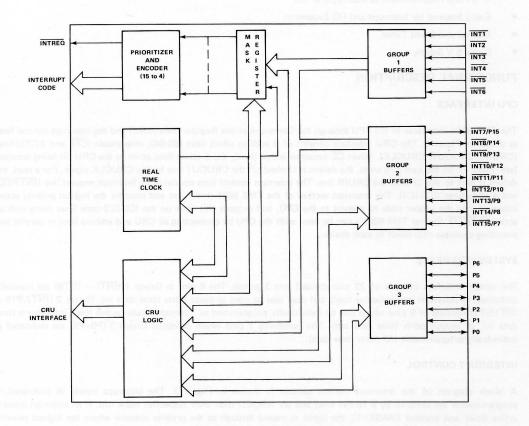

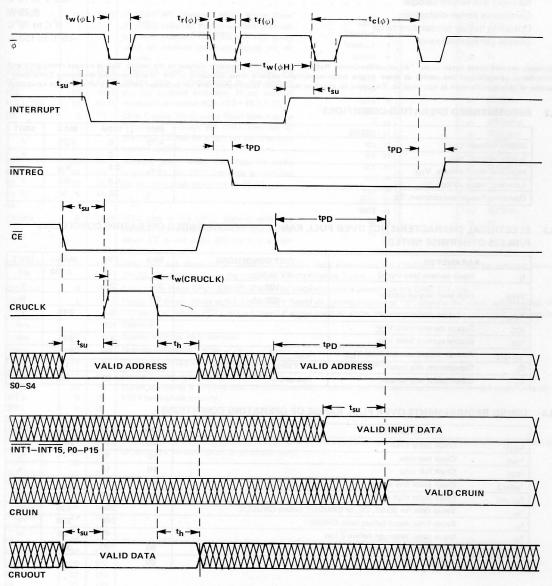

The TMS 9901 interfaces to the CPU through the Communications Register Unit (CRU) and the interrupt control lines as shown in Figure 2. The CRU interface consists of 5 address select lines (S0-S4), chip enable ( $\overline{\text{CE}}$ ), and 3 CRU lines (CRUIN, CRUOUT, CRUCLK). When  $\overline{\text{CE}}$  becomes active (low), the 5 select lines point to the CRU bit being accessed (see Table 1). In the case of a write, the datum is strobed off the CRUOUT line by the CRUCLK signal. For a read, the datum is sent to the CPU on the CRUIN line. The interrupt control lines consist of an interrupt request line ( $\overline{\text{INTREO}}$ ) and 4 code lines (ICO-IC3). The interrupt section of the TMS 9901 prioritizes and encodes the highest priority active interrupt into the proper code to present to the CPU, and outputs this code on the ICO-IC3 code lines along with an active  $\overline{\text{INTREO}}$ . Several TMS 9901's can be used with the CPU by connecting all CRU and address lines in parallel and providing a unique chip select to each device.

#### 2.2 SYSTEM INTERFACE

The system interface consists of 22 pins divided into 3 groups. The 6 pins in Group 1 ( $\overline{\text{INTI}} - \overline{\text{INT6}}$ ) are normally dedicated to interrupt inputs (active low), but may also be used as input ports (true data in). Group 2 ( $\overline{\text{INT7}}/\text{P15} - \overline{\text{INT15}}/\text{P7}$ ) consists of 9 pins which can be individually programmed as interrupt inputs (active low), input ports (true data in), or output ports (true data out). The remaining 7 pins which comprise Group 3 (P0–P6) are dedicated as individually programmable I/O ports (true data).

#### 2.3 INTERRUPT CONTROL

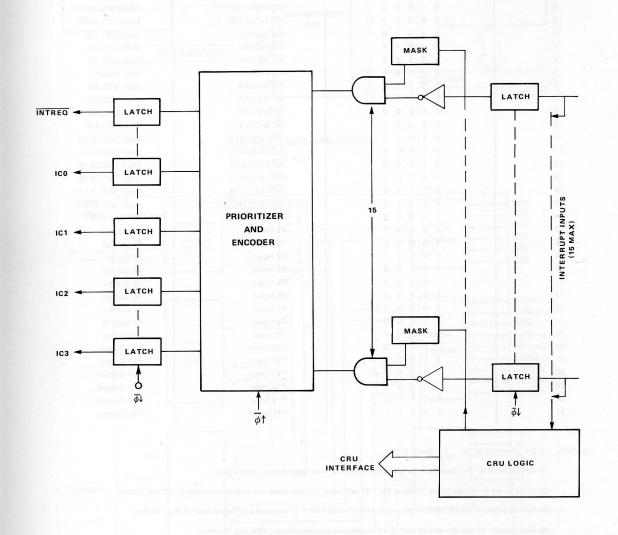

A block diagram of the interrupt control section is shown in Figure 3. The interrupt inputs (6 dedicated, 9 programmable) are sampled by  $\overline{\phi}$  (active low) and are ANDED with their respective mask bits. If an interrupt input is active (low) and enabled (MASK=1), the signal is passed through to the priority encoder where the highest priority signal is encoded into a 4 bit binary code as shown in Table 2. The code along with interrupt request is then output via the CPU interface on the leading edge of the next  $\overline{\phi}$  to ensure proper synchronization to the processor.

FIGURE 1 - 9900/9980 SYSTEM

FIGURE 2 - TMS 9901 BLOCK DIAGRAM

TABLE 1

| RU Bit  | $S_0 S_1 S_2 S_3 S_4 \bigcirc$ | CRU Read Data          | CRU Write Data  |

|---------|--------------------------------|------------------------|-----------------|

| o       | 0 0 0 0 0 6                    | CONTROL BIT(1)         | CONTROL BIT(1)  |

| 1       | 0 0 0 0 1 0                    | INT1/CLK1(2)           | Mask 1/CLK1(3)  |

| 2       | 0 0 0 1 0 0                    | INT2/CLK2              | Mask 2/CLK2     |

| 3       | 0 0 0 1 1 0                    | INT3/CLK3              | Mask 3/CLK3     |

| 4       | 0 0 1 0 0                      | INT4/CLK4              | Mask 4/CLK4     |

| 5       | 0 0 1 0 1 0                    | INT5/CLK5              | Mask 5/CLK5     |

| 6       | 0 0 1 1 0 0                    | INT6/CLK6              | Mask 6/CLK6     |

| 7 HOTAS | 0 0 1 1 1 0                    | ĪNT7/CLK7              | Mask 7/CLK7     |

| 8       | 0 1 0 0 0 0                    | ĪNT8/CLK8              | Mask 8/CLK8     |

| 9       | 0 1 0 0 1 0                    | INT9/CLK9              | Mask 9/CLK9     |

| 10      | 0 1 0 1 0 0                    | INT10/CLK10            | Mask 10/CLK10   |

| 11      | 0 1 0 1 1 0                    | INT11/CLK11            | Mask 11/CLK11   |

| 12      | 0 1 1 0 0 0                    | INT12/CLK12            | Mask 12/CLK12   |

| 13      | 0 1 1 0 1 0                    | INT13/CLK13            | Mask 13/CLK13   |

| 14      | 0 1 1 1 0 0                    | INT14/CLK14            | Mask 14/CLK14   |

| 15      | 0 1 1 1 1 0                    | INT15/INTREQ           | Mask 15/RST2(4) |

| 16      | 1 0 0 0 0 0                    | PO Input(5)            | PO Output(6)    |

| 17      | 1 0 0 0 1 0                    | P1 Input               | P1 Output       |

| 18      | 1 0 0 1 0 0                    | P2 Input               | P2 Output       |

| 19      | 1 0 0 1 1 0                    | P3 Input               | P3 Output       |

| 20      | 1 0 1 0 0 0                    | P4 Input               | P4 Output       |

| 21      | 1 0 1 0 1 0                    | P5 Input               | P5 Output       |

| 22      | 1 0 1 1 0 0                    | P6 Input               | P6 Output       |

| 23      | 1 0 1 1 1 00                   | P7 Input               | P7 Output       |

| 24      | 1 1 0 0 0 0                    | P8 Input               | P8 Output       |

| 25      | 1 1 0 0 1 0                    | P9 Input               | P9 Output       |

| 26      | 1 1 0 1 0 0                    | P10 Input              | P10 Output      |

| 27      | 1 1 0 1 1 0                    | P11 <sup>(</sup> Input | P11 Output      |

| 28      | 1 1 1 0 0 0                    | P12 Input              | P12 Output      |

| 29      | 1 1 1 0 1 0                    | P13 Input              | P13 Output      |

| 30      | 1 1 1 1 0 0                    | P14 Input              | P14 Output      |

| 31      | 1 1 1 1 1 0                    | P15 Input              | P15 Output      |

NOTES: (1) 0 = Interrupt Mode 1 = Clock Mode

- (2) Data present on  $\overline{\mathsf{INT}}$  input pin (or clock value) will be read regardless of mask value.

- (3) While in the Interrupt Mode (Control Bit = 0) writing a "1" into mask will enable interrupt; a "0" will disable.

- (4) Writing a zero to bit 15 while in the clock mode (control bit = 1) executes a software reset of the I/O pins.

- (5) Data present on the pin will be read. Output data can be read without affecting the data.

- (6) Writing data to the port will program the port to the output mode and output the data.

FIGURE 3 – INTERRUPT CONTROL LOGIC

TABLE 2

INTERRUPT CODE GENERATION

| INTERRUPT/STATE | PRIORITY    | lco | l <sub>C1</sub> | I <sub>C2</sub> | IC3 | INTREQ |

|-----------------|-------------|-----|-----------------|-----------------|-----|--------|

| ĪNT 1           | 1 (HIGHEST) | 0   | 0               | 0               | 1   | 0      |

| INT 2           | 2           | 0   | 0               | 1               | 0   | 0      |

| INT 3/CLOCK     | 3           | 0   | 0               | 1               | 1   | 0      |

| INT 4           | 4           | 0   | 1               | 0               | 0   | 0      |

| INT 5           | 5           | 0   | 1               | 0               | 1   | 0      |

| INT 6           | 6           | 0   | 1               | 1               | 0   | 0      |

| INT 7           | 7 10771900  | 0   | 1               | 1               | 1   | 0      |

| INT 8           | 8           | 1   | 0               | 0               | 0   | 0      |

| INT 9           | 9           | 1   | 0               | 0               | 1   | 0      |

| INT 10          | 10          | 1   | 0               | 1               | 0   | 0      |

| INT 11          | 11          | 1   | 0               | 1               | 1   | 0      |

| INT 12          | 12          | 1   | 1               | 0               | 0   | 0      |

| INT 13          | 13          | 1   | 1               | 0               | 1   | 0      |

| INT 14          | 14          | 1   | 1               | 1               | 0   | 0      |

| INT 15          | 15 (LOWEST) | 1   | 1               | 1               | 1   | 0      |

| NO INTERRUPT    | _           | 1   | 1               | 1               | 1   | 1      |

The output signals will remain valid until the corresponding interrupt input is removed, the interrupt is disabled (MASK=0), or a higher priority enabled interrupt becomes active. When the highest priority enabled interrupt is removed, the code corresponding to the next highest priority enabled interrupt is output. If no enabled interrupt is active, all CPU interface lines (INTREQ, ICO-IC3) are held high. RSTI (power-up-reset) will force the output code to (0,0,0,0) with INTREQ held high and will reset all mask bits low (interrupts disabled). Individual interrupts can be subsequently enabled (disabled) by programming the appropriate command bits. Unused interrupt inputs may be used as datum inputs by disabling the interrupt (MASK=0).

#### 2.4 INPUT/OUTPUT

A block diagram of the I/O section is shown in Figure 4. Up to 16 individually controlled I/O ports are available (7 dedicated, 9 programmable). RST1 or RST2 (a command bit) will program all ports to the input mode. Writing a datum to any port will program that port to the output mode and latch out the datum. The port will then remain in the output mode until either RST1 or RST2 are executed. Data present on the Group 2 pins can be read by either the Read Interrupt Commands or the Read Input Commands. Group 2 pins being used as input ports should have their respective Interrupt Mask values reset (Iow) to prevent false interrupts from occurring. In applications where Group 1 pins are not required as interrupt inputs, they may be used as input ports and read using the Read Input commands. As with Group 2 ports, any pins being used as input ports should have their respective Interrupt Masks disabled.

#### 2.5 PROGRAMMABLE REAL TIME CLOCK

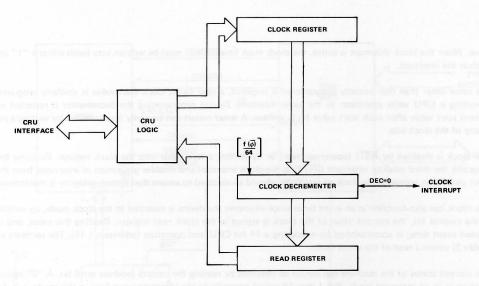

A block diagram of the programmable real time clock section is shown in Figure 5. The clock consists of a 14 bit counter that decrements at a rate of  $F(\phi)/64$  (at 3 MHz this results in a maximum interval of 349 ms with a resolution of 21.3  $\mu$ s) and can be used as either an interval timer or as an event timer.

The clock is accessed by writing a one into the control bit (address 0) to force CRU bits 1-15 to clock mode. (See Table 1.) Writing a nonzero value into the clock register then enables the clock and sets its frequency. During system set up this entire operation can be accomplished with one additional I/O instruction (LDCR) as shown in Table 3. The clock functions as an interval timer by decrementing to zero, issuing an interrupt, and restarting at the programmed start

1/0 CONTROL DATA LATCH CRU CRU INTERFACE LOGIC I/O PORTS (PO-P15 MAX) 1/0 CONTROL DATA LATCH

FIGURE 4 – I/O INTERFACE

## FIGURE 5 - REAL TIME CLOCK

# TABLE 3 SOFTWARE EXAMPLES

- ASSUMPTIONS

System uses clock at maximum interval

Total of 6 interrupts are used

8 bits are used as output port

8 bits are used as input port

RSTI (power up reset) has already been applied.

|                              | LI                                    | R12,PSIBAS                               | Setup CRU Base Address                                                                                                            | to point to 9901                           |  |

|------------------------------|---------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| system<br>Setup for          | LDCR                                  | @X,0                                     | Program Clock with maxi                                                                                                           | mum interval                               |  |

| nterrupt                     | LDCR                                  | @Y,7                                     | Re-enter interrupt mode                                                                                                           | and enable top 6 interrupts                |  |

| ystem                        | LI                                    | R12,PSIBAS+ 16                           | Move CRU Base to point                                                                                                            | to I/O port                                |  |

| Setup for<br>Output<br>Ports | LDCR                                  | R1,8                                     | Move most significant by                                                                                                          | Company of the second second second second |  |

| lead                         | [Li                                   | R12,PSIBAS+ 24                           | Move CRU Base to point                                                                                                            | to input ports                             |  |

| rogrammed<br>nputs           | STCR                                  | R2,8                                     | Move input port to most                                                                                                           |                                            |  |

| bedi norta                   | (x)——                                 | ►FFFF                                    |                                                                                                                                   |                                            |  |

|                              | innecting tive                        |                                          |                                                                                                                                   |                                            |  |

|                              | (Y)——                                 | →7FXX                                    |                                                                                                                                   |                                            |  |

|                              |                                       |                                          |                                                                                                                                   |                                            |  |

|                              |                                       | Don't Care                               | s                                                                                                                                 |                                            |  |

|                              | BLWP                                  | Don't Care                               | Save Interrupt Mask                                                                                                               |                                            |  |

|                              | BLWP                                  |                                          | V 2 751                                                                                                                           |                                            |  |

| LKPC                         | BLWP<br>LIMI<br>LI                    | CLKVCT  0 R12,PSIBAS +1                  | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base                                                                           | e Latch Clock Value                        |  |

| LKPC                         | BLWP<br>•<br>•<br>•                   | CLKVCT  0 R12,PSIBAS+1 -1                | Save Interrupt Mask  Disable INTERRUPTS                                                                                           |                                            |  |

| LKPC                         | BLWP<br>LIMI<br>LI<br>SB0             | CLKVCT  0 R12,PSIBAS +1                  | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod                                                   | h Value into R4                            |  |

| LKPC                         | BLWP  LIMI LI SB0 STCR                | 0<br>R12,PSIBAS+1<br>-1<br>R4, 14        | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod Store Read Register Latc                          | h Value into R4                            |  |

| LKPC                         | BLWP  LIMI LI SBO STCR SBZ            | 0<br>R12,PSIBAS+1<br>-1<br>R4, 14        | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod Store Read Register Late Reenter Interrupt Mode a | h Value into R4                            |  |

| LKPC                         | BLWP  LIMI LI SBO STCR SBZ            | 0<br>R12,PSIBAS+1<br>-1<br>R4, 14        | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod Store Read Register Late Reenter Interrupt Mode a | h Value into R4                            |  |

| tarte                        | BLWP  LIMI LI SBO STCR SBZ            | 0<br>R12,PSIBAS+1<br>-1<br>R4, 14        | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod Store Read Register Late Reenter Interrupt Mode a | h Value into R4                            |  |

| arte                         | BLWP  LIMI LI SBO STCR SBZ RTWP       | 0<br>R12,PSIBAS +1<br>-1<br>R4, 14<br>-1 | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod Store Read Register Late Reenter Interrupt Mode a | h Value into R4                            |  |

| CLKPC<br>CLKVCT              | BLWP  LIMI LI SBO STCR SBZ RTWP  DATA | 0<br>R12,PSIBAS +1<br>-1<br>R4, 14<br>-1 | Save Interrupt Mask  Disable INTERRUPTS Set up CRU Base Set 9901 into Clock Mod Store Read Register Late Reenter Interrupt Mode a | h Value into R4                            |  |

value. When the clock interrupt is active, the clock mask (mask bit 3) must be written into (with either a "1" or a "0") to clear the interrupt.

If a value other than that initially programmed is required, a new 14-bit clock start value is similarly programmed by executing a CRU write operation to the same locations. During programming the decrementer is restarted with the current start value after each start value bit is written. A timer restart can be easily implemented by writing a single bit to any of the clock bits.

The clock is disabled by RSTI (power-up-clear) or by writing a zero value into the clock register. Enabling the clock programs the third priority interrupt (INT3) as the clock interrupt and disables generation of interrupts from the INT3 input pin. When accessing the clock all interrupts should be disabled to ensure that system integrity is maintained.

The clock can also function as an event timer since whenever the device is switched to the clock mode, by writing a one to the control bit, the current value of the clock is stored in the clock read register. Reading this value, and thus the elapsed event time, is accomplished by executing a 14 bit CRU read operation (addresses 1-14). The software example (Table 3) shows a read of the event timer.

The current status of the machine can always be obtained by reading the control (address zero) bit. A "0" indicates the machine is in an interrupt mode. Bits 1 thru 15 would normally be the interrupt input lines in this mode, but if any are not needed for interrupts they may also be read with a CRU input command and interpreted as normal data inputs. A "1" read on the control bit indicates that the 9901 is in the clock mode. Reading bits 1 thru 14 completes the event timer operation as described above. Reading bit 15 indicates whether the interrupt request line is active.

A software reset  $\overline{RST2}$  can be performed by writing a "1" to the control bit followed by writing a "1" to bit 15, which forces all I/O ports to the input mode.

#### 2.6 SYSTEM OPERATION

During power up RSTI must be activated (low) for a minimum of 2 clock cycles to force the TMS 9901 into a known state. RST1 will disable all interrupts, disable the clock, program all I/O ports to the input mode, and force ICO-IC3 to (0,0,0,0) with INTREQ held high. System software must then enable the proper interrupts, program the clock (if used), and configure the I/O ports as required (See Table 3 for an example). After initial power up, the TMS 9901 will be accessed only as needed to service the clock, enable (disable) interrupts, or read (write) data to the I/O ports. The I/O ports can be reconfigured by use of the RST2 command bit.

Figure 6 illustrates the use of a TMS 9901 with a TMS 9900. The TIM 9904 is used to generate RST to reset the 9900 and the 9901 (connected to RST1). Figure 7 shows a TMS 9980 system using the TMS 9901. The reset function, load interrupt, and 4 maskable interrupts allowed in a 9980 are encoded as shown in Table 4. Connecting the system as shown ensures that the proper reset will be applied to the 9980.

TABLE 4

9980 INTERRUPT LEVEL DATA

| INTERRUPT<br>CODE<br>(IC0–IC2) | FUNCTION | VECTOR LOCATION<br>(MEMORY ADDRESS<br>IN HEX) | DEVICE ASSIGNMENT | INTERRUPT MASK VALUES<br>TO ENABLE<br>(ST12 THROUGH ST15) |

|--------------------------------|----------|-----------------------------------------------|-------------------|-----------------------------------------------------------|

| 1 1 0                          | Level 4  | 0 0 1 0                                       | External Device   | 4 Through F                                               |

| 1 0 1                          | Level 3  | 0 0 0 C                                       | External Device   | 3 Through F                                               |

| 1 0 0                          | Level 2  | 0 0 0 8                                       | External Device   | 2 Through F                                               |

| 0 1 1                          | Level 1  | 0 0 0 4                                       | External Device   | 1 Through F                                               |

| 0 0 1                          | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                                |

| 0 1 0                          | Load     | 3 F F C                                       | Load Stimulus     | Don't Care                                                |

| 0 0 0                          | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                                |

| 1 1 1                          | No-Op    |                                               |                   |                                                           |

FIGURE 6 - TMS 9900-TMS 9901 INTERFACE

FIGURE 7 - TMS 9980-TMS 9901 INTERFACE

# 2.7 PIN DEFINITIONS

Table 5 defines the TMS 9901 pin assignments and describes the function of each pin.

TABLE 5

TMS 9901 PIN ASSIGNMENTS AND FUNCTIONS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIN                                                                                                                                      | I/O                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                              |             |                        |                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|-------------|------------------------|-------------------------------------|

| INTREQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                                                                                       | оит                                        | INTERRUPT Request. When active (low)                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           | -                            |             |                        |                                     |

| ZEROTECHÓ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          | 001                                        | INTREQ indicates that an enabled interrupt                                                                                                                                                                                                                                                                                                                                                                                    | RST1                                                                      | 1 [                          |             | 40                     | Vcc                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |                                            | has been received. INTREQ will stay active                                                                                                                                                                                                                                                                                                                                                                                    | CRUOUT                                                                    | 2                            | U           | 39                     | SO                                  |

| No. of the last of |                                                                                                                                          | Limite's                                   | until all enabled interrupt inputs are re-                                                                                                                                                                                                                                                                                                                                                                                    | CRUCLK                                                                    | 3                            |             | 38                     | PO                                  |

| in put t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 199                                                                                                                                      | UTL BOX                                    | moved.                                                                                                                                                                                                                                                                                                                                                                                                                        | CRUIN                                                                     | 4 🗍                          |             | 37                     | P1                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                               | CE                                                                        | 5                            |             | 36                     | S1                                  |

| C0 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                                                                                                                                       | OUT                                        | Interrupt Code lines. ICO-IC3 output the                                                                                                                                                                                                                                                                                                                                                                                      | INTE                                                                      | 6                            |             | 35                     | S2                                  |

| C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                                                                                                       | OUT                                        | binary code corresponding to the highest                                                                                                                                                                                                                                                                                                                                                                                      | INTS                                                                      | 7                            |             | 34                     | INT7/P15                            |

| C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13                                                                                                                                       | OUT                                        | priority enabled interrupt. If no enabled                                                                                                                                                                                                                                                                                                                                                                                     | INT4                                                                      | 8                            |             | 33                     | INT8/P14                            |

| C3 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                                                                                                       | OUT                                        | interrupts are active ICO—IC3 = (1,1,1,1).                                                                                                                                                                                                                                                                                                                                                                                    | INT3                                                                      | 9                            |             | 32                     | INT9/P13                            |

| CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                                                                                                        | IN                                         | Chip Enable. When active (low) data may be                                                                                                                                                                                                                                                                                                                                                                                    | $\frac{1}{\phi}$                                                          |                              |             | 31                     | INT10/P12                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          | 140                                        | transferred through the CRU interface to                                                                                                                                                                                                                                                                                                                                                                                      | INTREQ                                                                    |                              |             | 30                     | INT11/P11                           |

| The to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er ber 1                                                                                                                                 | THREE                                      | the CPU. CE has no effect on the interrupt                                                                                                                                                                                                                                                                                                                                                                                    | IC3                                                                       | -                            |             | 29                     | INT12/P10                           |

| The second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | a la n                                                                                                                                   | 4                                          | control section.                                                                                                                                                                                                                                                                                                                                                                                                              | IC2                                                                       | 7                            |             | 28                     | INT13/P9                            |

| 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                                                                                       | IN                                         | Address select lines. The data bit being                                                                                                                                                                                                                                                                                                                                                                                      | IC1                                                                       | 7                            |             | 27                     | INT 14/P8                           |

| 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                                                                       | IN                                         | accessed by the CRU interface is specified                                                                                                                                                                                                                                                                                                                                                                                    | 100                                                                       | 7                            |             | 26                     | P2                                  |