# 2. Pin Functions

This section discusses the TMS34010 pin functions. Section 2.1 contains a TMS34010 pinout, summarizes the pin functions, and associates the pins with various categories. Section 2.2 through Section 2.6 present details concerning the individual categories. Contents of this section include:

| Sectio |                                     | Page |

|--------|-------------------------------------|------|

| 2.1    | Pinout and Pin Descriptions         |      |

|        | Host Interface Bus Signals          |      |

|        | Local Memory Interface Signals      |      |

| 2.4    | Video Timing Signals                | 2-9  |

|        | Hold and Emulator Interface Signals |      |

|        | Power, Ground, and Reset Signals    |      |

### 2.1 Pinout and Pin Descriptions

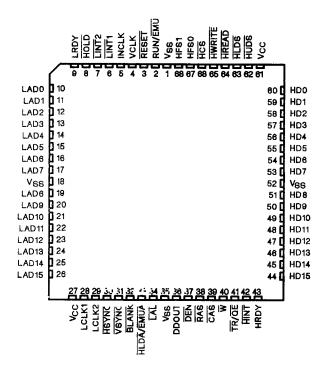

The TMS34010 is packaged as a 68-pin plastic leaded chip carrier (PLCC). Figure 2-1 shows a pinout of the TMS34010 processor. Mechanical information is contained in Appendix A.

Figure 2-1. TMS34010 Pinout (Top View)

The TMS34010's 68 pins are divided among several interfaces:

| Host interface               |        | 25 pins |

|------------------------------|--------|---------|

| Local memory interface       |        | 29 pins |

| Video timing interface       |        | 4 pins  |

| Hold and emulator interfaces |        | 3 pins  |

| Power and reset              |        | 7 pins  |

|                              | Total: | 68 pins |

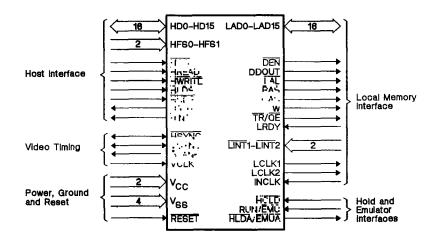

Figure 2-2 associates the pins with the TMS34010's major interfaces. Table 2-1 summarizes the pin functions at each interface.

Figure 2-2. TMS34010 Major Interfaces

| Name                    | Pin                     | I/O                | Description                                    |  |  |  |

|-------------------------|-------------------------|--------------------|------------------------------------------------|--|--|--|

|                         | Host Interface Bus Pins |                    |                                                |  |  |  |

| HCS                     | 66                      |                    | Host chip select                               |  |  |  |

| HD0-HD15                | 44-51,53-60             | 1/0                | Host bidirectiona! data bus                    |  |  |  |

| HF\$0,HF\$1             | 67,68                   | 1                  | Host function select                           |  |  |  |

| <u>111.1 -</u>          | 42                      | 0                  | Host interrupt request                         |  |  |  |

| HLDS                    | 63                      | I                  | Host lower data select                         |  |  |  |

| HUDS                    | 62                      | I                  | Host upper data select                         |  |  |  |

| HRDY                    | 43                      | 0                  | Host ready                                     |  |  |  |

| HIR- AD                 | 64                      | 1                  | Host read strobe                               |  |  |  |

| FARTE                   | 65                      | 1                  | Host write strobe                              |  |  |  |

|                         | Le                      | ocal int           | erface Bus Pins                                |  |  |  |

| RAS                     | 38                      | 0                  | Local row-address strobe                       |  |  |  |

| CAS                     | 39                      | 0                  | Local column-address strobe                    |  |  |  |

| DDOUT                   | 36                      | 0                  | Local data direction out                       |  |  |  |

| <u>ren</u>              | 37                      | 0                  | Local data enable                              |  |  |  |

| LAD0-LAD15              | 10-17,19-26             | 1/0                | Local address/data bus                         |  |  |  |

| LAL                     | 34                      | 0                  | Local address latched                          |  |  |  |

| LCLK1,LCLK2             | 28,29                   | 0                  | Local output clocks                            |  |  |  |

| LINT1, LINT2            | 6,7                     | 1                  | Local interrupt request pins                   |  |  |  |

| LRDY                    | 9                       | I                  | Local ready                                    |  |  |  |

| TR/QE                   | 41                      | 0                  | Local shift-register transfer or output enable |  |  |  |

| $\overline{\mathbf{W}}$ | 40                      | 0                  | Local write strobe                             |  |  |  |

| INCLK                   | 5                       | I                  | input clock                                    |  |  |  |

|                         |                         | Hold a             | ind Emulation                                  |  |  |  |

| HOLD                    | 8                       | l I                | Hold request                                   |  |  |  |

| RUN, EMU                | 2                       | I                  | Run/Emulate                                    |  |  |  |

| HLDA, : JA              | 33                      | 0                  | Hold acknowledge or emulate acknowledge        |  |  |  |

|                         |                         | Video <sup>-</sup> | Fiming Signals                                 |  |  |  |

| BLANK                   | 32                      | 0                  | Blanking                                       |  |  |  |

| HSYNC                   | 30                      | 1/0                | Horizontal sync                                |  |  |  |

| VCLK                    | 4                       | 1                  | Video clock                                    |  |  |  |

| VSYNC                   | 31                      | 1/0                | Vertical sync                                  |  |  |  |

|                         |                         | Mis                | cellaneous                                     |  |  |  |

| 31517                   | 3                       | 1                  | Device reset                                   |  |  |  |

| V <sub>CC</sub>         | 27,61                   |                    | Nominal 5-volt power supply                    |  |  |  |

| V <sub>SS</sub>         | 1,18,35,52              | Ι                  | Ground                                         |  |  |  |

Table 2-1. Pin Descriptions

### 2.2 Host Interface Bus Signals

The host interface pins are used for communication between the TMS34010 and a host processor. Signals output on these pins are assumed to be asynchronous with respect to local clocks LCLK1 and LCLK2. To software running on a host processor, the TMS34010's host interface appears as a peripheral device containing a block of four 16-bit registers. Table 2-2 describes the host interface pins. TMS34010 host interface operation is discussed in Section 10. Host interface registers are discussed in Section 6.

| Signal    | I/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HCS       |     | Host Chip Select. HCS is driven active low to enable access to the 16-bit host interface register that is selected by HFSO $\mathbf{u} \cdot \mathbf{i}$ HFS1. During the low-to-high transition of RESET, the level on the $\mathbf{i} \cdot \mathbf{i}$ input determines whether the TMS34010 is halted (if HCS is high), or begins immediately executing its reset service routine (if HCS is low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| HFS0-HFS1 | 1   | <i>Host Function Select.</i> The two function select pins determine which of the four 16-bit host interface registers is selected during a read or write cycle that is initiated by the host processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|           |     | HFS1 HFS0RegisterDescription00HSTADRLLSBs of pointer address01HSTADRHMSBs of pointer address10HSTDATAData buffer register11HSTCTLControl register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| · · · D   | I   | Host Read Strobe. $\cdots : \cdots : \overline{D}$ is driven active low during a read cycle that is initiated by the host processor. This enables the $\cdots :$ ents of the selected host interface register to be $c : \cdots : \overline{O}$ on HDO-HD15. $\overline{I} : \cdots : \overline{D}$ should not be active low at the same time that $\overline{I} : \cdots : \overline{E}$ is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| HWRITE    |     | Host Write Strobe. HWRITE is driven active low during a write cycle that is initiated by the host processor. This enables the contents of HDO-HD15 to be written to the selected $\cdot \cdot$ interface register. HWRITE should not be active low at the same time that $\frac{1}{2}$ $\cdot$ $\frac{1}{2}$ $1$ |  |  |

| HLDS      | I   | Host Lower Data Select. HLDS is driven active low during a read or write cycle that is initiated by the host. This enables the lower byte (bits 0-7) of the selected host interface register to be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| HUDS      | I   | Host Upper Data Select. HUDS is driven active low during a read or write cycle that is initiated by the host processor. This enables the upper byte (bits 8–15) of the selected host interface register to be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| HRDY      | 0   | Host Ready. HRDY indicates when the TMS34010 is ready to complete a read<br>or write cycle that is initiated by the host. Except during an access of a host<br>interface register, HRDY is always high. HRDY will be driven low if the host<br>processor attempts to initiate an access of a host interface register before the<br>TMS34010 has had sufficient time to complete all processing resulting from an<br>access initiated previously by the host. HRDY always goes low briefly at the<br>start of a HSTCTL register access. When HRDY is driven low, the host must<br>wait to complete the access until HRDY is again driven high. While HCS is<br>high, HRDY is driven high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

Table 2-2. Host Interface Signals

| Signal   | I/O | Description                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HINT     | 0   | Host Interrupt Request. The $\overrightarrow{\text{Int}}$ pin follows the INTOUT bit in the HSTCTL register. HINT is typically used to transmit interrupt requests from the TMS34010 to the host processor. When INTOUT is set to 1 by the TMS34010, HINT is driven active low. HINT remains active low until the host writes a 0 to INTOUT, at which time HINT becomes inactive high. |

| HD0-HD15 | 1/0 | Host Bidirectional Data Bus. The host data pins, HD0-HD15, form a bidirec-<br>tional 16-bit bus. This bus is used to transfer data between the selected 16-bit<br>host interface register and the host processor. HD0 is the LSB and HD15 is the<br>MSB.                                                                                                                               |

| Table 2-2. | Host | Interface | Signals | (Concluded) |

|------------|------|-----------|---------|-------------|

|------------|------|-----------|---------|-------------|

# 2.3 Local Memory Interface Signals

The TMS34010 uses the local bus interface pins to communicate with external memory and with external memory-mapped I/O devices. The signals at this interface are used directly to control DRAMs (dynamic RAMs) and VRAMs (video RAMs). Local memory interface operation is discussed in Section 11.

| Signal  | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u></u> | 0   | Local Data Enable. L+F: is an active-low output. It is used to drive the ac-<br>tive-low output-enable inputs on the bidirectional transceivers (such as the<br>74ALS245), which are used to buffer data input and output on the<br>LADO-LAD15 pins. External buffering may be required on the LADO-LAD15<br>pins when the TMS34010 is interfaced to a large number of local memory<br>devices.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DDOUT   | 0   | Local Data Direction Out. DDOUT drives the direction control inputs on the bidirectional transceivers (such as the 74ALS245), which are used to buffer data input and output on the LADO-LAD15 pins. External buffering may be required on the LADO-LAD15 pins when the TMS34010 is interfaced to a large number of local memory devices. During write cycles, DDOUT isn high to enable data to be output from the LADO-LAD15 pins while IT! is driven active low. During read cycles, DDOUT goes low to enable data to be input to the LADO-LAD15 pins while DEN is driven active low. At all other times, DDOUT remains driven to the default high level.                                                                                                                                                             |

| LAL     | . 0 | Local Address Latched. An external latch can use the high-to-low transition of LAL to capture the column address from the LAD0-LAD15 pins. When a transparent latch such as a 74ALS373 is used, the address remains latched as long as LAL remains active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RAS     | 0   | Local Row Address Strobe. The $\overline{RAS}$ output is used to drive the $\overline{RAS}$ inputs of DRAMs and VRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CAS     | 0   | Local Column Address Strobe. The $\overline{CAS}$ output is used to drive the $\overline{CAS}$ inputs of DRAMs and VRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| W       | 0   | Local Write Strobe. The active-low $\overline{W}$ output is used to drive the $\overline{W}$ inputs<br>of DRAMs and VRAMs. $\overline{W}$ can also be used as the active-low write enable<br>to static memories and other devices connected to the TMS34010 local inter-<br>face. During a local memory read cycle, $\overline{W}$ remains inactive high while $\overline{CAS}$<br>is strobed active low. During a local memory write cycle, $\overline{W}$ is strobed active<br>low while $\overline{CAS}$ is low. During shift-register-transfer cycles, the state of $\overline{W}$<br>indicates whether the transfer is from shift register to memory ( $\overline{W}$ is low) or<br>memory to shift register ( $\overline{W}$ is high). At all other times, $\overline{W}$ is driven to the<br>default high level. |

| TR/QE   | 0   | Local Shift Register Transfer or Output Enable. This pin connects directly to the $\overline{TR}/\overline{OE}$ (or $\overline{DT}/\overline{OE}$ ) pin of a VRAM. During local memory read cycles, $\overline{TR}/\overline{OE}$ functions as an active-low output enable to gate data from memory to the LAD0-LAD15 pins. During VRAM shift-register-transfer cycles, $\overline{TR}/\overline{OE}$ is driven active low during the high-to-low transition of $\overline{RAS}$ .                                                                                                                                                                                                                                                                                                                                      |

| INCLK   | 1   | <i>Input Clock</i> . INCLK is the input clock used to generate the LCLK1 and LCLK2 outputs, to which all processor functions in the TMS34010 are synchronous. A separate input clock, VCLK, controls the video timing registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 2-3. Local Bus Interface Signals

| Signal      | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCLK1,LCLK2 | 0   | Local Output Clocks. These two output clocks, 90 degrees out of phase with each other, provide convenient synchronous control of external circuitry to the TMS34010's internal timing. All signals output from the TMS34010, with the exception of the CRT timing signals, are synchronous to these clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LRDY        | 1   | Local Ready. LRDY is driven low by external circuitry to inhibit the TMS34010 from completing a local memory cycle it has initiated. While LRDY remains low, the TMS34010 continues to wait. When LRDY is again driven high, the TMS34010 completes the cycle. While LRDY is low, the TMS34010 generates internal wait states in increments of one full LCLK1 cycle in duration. LRDY can be driven low to extend local memory read and write cycles, shift-register-transfer cycles, and DRAM refresh cycles. During internal cycles, the TMS34010 ignores LRDY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LINT1,LINT2 | I   | Local Interrupt Request Pins. Interrupt requests from external devices are tran-<br>smitted to the TMS34010 on the LINT1 and LINT2 pins. Each pin activates the<br>request for one of two external interrupt request levels. An external device<br>generates an interrupt request by driving the appropriate interrupt request pin<br>to its active-low state. The pin should remain active low until the TMS34010<br>has recognized the request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |     | Transitions on the two interrupt request pins are assumed to be asynchronous with respect to local clocks LCLK1 and LCLK2; the signals on these pins are synchronized internally before being used internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |     | The local interrupt pins are reconfigured during emulation and testing to per-<br>form special functions that are described in a separate emulation and testing<br>document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LADO-LAD15  | 1/0 | Local Address/Data Bus. LADO-LAD15 form the local multiplexed address/<br>data bus. At the start of a memory cycle, two addresses (row and column) are<br>output on LADO-LAD15. During a read cycle, data are input on LADO-LAD15<br>during the latter part of the cycle. During a write cycle, data are output on<br>LADO-LAD15 during the latter part of the cycle. LAD0 is the LSB, and LAD15<br>is the MSB. During the time the row address is output on LADO-LAD14, status<br>bit RF is output on LAD15. RF is active low at the start of a DRAM-refresh<br>cycle (either RAS-only or CAS-before-RAS). During the time that the column<br>address is output on LAD0-LAD13, status bits TR and IAQ are output on<br>LAD15 and LAD14, respectively. IAQ is active high during a read cycle in<br>which the TMS34010 fetches an instruction word from the local memory.<br>During all other cycles, IAQ is inactive low. TR is active low during shift-<br>register-transfer cycles. (The level output on LAD14 during the high-to-low<br>transition of CAS is always the same as the level output on TR/QE during the<br>high-to-low transition of RAS.) |

Table 2-3. Local Bus Interface Signals (Concluded)

Note: The system designer must ensure that LRDY is not held low for so long that the TMS34010 is prevented from performing the necessary number of DRAM refresh cycles or is prevented from refreshing the display by performing a VRAM memory-to-shift-register cycle during horizontal retrace.

## 2.4 Video Timing Signals

The video timing signals (BLANK, HSYNC, and VSYNC) are used to control the horizontal and vertical sweep rates of the video monitor. They are also used to synchronize the display on the monitor to video data output from the VRAMs. Section 9 discusses video timing and screen refresh operations.

| Signal | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i /NC  | 1/0 | Horizontal Sync. HSYNC is the horizontal sync signal used to control external video circuitry. It is programmed as either an input or an output by means of two control bits in the DPYCTL register. When configured as an output, the active-low horizontal sync signal is generated by the TMS34010's on-chip video timers. When configured as an input, the TMS34010 synchronizes its video timers to ·· rnally-generated horizontal sync pulses. Immediately following reset, HS·*. is configured as an input.                                                                                            |

| VSYNC  | 1/0 | Vertical Sync. VSYNC is the vertical sync signal used to control external video circuitry. It is programmed as either an input or an output by means of a control bit in the DPYCTL register. When configured as an output, the active-low vertical sync signal is generated by the TMS34010's on-chip video timers. When configured as an input, the TMS34010 synchronizes its video timers to externally-generated vertical sync pulses. Immediately following reset, VSYNC is configured as an input.                                                                                                      |

| BL     | 0   | Blanking. BLANK is a composite blanking signal used to turn off the electron beam of a CRT during both horizontal and vertical retrace intervals. This signal may also be used to control the starting and stopping of the VRAM shift registers.                                                                                                                                                                                                                                                                                                                                                              |

| VCLK   | 1   | Video Clock. VCLK is derived from the dot clock of the external video system<br>and is used internally to denter the TMS34010's video timing logic. The signals<br>output at the BLANK, Hi r':C, and VSYNC pins are synchronous to VCLK.<br>VCLK is not required to have any timing relationship with respect to INCLK; that<br>is, VCLK and INCLK can be asynchronous. In order to read HCOUNT and<br>VCOUNT registers reliably, VCLK should be held high during the read. In sys-<br>tems which do not use the video timing registers or require automatic screen<br>refreshing, VCLK can be strapped high. |

| Table 2-4. | Video | Timing | Signals |

|------------|-------|--------|---------|

|------------|-------|--------|---------|

**Note:** During factory testing, the HSYNC and VSYNC pins are configured to scan data in and out of the two internal shift register scan paths.

## 2.5 Hold and Emulator Interface Signals

The TMS34010 hold interface permits other devices to request and be granted control of the local interface bus.

The emulator interface is used to control the TMS34010 when it is used for emulation. The RUN/EMU pin may remain unconnected in nonemulation applications.

| Signal  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD    | 1   | Hold Request. The HOLD pin is driven active low by an external device to signal a request that the TMS34010 release ownership of the local memory bus. Once the TMS34010 has acknowledged the hold request via a hold acknowledge signal, the external device assumes ownership of the bus. The device must continue to assert its hold request until it has released the bus. |

| HLDA :A | 0   | Hold Acknowledge and Emulate Acknowledge. The HLDA I II A pin is mul-<br>tiplexed between two functions – acknowledgment of hold requests and ac-<br>knowledgment of emulation requests. The hold acknowledge signal (HLDA)<br>is output during r                                                                                                                              |

| RUN/EMU | 1   | Run/Emulate. This pin is defined as a no-connect during normal system oper-<br>ation. The RUN/EMU pin should <i>not</i> be pulled low except i ing factor testing<br>or chip emulation. An internal pull-up load permits RUN                                                                                                                                                   |

Table 2-5. Hold and Emulator Interface Signals

#### 2.6 Power, Ground, and Reset Signals

Six TMS34010 pins are dedicated to ground and power supply. Section 8 provides more details about RESET.

| Table 2-6. Po | ower, Ground, | and Rese | t Signals |

|---------------|---------------|----------|-----------|

|---------------|---------------|----------|-----------|

| Signal | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc    | 1   | V <sub>CC</sub> (2 pins). Two +5-volt power supply inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VSS    | 1   | V <sub>SS</sub> (4 pins). Four electrical ground inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R.     | 1   | Reset. F.: is pulled low to reset the device during normal operation.   While RESET is asserted low, the internal registers of the TMS34010 are set to an initial known state, and all output and bidirectional pins are driven either to inactive levels or to high impedance. The behavior of the TMS34010 chip following reset deperent on the level of the HCS input just prior to the low-to-high transition of P: ET. If HCS is low, the GSP begins executing the instructions pointer to by the reset vector. If HCS is high, the GSP is halted until a host processor writes a 0 to the HLT bit in the HSTCTL register.   Transitions on the RESET pin are assumed to be asynchronous with respect to local clocks LCLK1 and LCLK2; the signal input on this pin is synchronized internally before it is used internally.   During factory testing or chip emulation, RESET is used in conjunction with RUN/EMU, HOLD, LINT1, and LINT2 to configure in TMS34010 into the required test or emulation mode. As long as RUN/THS34010 into the required for normal system operation. |