General Information

# Data Transmission and Control Circuits 2

Display Drivers 3

Peripheral Drivers/Power Actuators

4

1

Mechanical Data 5

Explanation of Logic Symbols

6

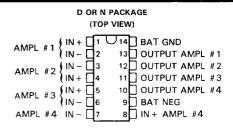

# DS3680I QUAD TELEPHONE RELAY DRIVER

D2758, MARCH 1986-REVISED MARCH 1990

- Designed for 52-V Battery Operation

- 50-mA Output Current Capability

- Input Compatible with TTL and CMOS

- High Common-Mode Input Voltage Range

- Very Low Input Current

- Fail-Safe Disconnect Feature

- Built-In Output Clamp Diode

- Direct Replacement for National DS3680 and Fairchild µA3680

#### description

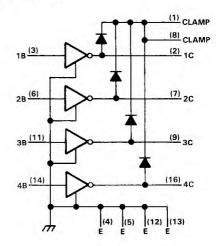

The DS3680I telephone relay driver is a monolithic integrated circuit designed to interface -48-V relay systems to TTL or other systems in telephone applications. It is capable of sourcing up to 50 mA from standard -52-V battery power. To reduce the effects of noise and IR drop between logic ground and battery ground, these drivers are designed to operate with a common-mode input range of  $\pm 20$  V referenced to battery ground. The common-mode input voltages for the four drivers can be different, so a wide range of input elements can be accommodated. The high-impedance inputs are compatible with positive TTL and CMOS levels or negative logic levels. A clamp network is included in the driver outputs to limit high-voltage transients generated by the relay coil during switching. The complementary inputs ensure that the driver output will be "off" as a fail-safe condition when either output is open.

The DS3680I is characterized for operation from -40°C to 85°C.

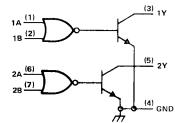

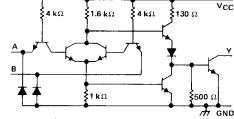

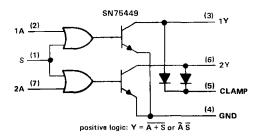

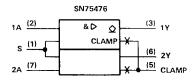

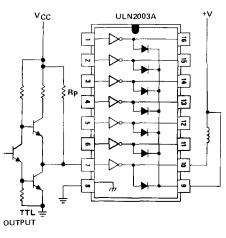

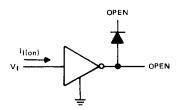

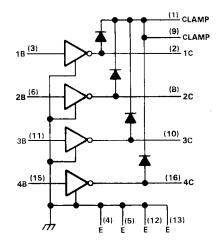

#### symbol (each driver)

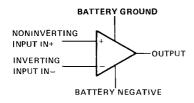

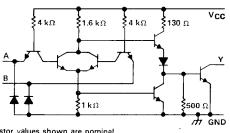

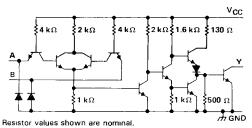

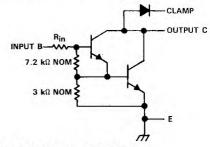

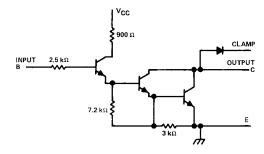

#### schematic diagram (each driver)

All resistor values shown are nominal.

### DS36801 QUAD TELEPHONE RELAY DRIVER

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range at BAT NEG, VB_ (see Note 1)                   |

|---------------------------------------------------------------------|

| Input voltage range with respect to BAT NEG                         |

| Differential input voltage, V <sub>ID</sub> (see Note 2) $\pm 20$ V |

| Output current: resistive load                                      |

| inductive load                                                      |

| Inductive output load                                               |

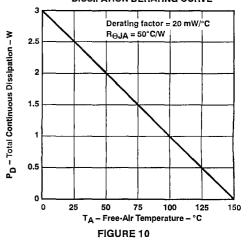

| Continuous total power dissipation                                  |

| Operating free-air temperature range, TA40 °C to 85 °C              |

| Storage temperature range                                           |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds        |

NOTES: 1. All voltages are with respect to the BAT GND terminal unless otherwise specified.

2. Differential input voltages are at the noninverting input terminal IN + with respect to the inverting input terminal IN -.

| PACKAGE | $T_A \le 25 ^{\circ}C$<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70 °C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------|------------------------------------------------|----------------------------------------|---------------------------------------|

| D       | 950 mW                                 | 7.6 mW/°C                                      | 608 mW                                 | 494 mW                                |

| N       | 1150 mW                                | 9.2 mW/°C                                      | 736 mW                                 | 598 mW                                |

#### DISSIPATION RATING TABLE

#### recommended operating conditions

|                                             | MiN   | MAX  | UNIT |

|---------------------------------------------|-------|------|------|

| Supply voltage, V <sub>B</sub> _            | - 10  | - 60 | V    |

| Input voltage, either input                 | -20†  | 20   | V    |

| High-level differential input voltage, VIDH | 2     | 20   | V    |

| Low-level differential input voltage, VIDL  | - 20† | 0.8  | V    |

| Operating free-air temperature, TA          | -40   | 85   | °C   |

<sup>†</sup>The algebraic convention, in which the less positive (more negative) limit is designated minimum, is used in this data sheet for input voltage levels.

# electrical characteristics over recommended operating free-air temperature range, $V_{B-} = -52 V$ (unless otherwise noted)

|                    | PARAMETER                            | TEST CON                | DITIONS                 | MIN | TYP <sup>‡</sup> | MAX   | UNIT |

|--------------------|--------------------------------------|-------------------------|-------------------------|-----|------------------|-------|------|

| tu.                | High-level input current (into IN +) | $V_{ID} = 2 V$          |                         |     | 40               | 100   |      |

| ĥН                 | nigh-level input cohent (into in +)  | V <sub>ID</sub> = 7 V   |                         |     | 375              | 1000  | μA   |

|                    | Low-level input current (into IN+)   | V <sub>ID</sub> = 0.4 V | •                       |     | 0.01             | 5     |      |

| ΙL                 |                                      | V <sub>ID</sub> = −7 V  |                         |     | - 1              | - 1   | μA   |

| VO(on)             | On-state output voltage              | $I_0 = -50 \text{ mA},$ | V <sub>ID</sub> = 2 V   |     | - 1.6            |       | V    |

| 10                 | Off state output surrent             |                         | V <sub>ID</sub> = 0.8 V |     | -2               |       |      |

| O(off)             | Off-state output current             | $V_0 = V_{B-}$          | Inputs open             |     | -2               | -1.1  | μA   |

| IR                 | Clamp diode reverse current          | $V_0 = 0$               |                         |     | 2                | 100   | μA   |

| Voк                | Output clamp voltage                 | $I_0 = 50 \text{ mA}$   |                         |     | 0.9              | 1.2   | v    |

| VOK                | Suppr clamp voltage                  | $I_0 = -50 \text{ mA},$ | $V_{B-} = 0$            |     | -0.9             | - 1.2 | v    |

| I <sub>B(on)</sub> | On-state battery current             | All drivers on          |                         |     | - 2              | -4.4  | mA   |

| lB(off)            | Off-state battery current            | All drivers off         |                         |     | - 1              | - 100 | μA   |

<sup>‡</sup>All typical values are at  $T_A = 25 \,^{\circ}C$ .

### DS3680I QUAD TELEPHONE RELAY DRIVER

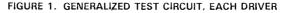

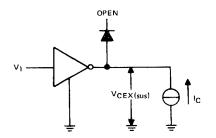

# switching characteristics $V_{B-} = -52 V$ , $T_A = 25 °C$

| PARAMETER                      | TEST COND        | TIONS               | MIN | ТҮР | MAX | UNIT |

|--------------------------------|------------------|---------------------|-----|-----|-----|------|

| t <sub>on</sub> Turn-on time   | VID = 3-V pulse, | $R_L = 1 k\Omega$ , |     | • 1 | 10  | μs   |

| t <sub>off</sub> Turn-off time | L = 1 H,         | See Figure 2        |     | 1   | 10  | μs   |

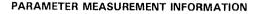

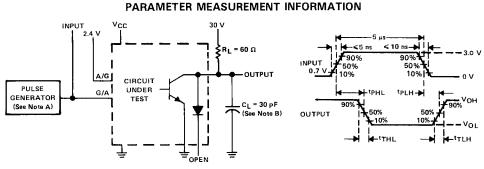

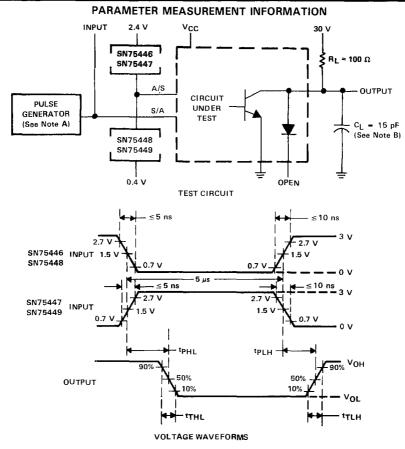

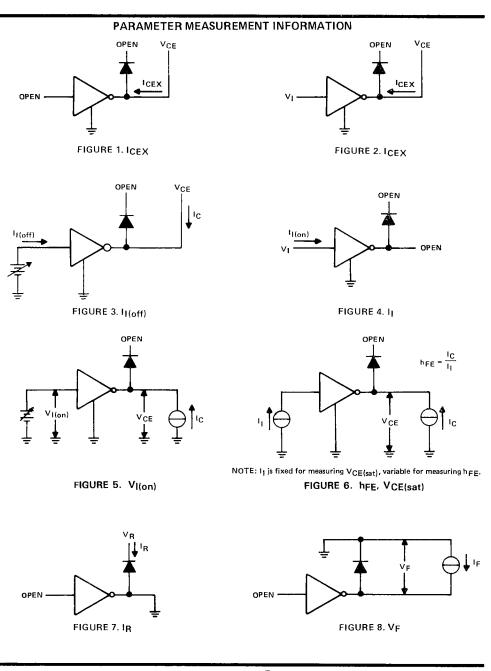

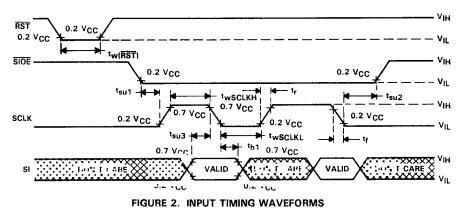

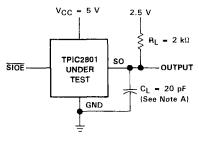

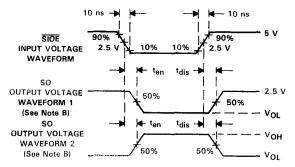

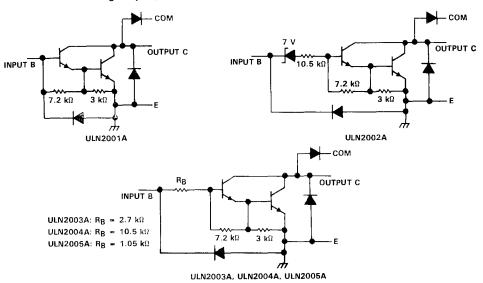

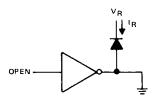

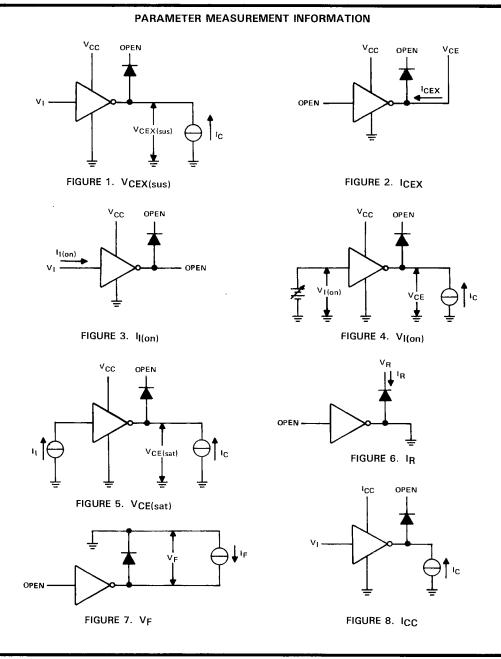

### PARAMETER MEASUREMENT INFORMATION

# DS3680I QUAD TELEPHONE RELAY DRIVER

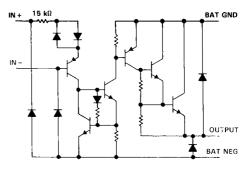

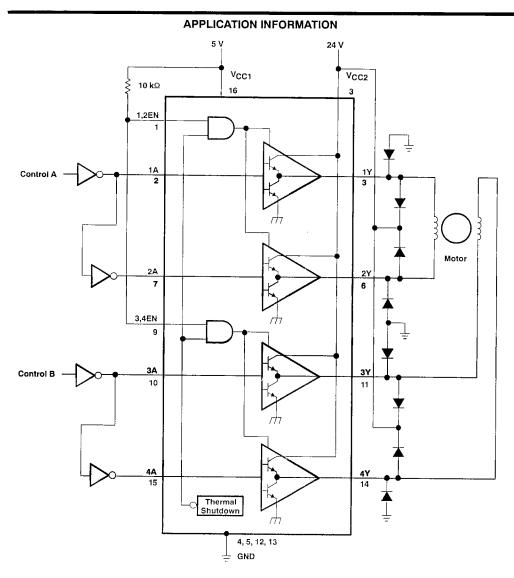

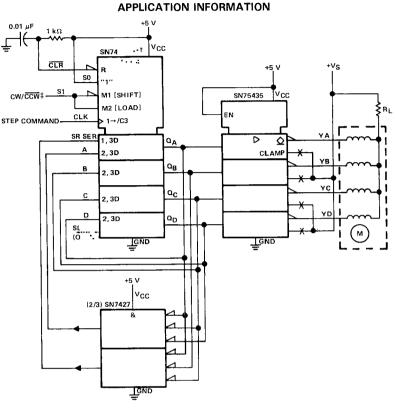

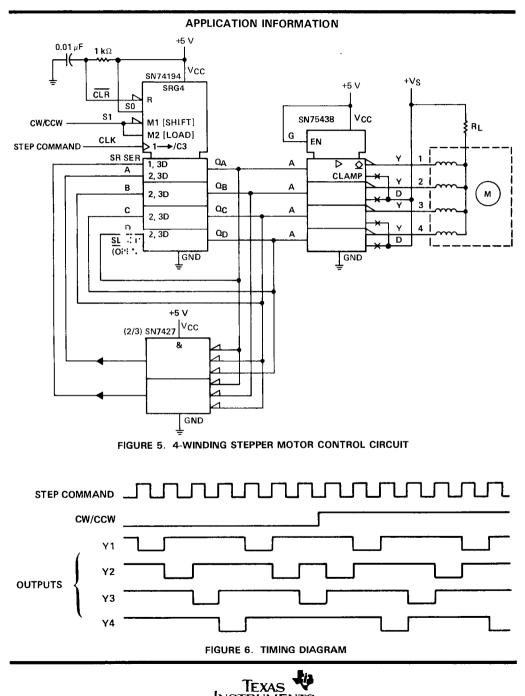

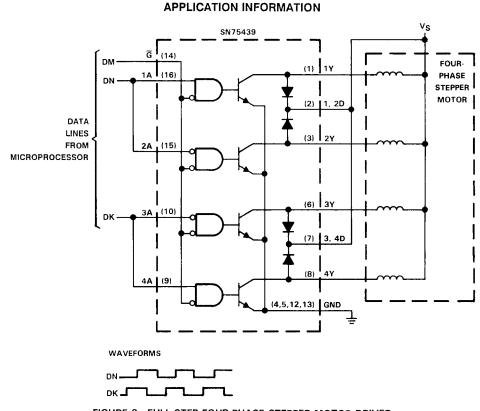

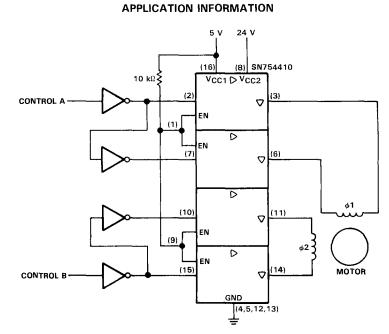

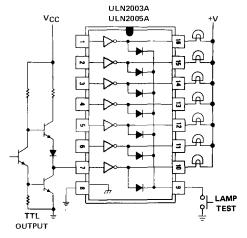

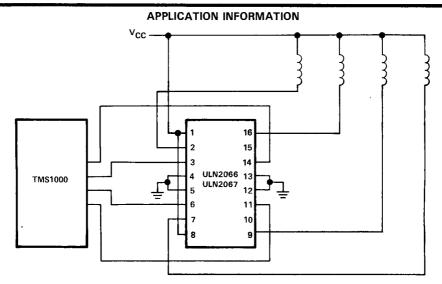

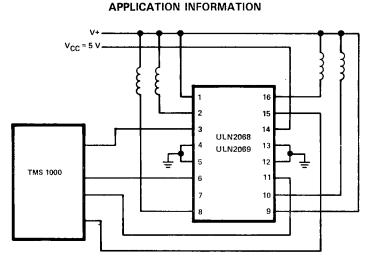

### **APPLICATION INFORMATION**

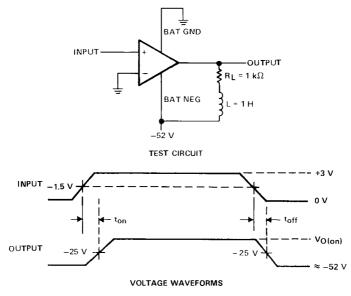

FIGURE 3. RELAY DRIVER

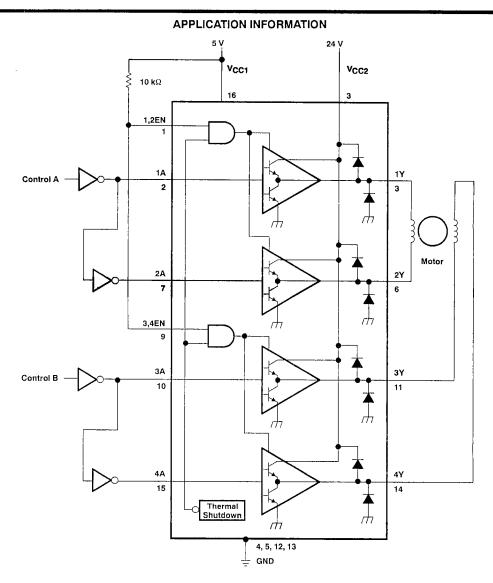

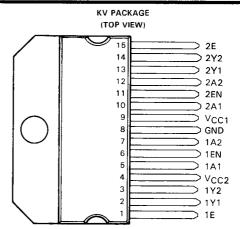

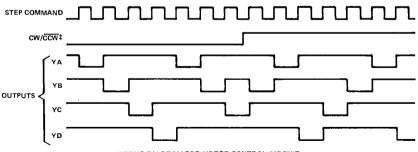

# L293 QUADRUPLE HALF-H DRIVER

D2942, SEPTEMBER 1986-REVISED MAY 1990

- 1-A Output Current Capability Per Driver

- Pulsed Current 2-A Driver

- Wide Supply Voltage Range: 4.5 V to 36 V

- Separate Input-Logic Supply

- NE Package Designed for Heat Sinking

- Thermal Shutdown

- Internal ESD Protection

- High-Noise-Immunity Inputs

- Functional Replacement for SGS L293

#### description

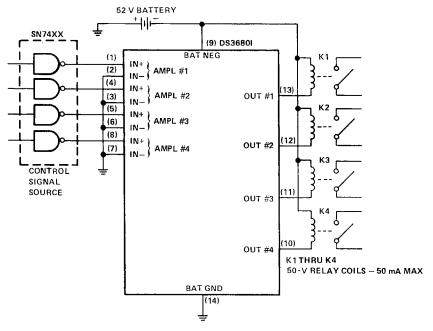

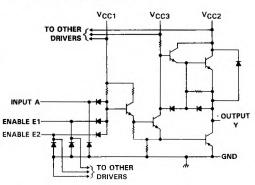

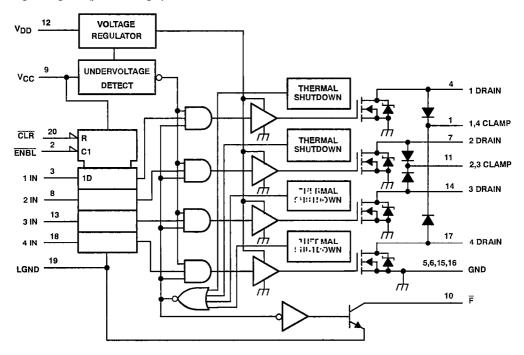

The L293 is a quadruple high-current half-H driver designed to provide bidirectional drive currents of up to one ampere at voltages from 4.5 V to 36 V. It is designed to drive inductive loads such as relays, solenoids, dc and bipolar stepping motors, as well as other highcurrent/high-voltage loads in positive-supply applications.

<sup>†</sup>In the thermal shutdown mode, the output is in the high-impedance state regardless of the input levels.

(off)

Z =

high-impedance

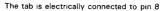

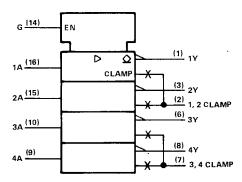

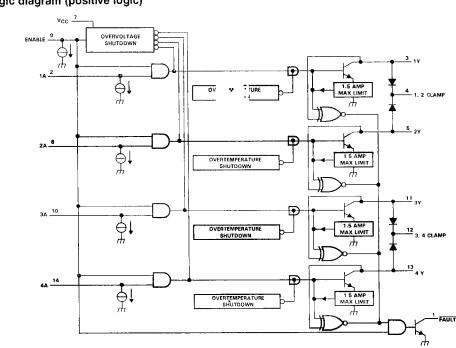

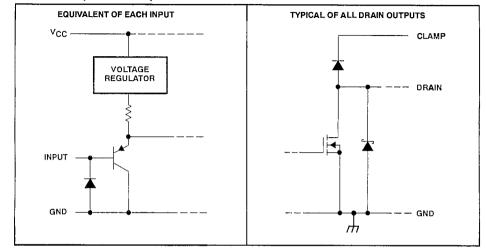

All inputs are TTL-compatible. Each output is a complete totem-pole drive circuit with a Darlington transistor sink and a psuedo-Darlington source. Drivers are enabled in pairs with drivers 1 and 2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN. When an enable input is high, the associated drivers are enabled and their outputs are active and in phase with their inputs. When the enable input is low, those drivers are disabled and their outputs are off and in a high-impedance state. With the proper data inputs, each pair of drivers form a full-H (or bridge) reversible drive suitable for solenoid or motor applications.

External high-speed output clamp diodes should be used for inductive transient suppression. A V<sub>CC1</sub> terminal , separate from V<sub>CC2</sub>, is provided for the logic inputs to minimize device power dissipation.

The L293 is designed for operation from 0°C to 70°C.

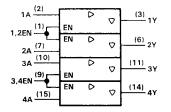

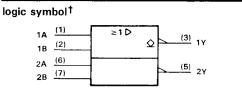

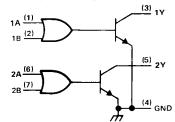

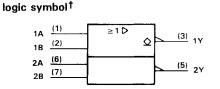

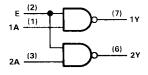

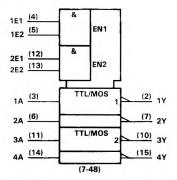

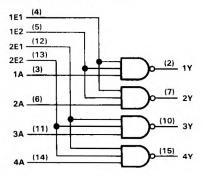

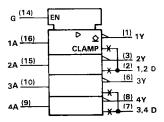

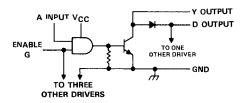

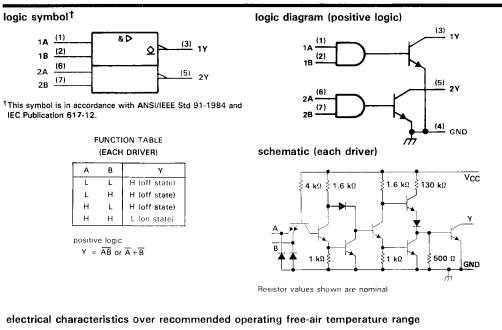

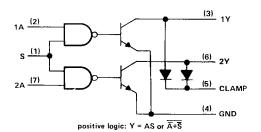

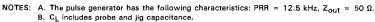

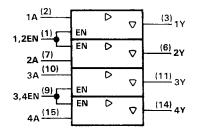

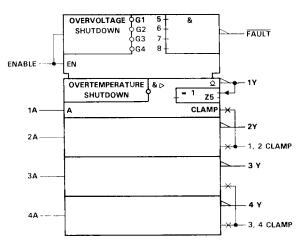

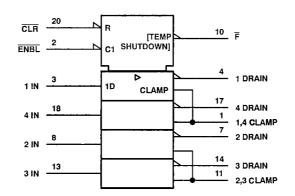

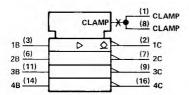

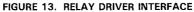

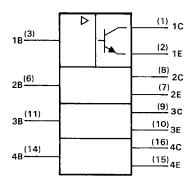

### logic symbol<sup>‡</sup>

\*This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

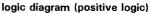

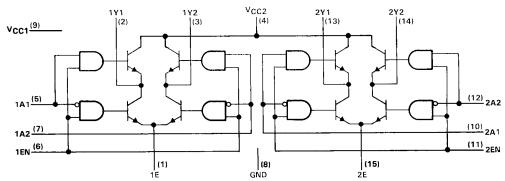

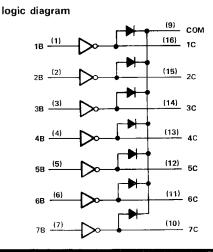

logic diagram

PRODUCTION DATA documents contain information ct···· s of publication date. Products conform to sg····tions per the terms of Texas Instruments st...c., warrenty. Production processing daas not necessarily include testing of all parameters.

Copyright © 1990, Texas Instruments Incorporated

## L293 QUADRUPLE HALF-H DRIVER

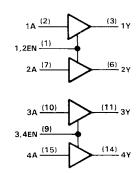

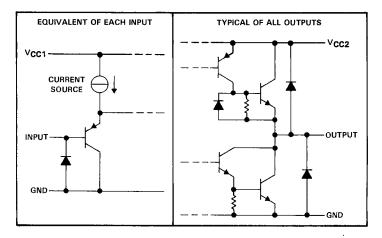

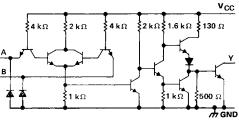

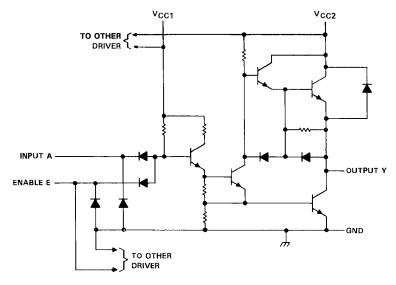

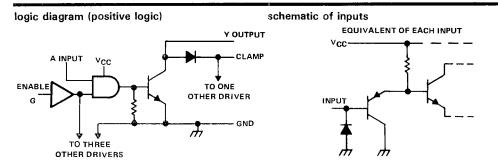

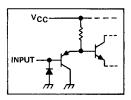

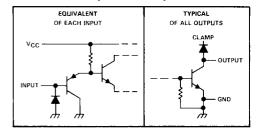

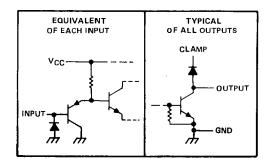

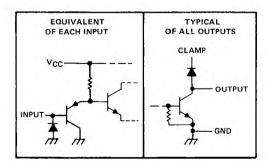

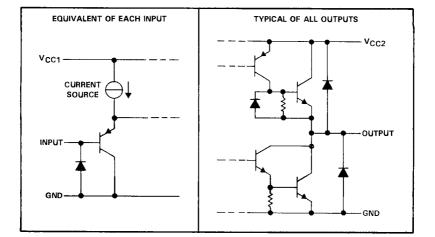

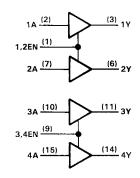

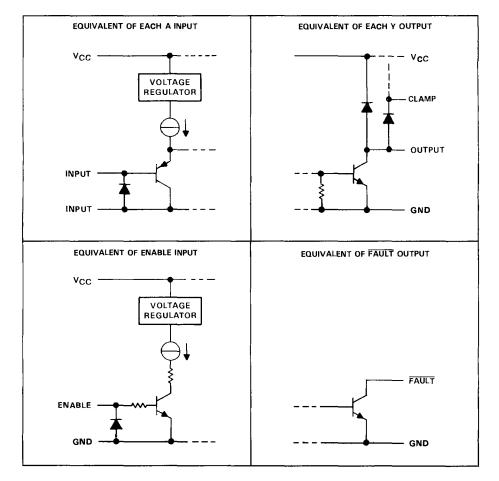

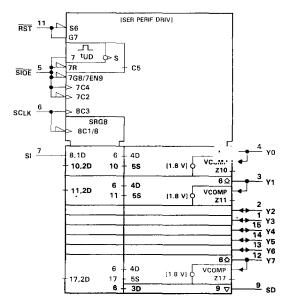

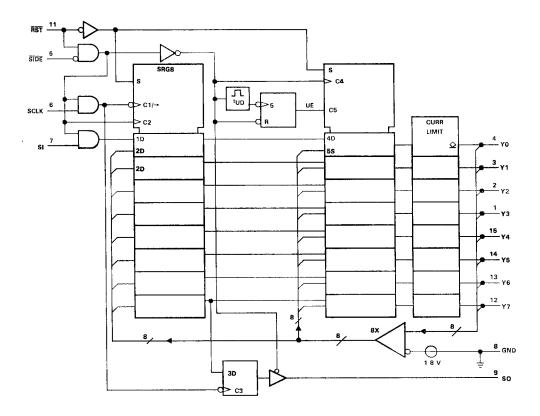

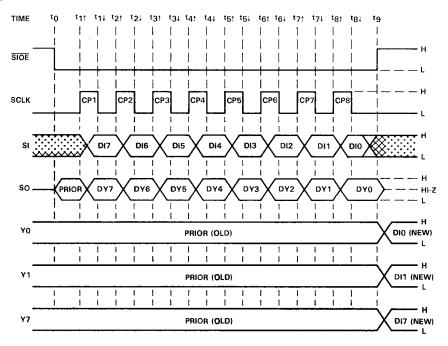

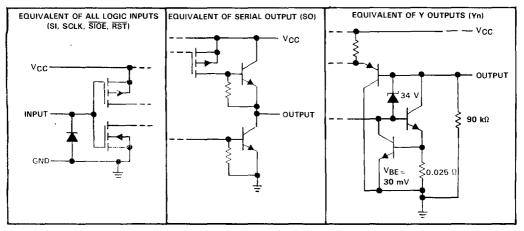

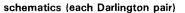

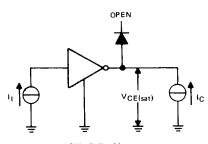

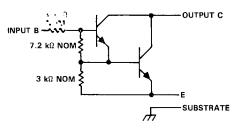

schematics of inputs and outputs

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Logic supply voltage, V <sub>CC1</sub> (see Note 1)                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|

| Input voltage                                                                                                                   |

| Output voltage range                                                                                                            |

| Peak output current (nonrepetitive, t $\leq$ 5 ms) ±2 A                                                                         |

| Continuous output current ±1 A                                                                                                  |

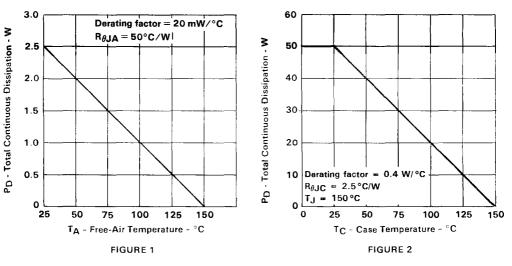

| Continuous total dissipation at (or below) 25 °C free-air temperature<br>(see Notes 2 and 3)                                    |

| Continuous total dissipation at 80 °C case temperature (see Note 3)                                                             |

| Operating case or virtual junction temperature range                                                                            |

| Storage temperature range       -65°C to 150°C         Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds       260°C |

NOTES: 1. All voltage values are with respect to the network ground terminal.

2. For operation above 25 °C free-air temperature, derate linearly at the rate of 16.6 mW/ °C.

3. For operation above 25 °C case temperature, derate linearly at the rate of 71.4 mW/°C. Due to variations in individual device electrical characteristics and thermal resistance, the built-in thermal overload protection may be activated at power levels slightly above or below the rated dissipation.

### recommended operating conditions

|                                                             | MIN   | MAX | UNIT |

|-------------------------------------------------------------|-------|-----|------|

| Logic supply voltage, VCC1                                  | 4.5   | 7   | v    |

| Output supply voltage, V <sub>CC2</sub>                     |       | 36  | v    |

| High-level input voltage, V <sub>IH</sub> $V_{CC1} \le 7 V$ | 2.3   |     |      |

| $V_{CC1} \ge 7 V$                                           | 2.3   | 7   | v    |

| Low-level input voltage, VIL                                | -0.3† | 1.5 | v    |

| Operating free-air temperature, TA                          | 0     | 70  | °C   |

<sup>†</sup>The algebraic convention, in which the least positive (most negative) designated minimum, is used in this data sheet for logic voltage levels.

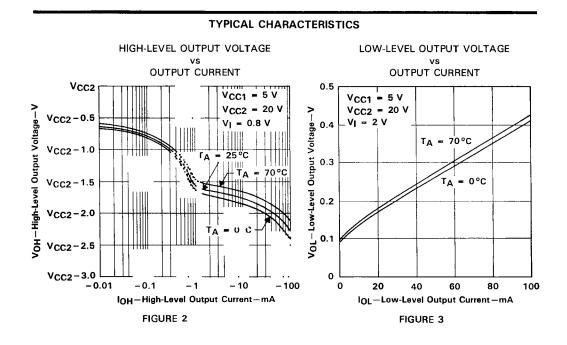

|      | PARAMETER                   |                       | TEST CONDITIONS               | MIN                   | TYP                   | MAX   | UNIT |

|------|-----------------------------|-----------------------|-------------------------------|-----------------------|-----------------------|-------|------|

| VOH  | High-level output voltage   | 1он = -               | 1 A                           | V <sub>CC2</sub> -1.8 | V <sub>CC2</sub> -1.4 |       | V    |

| VOL  | Low-level output voltage    | I <sub>OL</sub> = 1 / | A                             |                       | 1.2                   | 1.8   | V    |

| •    | A A                         | <u> </u>              |                               |                       | 0.2                   | 100   | μA   |

| ЧH   | High-level input current EN | Vi = 7 V              |                               |                       | 0.2                   | ± 10  |      |

|      | A                           |                       |                               |                       | - 3                   | - 10  | μA   |

| μL   | Low-level input current EN  | VI = 0                |                               |                       | - 2                   | - 100 |      |

|      |                             |                       | All outputs at high level     |                       | 13                    | 22    |      |

| ICC1 | Logic supply current        | io = 0                | All outputs at low level      |                       | 35                    | 60    | mA   |

|      |                             |                       | All outputs at high impedance |                       | 8                     | 24    |      |

|      |                             |                       | All outputs at high level     |                       | 14                    | 24    |      |

| ICC2 | Output supply current       | l <sub>0</sub> = 0    | All outputs at low level      |                       | 2                     | 6     | mA   |

|      |                             | _                     | All outputs at high impedance |                       | 2                     | 4     | 1    |

### electrical characteristics, $V_{CC1} = 5 V$ , $V_{CC2} = 24 V$ , $T_A = 25 °C$

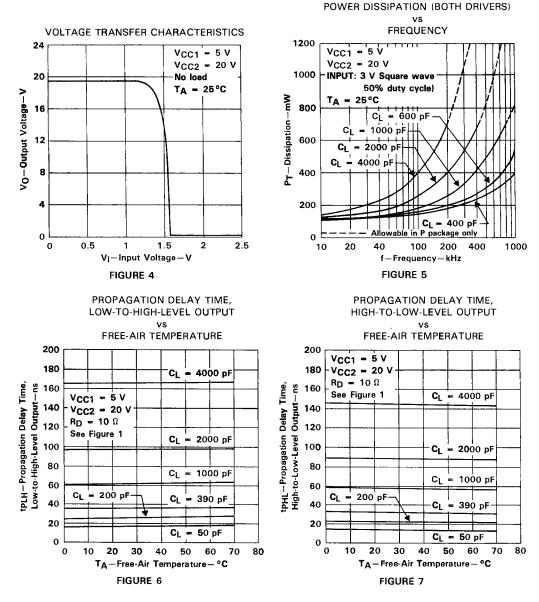

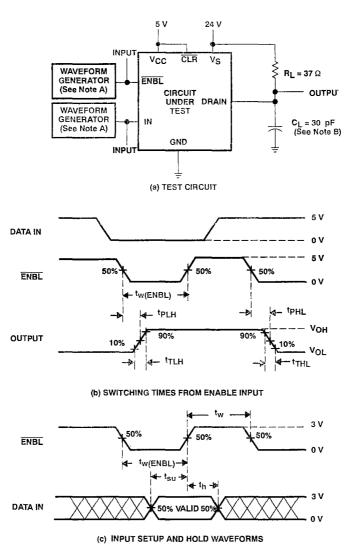

# switching characteristics, V<sub>CC1</sub> = 5 V, V<sub>CC2</sub> = 24 V, T<sub>A</sub> = $25 \,^{\circ}$ C

|                  | PARAMETER                                                     | TEST CONDITIONS        | MIN | түр | MAX | UNIT |

|------------------|---------------------------------------------------------------|------------------------|-----|-----|-----|------|

| <b>t</b> PLH     | Propagation delay time, low-to-high-level output from A input |                        |     | 800 |     | ns   |

| tPHL             | Propagation delay time, high-to-low-level output from A input | $C_L = 30 \text{ pF},$ |     | 400 |     | ns   |

| t <sub>TLH</sub> | Transition time, low-to-high-level output                     | See Figure 1           |     | 300 |     | ns   |

| <b>t</b> THL     | Transition time, high-to-low-level output                     |                        |     | 300 |     | ns   |

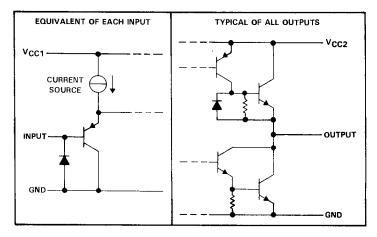

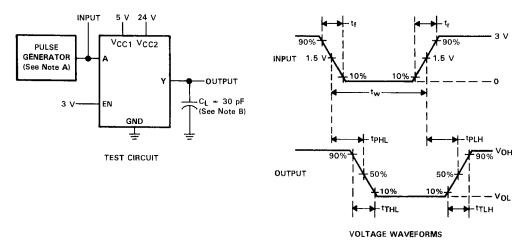

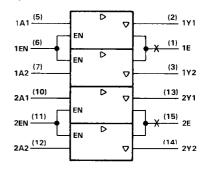

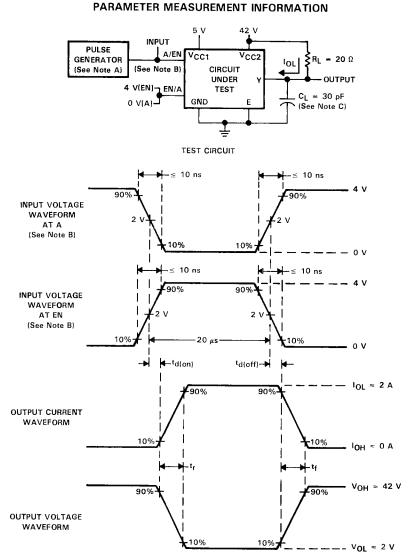

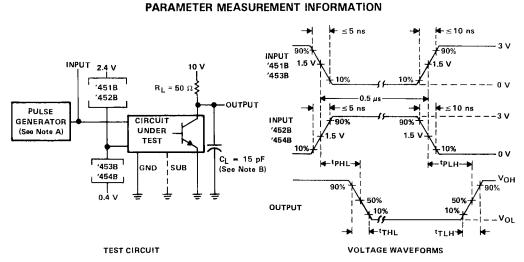

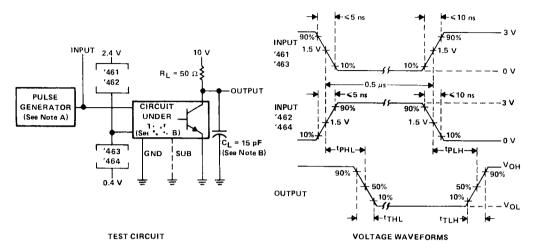

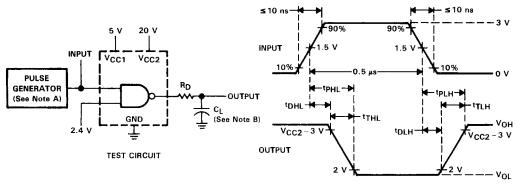

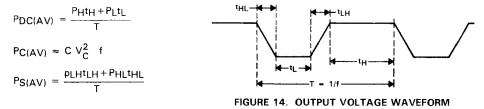

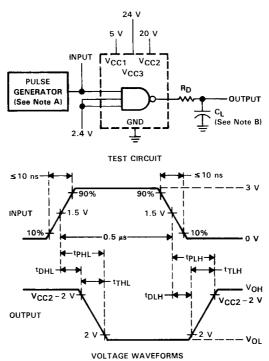

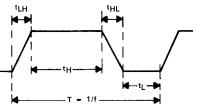

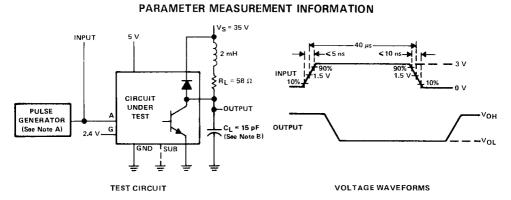

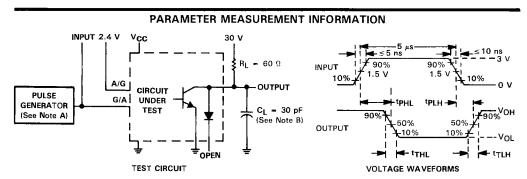

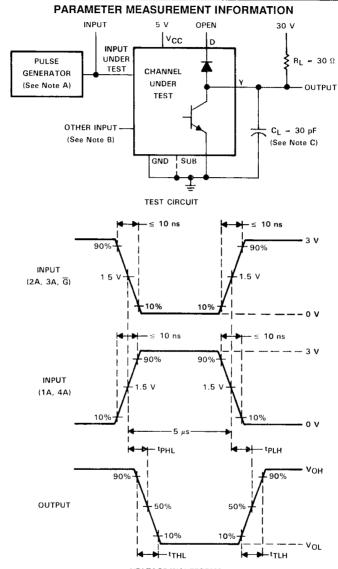

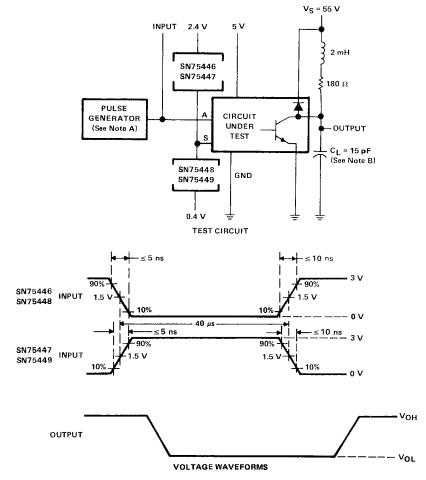

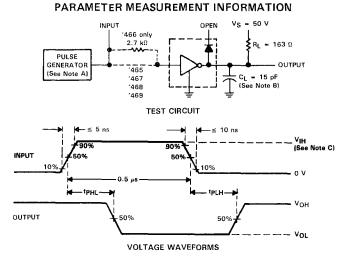

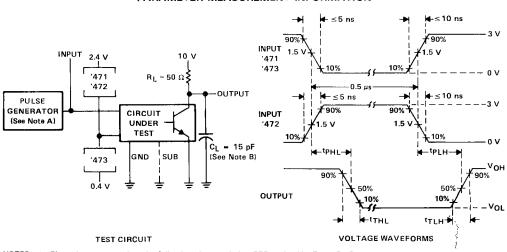

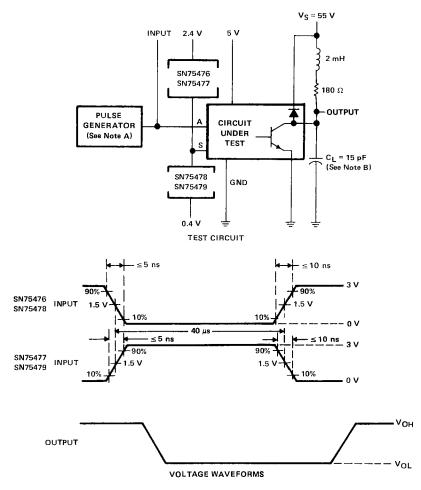

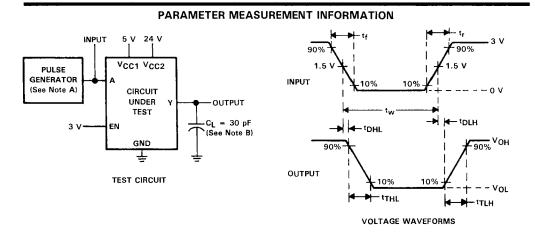

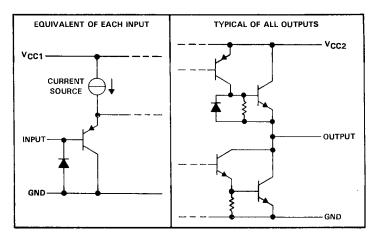

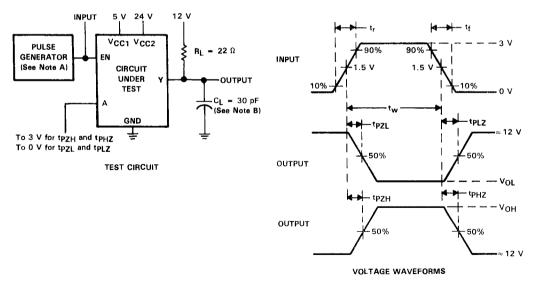

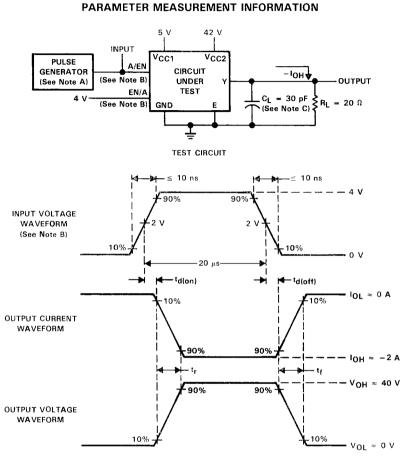

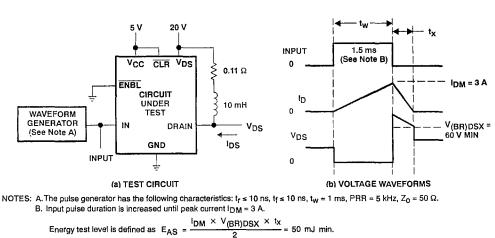

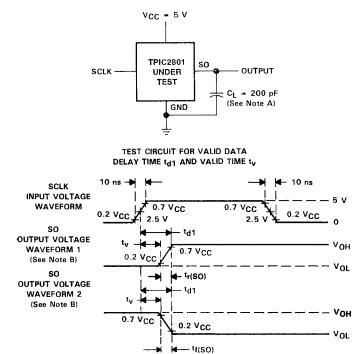

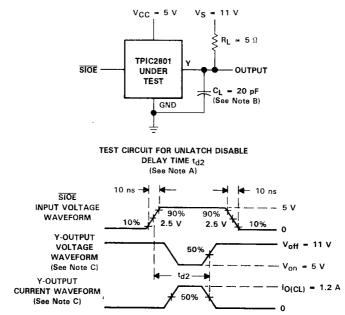

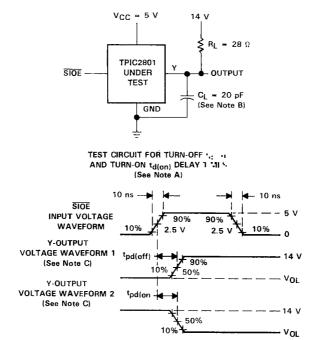

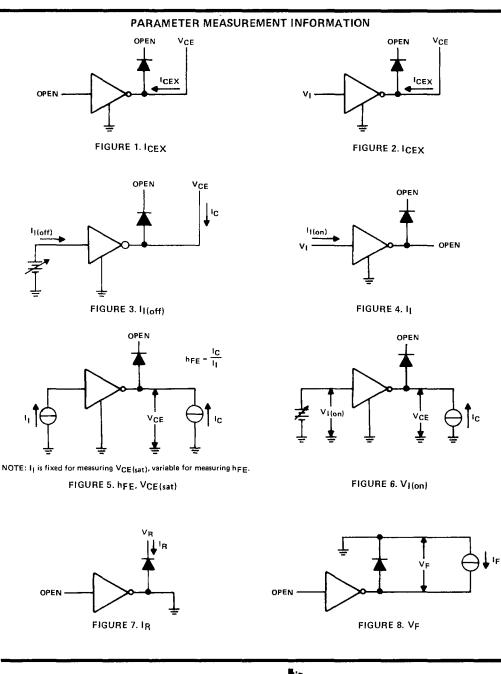

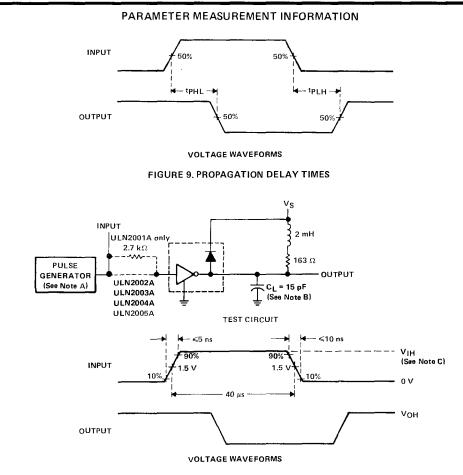

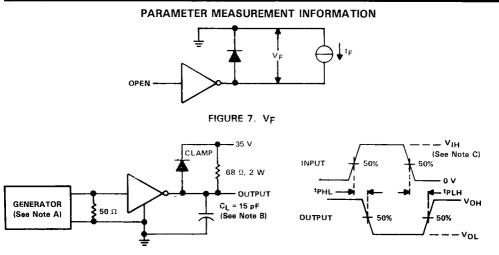

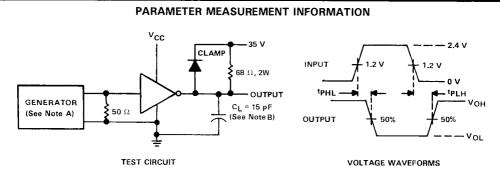

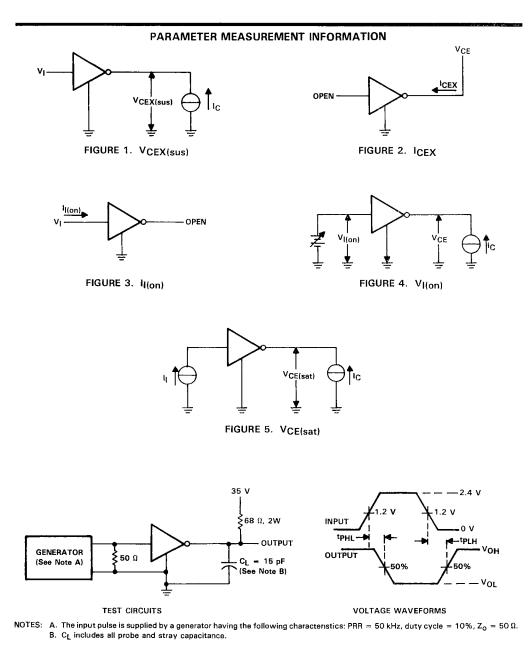

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. The pulse generator has the following characteristics:  $t_r \le 10$  ns,  $t_f \le 10$  ns,  $t_W = 10 \ \mu$ s, PRR = 5 kHz,  $Z_0 = 50 \ \Omega$ . B. CL includes probe and jig capacitance.

### FIGURE 1. SWITCHING TIMES

# L293 QUADRUPLE HALF-H DRIVER

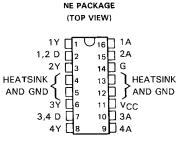

# L293D QUADRUPLE HALF-H DRIVER

D3511, SEPTEMBER 19B6-REVISED MAY 1990

- 600-mA Output Current Capability Per Driver

- Pulsed Current 1.2-A Per Driver

- Output Clamp Diodes for Inductive Transient Suppression

- Wide Supply Voltage Range: 4.5 V to 36 V

- Separate Input-Logic Supply

- Thermal Shutdown

- Internal ESD Protection

- High-Noise-Immunity Inputs

- Functional Replacement for SGS L293D

#### description

The L293D is a quadruple high-current half-H driver designed to provide bidirectional drive currents of up to 600 mA at voltages from 4.5 V to 36 V. It is designed to drive inductive loads such as relays, solenoids, dc and bipolar stepping motors, as well as other high-current/high-voltage loads in positive-supply applications.

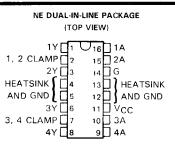

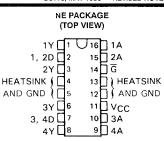

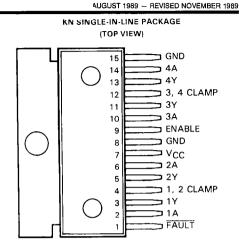

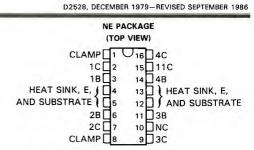

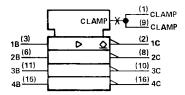

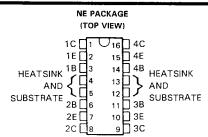

NE PACKAGE (TOP VIEW) 1,2EN 🗍 1 J<sub>16</sub> VCC1 1A [ 2 15 🗍 4A 1Y 🗍 3 14 4Y HEATSINK AND 13 HEATSINK AND 12 GROUND GROUND ) 15 2Y 16 11 3Y 2A 🗍 7 10 🗍 3A 9 3,4EN VCC2 🛛 8

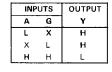

> FUNCTION TABLE (EACH DRIVER)

| INPL                                                       | JTS† | OUTPUT |  |  |  |  |

|------------------------------------------------------------|------|--------|--|--|--|--|

| А                                                          | EN   | Y      |  |  |  |  |

| н                                                          | н    | н      |  |  |  |  |

| L                                                          | н    | L      |  |  |  |  |

| X                                                          | L    | z      |  |  |  |  |

| X L Z<br>H = high-level<br>L = low-level<br>X = irrelevant |      |        |  |  |  |  |

Z = high-impedance (off)

<sup>†</sup>In the thermal shutdown mode, the output is in the high-impedance state regardless of the input levels.

All inputs are TTL-compatible. Each output is a complete totem-pole drive circuit with a Darlington transistor sink and a psuedo-Darlington source. Drivers are enabled in pairs with drivers 1 and 2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN. When an enable input is high, the associated drivers are enabled and their outputs are active and in phase with their inputs. When the enable input is low, those drivers are disabled and their outputs are off and in a high-impedance state. With the proper data inputs, each pair of drivers form a full-H (or bridge) reversible drive suitable for solenoid or motor applications.

A VCC1 terminal, separate from VCC2, is provided for the logic inputs to minimize device power dissipation.

The L293D is designed for operation from 0°C to 70°C.

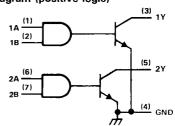

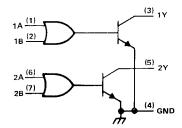

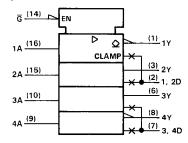

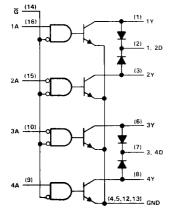

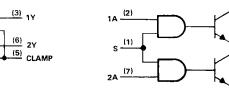

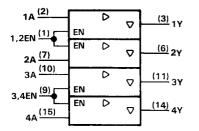

#### logic symbol<sup>‡</sup>

<sup>‡</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

logic diagram

Copyright © 1990, Texas Instruments Incorporated

### L293D QUADRUPLE HALF-H DRIVER

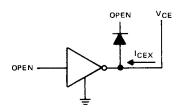

#### schematics of inputs and outputs

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Logic supply voltage, V <sub>CC1</sub> (see Note 1)                      |

|--------------------------------------------------------------------------|

| Output supply voltage, V <sub>CC2</sub>                                  |

| Input voltage                                                            |

| Output voltage range $$                                                  |

| Peak output current (nonrepetitive, t $\leq 100 \ \mu s$ ) $\pm 1.2 \ A$ |

| Continuous output current ±600 mA                                        |

| Continuous total dissipation at (or below) 25 °C free-air temperature    |

| (see Notes 2 and 3)                                                      |

| Continuous total dissipation at 80 °C case temperature (see Note 3)      |

| Operating case or virtual junction temperature range                     |

| Storage temperature range                                                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds             |

NOTES: 1. All voltage values are with respect to the network ground terminal.

- 2. For operation above 25 °C free-air temperature, derate linearly at the rate of 16.6 mW/ °C.

- 3. For operation above 25 °C case temperature, derate linearly at the rate of 71.4 mW/°C. Due to variations in individual device electrical characteristics and thermal resistance, the built-in thermal overload protection may be activated at power levels slightly above or below the rated dissipation.

### recommended operating conditions

|                                                                                                                                                    | MIN               | MAX  | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|

| Logic supply voltage, V <sub>CC1</sub>                                                                                                             | 4.5               | 7    | V    |

| Output supply voltage, V <sub>CC2</sub>                                                                                                            | V <sub>CC1</sub>  | 36   | v    |

| V <sub>CC1</sub> $\leq$ 7 V                                                                                                                        | 2.3               | VCC1 |      |

| utput supply voltage, $V_{CC2}$<br>igh-level input voltage, $V_{IH} = \frac{V_{CC1} \le 7 V}{V_{CC1} \ge 7 V}$<br>pw-level input voltage, $V_{IL}$ | 2.3               | 7    | v    |

| Low-level input voltage, VIL                                                                                                                       | -0.3 <sup>†</sup> | 1.5  | v    |

| Operating free-air temperature, TA                                                                                                                 | 0                 | 70   | °C   |

<sup>†</sup>The algebraic convention, in which the least positive (most negative) designated minimum, is used in this data sheet for logic voltage levels.

|      | PARAMETER                           |         |                                | TEST CONDITIONS               | MIN                   | TYP                     | MAX   | UNIT |     |  |

|------|-------------------------------------|---------|--------------------------------|-------------------------------|-----------------------|-------------------------|-------|------|-----|--|

| ∨он  | High-level output voltage           |         | I <sub>OH</sub> = -0.6 A       |                               | V <sub>CC2</sub> -1.8 | 3 V <sub>CC2</sub> -1.4 |       | V    |     |  |

| VOL  | Low-level output voltage            |         | $I_{OL} = 0.6 \text{ A}$       |                               |                       | 1.2                     | 1.8   | V    |     |  |

| ∨окн | High-level output clamp v           | /oltage | IOK = 0.6 A                    |                               |                       | V <sub>CC2</sub> +1.3   |       | V    |     |  |

| VOKL | Low-level output clamp v            | oltage  | $I_{OK} = -0.6 \text{ A}$      |                               |                       | 1.3                     |       | v    |     |  |

| 1    | IH High-level input current A<br>EN |         | Alish Isost is such as a fille |                               | VI = 7 V              |                         |       | 0.2  | 100 |  |

| чн   |                                     |         | VI = 7 V                       |                               |                       | 0.2                     | ±10   | μA   |     |  |

| L.   | Low lovel innut everent             |         |                                | VI = 0                        |                       | -3                      | - 10  |      |     |  |

| ηĽ   | Low-level input current EN          |         | vi = 0                         |                               |                       | -2                      | - 100 | μA   |     |  |

|      |                                     |         |                                | All outputs at high level     |                       | 13                      | 22    |      |     |  |

| ICC1 | Logic supply current                |         | <b>i</b> <sub>0</sub> = 0      | All outputs at low level      |                       | 35                      | 60    | mA   |     |  |

|      |                                     |         |                                | All outputs at high impedance |                       | 8                       | 24    |      |     |  |

|      |                                     |         |                                | All outputs at high level     |                       | 14                      | 24    |      |     |  |

| ICC2 | Output supply current               |         | i <sub>0</sub> ≂ 0             | All outputs at low level      |                       | 2                       | 6     | mA   |     |  |

|      |                                     |         |                                | All outputs at high impedance |                       | 2                       | 4     |      |     |  |

### electrical characteristics, $V_{CC1} = 5 V$ , $V_{CC2} = 24 V$ , $T_A = 25 °C$

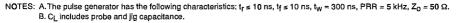

### switching characteristics, V<sub>CC1</sub> = 5 V, V<sub>CC2</sub> = 24 V, T<sub>A</sub> = $25^{\circ}$ C

|                  | PARAMETER                                                     | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------------------------------|-------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level output from A input |                         |     | 800 |     | ns   |

| <b>tPHL</b>      | Propagation delay time, high-to-low-level output from A input | C <sub>L</sub> = 30 pF, |     | ÷., |     | ns   |

| tŢLH             | Transition time, low-to-high-level output                     | See Figure 1            |     |     |     | ns   |

| <b>t</b> THL     | Transition time, high-to-low-level output                     |                         |     | 300 |     | ns   |

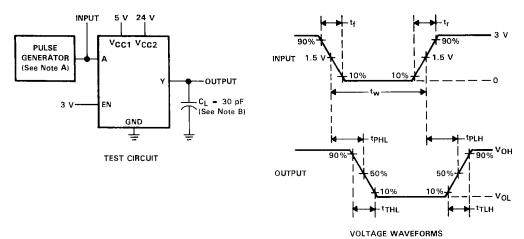

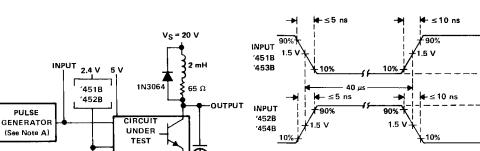

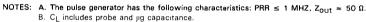

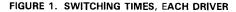

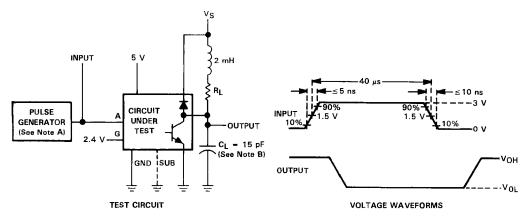

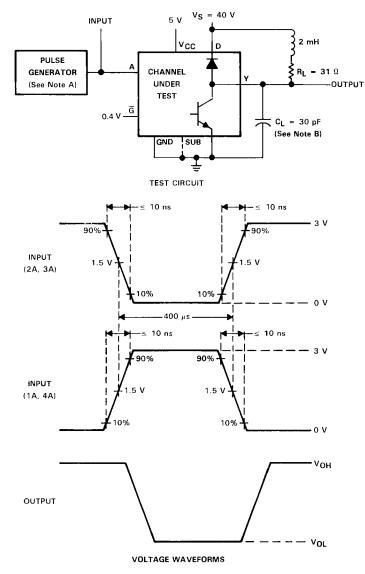

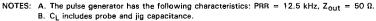

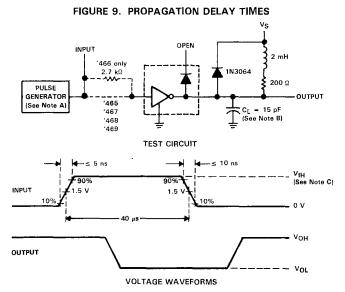

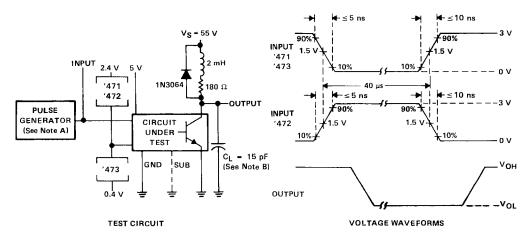

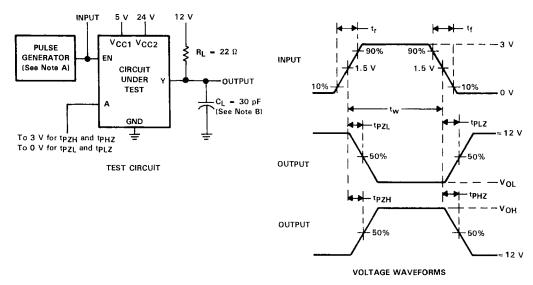

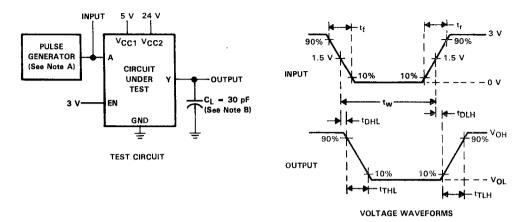

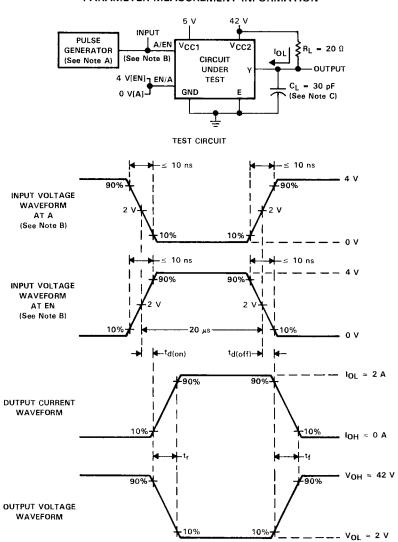

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. The pulse generator has the following characteristics:  $t_r \le 10$  ns,  $t_f \le 10$  ns,  $t_W = 10 \ \mu$ s, PRR = 5 kHz,  $Z_0 = 50 \ \Omega$ . B.  $C_L$  includes probe and jig capacitance.

#### FIGURE 1. SWITCHING TIMES

# L293D QUADRUPLE HALF-H DRIVER

D2942, OCTOBER 1986-REVISED JUNE 1990

- 2-A Output Current Capability per Full-H Driver

- Wide Range of Output Supply Voltage . . . 5 V to 46 V

- Separate Input-Logic Supply Voltage

- Thermal Shutdown

- Internal Electrostatic Discharge Protection

- High Noise Immunity

- Functional Replacement for SGS L298

#### description

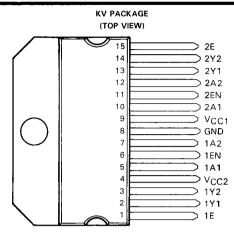

The L298 is a dual high-current full-H driver designed to provide bidirectional drive currents of up to two amperes at voltages from 5 V to 46 V It is designed to drive inductive loads such as relays, solenoids, dc motors, stepping motors, and other high-current or high-voltage loads in positive-supply applications All inputs are TTL compatible Each output (Y) is a complete totempole drive with a Darlington transistor sink and a psuedo-Darlington source. Each full-H driver is enabled separately Outputs 1Y1 and 1Y2 are enabled by 1EN and outputs 2Y1 and 2Y2 are enabled by 2EN. When an EN input is high, the associated channels are active. When an EN input is low, the associated channels are off (i.e., in the high-impedance state)

Each half of the device forms a full-H reversible driver suitable for solenoid or motor applications. The current in each full-H driver can be monitored by connecting a resistor between the sense output terminal 1E and ground and another resistor between sense output terminal 2E and ground.

External high-speed output-clamp diodes should be used for inductive transient suppression. To minimize device power dissipation, a V<sub>CC1</sub> supply voltage, separate from V<sub>CC2</sub>, is provided for the logic inputs

The L298 is designed for operation from 0  $^{\circ}\text{C}$  to 70  $^{\circ}\text{C}$

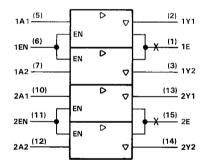

#### logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12

# FUNCTION TABLE

| Γ | INPL | JTS‡ | OUTPUT |

|---|------|------|--------|

| Γ | А    | EN   | Y      |

| Γ | н    | н    | н      |

|   | L    | н    | L      |

|   | х    | L    | z      |

<sup>‡</sup>In the thermal shutdown mode, the outputs are in the high-impedance state regardless of the input levels

- H = high-level

- L = low-level

- X = irrelevant

- Z = high-impedance (off)

Copyright © 1990, Texas Instruments Incorporated

PPDNIICTIO, II'I ocuments centain infermation as o'on date Preducts conferm te taitea..., terms af Texas instruments sistuard warranty Preduction precessing does not necessarily include texting of all paramaters

# L298 DUAL FULL-H DRIVER

#### logic diagram (positive logic) Vcc2 1Y1 1Y2 2Y1 2Y2 (2) (3) (4) (13) (14) V<sub>CC1</sub>(9) (1<u>2)</u> 2A2 1A1(5) 1A2 (7) (<u>10)</u> 2A1 1EN (6) (11) 2EN (1) (8) (15) 1E GND 2E

#### absolute maximum ratings over operating temperature range (unless otherwise noted)

| Logic supply voltage, V <sub>CC1</sub> , (see Note 1)         7 V           Output supply voltage, V <sub>CC2</sub> 50 V           Input voltage range at A or EN, V <sub>1</sub> -0.3 to 7 V           Output voltage range, V <sub>O</sub> -2 V to V <sub>CC2</sub> +2 V           Emitter terminal (1E and 2E) voltage range         -0.5 to 2.3 V |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Emitter terminal (1E and 2E) voltage (nonrepetitive, $t_W \leq 50 \ \mu s$ )                                                                                                                                                                                                                                                                          |

| Peak output current, $I_{OM}$ , (nonrepetitive, $t_W \le 0.1 \text{ ms}$ ) ±3 A                                                                                                                                                                                                                                                                       |

| (repetitive, $t_W \le 10$ ms, duty cycle $\le 80\%$ ) $\pm 2.5$ A                                                                                                                                                                                                                                                                                     |

| Continuous output current, IO ±2 A                                                                                                                                                                                                                                                                                                                    |

| Peak combined output current for each full-H driver (see Note 2)                                                                                                                                                                                                                                                                                      |

| (nonrepetitive, $t_W \leq 0.1 \text{ ms}$ ) $\pm 3 \text{ A}$                                                                                                                                                                                                                                                                                         |

| (repetitive, $t_W \le 10$ ms, duty cycle $\le 80\%$ ) $\pm 2.5$ A                                                                                                                                                                                                                                                                                     |

| Continuous combined output current for each full-H driver (see Note 2)                                                                                                                                                                                                                                                                                |

| Continuous dissipation at (or below) 25 °C free-air temperature (see Note 3)                                                                                                                                                                                                                                                                          |

| Continuous dissipation at (or below) 75 °C case temperature (see Note 3)                                                                                                                                                                                                                                                                              |

| Operating free-air, case, or virtual junction temperature range $\dots \dots \dots \dots \dots \dots -40$ °C to 150 °C                                                                                                                                                                                                                                |

| Storage temperature range                                                                                                                                                                                                                                                                                                                             |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                       |

NOTES: 1. All voltage values are with respect to the network ground terminal, unless otherwise noted.

Combined output current applies to each of the two full-H drivers individually. This current is the sum of the currents at outputs 1Y1 and 1Y2 for full-H driver 1 and the sum of the currents at outputs 2Y1 and 2Y2 for full-H driver 2. The full-H drivers may carry the rated combined current simultaneously.

3. For operation above 25°C free-air temperature, derate linearly at the rate of 28.6 mW/°C. For operation above 75°C case temperature, derate linearly at the rate of 333 mW/°C. Due to variations in individual device electrical characteristics and thermal resistance, the built-in thermal overload protection may be activated at power levels slightly above or below the rated dissipation.

#### recommended operating conditions

|                                                      |         | MIN               | MAX                                                                                        | UNIT |  |

|------------------------------------------------------|---------|-------------------|--------------------------------------------------------------------------------------------|------|--|

| Logic supply voltage, V <sub>CC1</sub>               | • • • • | 4.5               | 7                                                                                          | V    |  |

| Output supply voltage, V <sub>CC2</sub>              |         | 5                 | 46                                                                                         | V    |  |

|                                                      |         | -0.5†             | 2                                                                                          |      |  |

| Emitter terminal (1E or 2E) voltage, VE (see Note 4) |         |                   | V <sub>CC1</sub> ~ 3.5                                                                     | V    |  |

|                                                      |         |                   | V <sub>CC2</sub> -4                                                                        |      |  |

|                                                      | A       | 2.3               | $     7     46     2     V_{CC1}-3.5 V_{CC2}-4 V_{CC1} V_{CC2}-2.5 7 V_{CC1} 1.5 \pm 2 40$ |      |  |

|                                                      |         |                   | V <sub>CC2</sub> - 2.5                                                                     | l v  |  |

| High-level input voltage, VIH (see Note 4)           | EN      | 2.3               | 7                                                                                          |      |  |

|                                                      | EN      |                   | V <sub>CC1</sub>                                                                           |      |  |

| Low-level input voltage at A or EN, V <sub>1L</sub>  |         | -0.3 <sup>†</sup> | 1.5                                                                                        | v    |  |

| Output current, IO                                   |         |                   | ±2                                                                                         | A    |  |

| Commutation frequency, fc                            |         | •                 | 40                                                                                         | kHz  |  |

| Operating free-air temperature, TA                   |         | 0                 | 70                                                                                         | °C   |  |

<sup>†</sup>The algebraic convention, in which the least positive (most negative) designated minimum, is used in this data sheet for emitter terminal voltage and logic voltage levels.

NOTE 4: For optimum device performance, the maximum recommended voltage at any A input is 2.5 V lower then V<sub>CC2</sub>, the maximum recommended voltage at any emitter terminal is 3.5 V lower than V<sub>CC1</sub> and the maximum recommended voltage at any emitter terminal is 3.5 V lower than V<sub>CC1</sub> and 4 V lower than V<sub>CC2</sub>.

# electrical characteristics, $V_{CC1} = 5 V$ , $V_{CC2} = 42 V$ , $V_E = 0$ , $T_J = 25 °C$ (unless otherwise noted)

|             | PARAMETER                  |    |                                  | TEST CONDITIONS                                              | S                     | MIN                   | ТҮР                   | MAX                 | UNIT |   |

|-------------|----------------------------|----|----------------------------------|--------------------------------------------------------------|-----------------------|-----------------------|-----------------------|---------------------|------|---|

| ∨он         | High-level output voltage  |    | 10H = -                          | 1 A                                                          |                       | V <sub>CC2</sub> -1.8 | V <sub>CC2</sub> -1.2 |                     | v    |   |

| VOH         | OH High over output tokuge |    | 10H = -3                         | 2 A                                                          |                       | V <sub>CC2</sub> -2.8 | V <sub>CC2</sub> -1.8 |                     | v    |   |

| VOL         | Low-level output voltage   |    | $I_{OL} = 1$                     | 4                                                            |                       |                       | VE+1.2                | V <sub>E</sub> +1.8 | v    |   |

| VOL         | Low-level output voltage   |    | $1_{OL} = 2 I$                   | A                                                            |                       | V <sub>E</sub> +1.7   |                       | V <sub>E</sub> +2.6 | v    |   |

| м.          | Total source plus sink     |    | IOH = -1 A, IOL = 1 A See Note 5 |                                                              | 2.                    |                       | 3.4                   | v                   |      |   |

| Vdrop       | output voltage drop        |    | IOH = -2 A, IOL = 2 A            |                                                              | IOH = -2 A, IOL = 2 A |                       |                       | 3.5                 | 5.2  | v |

| 1           | High-level input current   | Α  | $V_{I} = V_{IH}$                 | $V_{I} = V_{IH}$ $V_{I} = V_{IH} \leq V_{CC1} - 0.6 V$       |                       |                       | 30                    | 100                 |      |   |

| <u> </u> ЧН | High-level input current   | EN | $V_I = V_{IH}$                   |                                                              |                       |                       | 30                    | 100                 | μA   |   |

| ΊL          | Low-level input current    |    | $V_{I} = 0$ to                   | 1.5 V                                                        |                       |                       |                       | - 10                | μA   |   |

|             |                            |    |                                  | All outputs at hig                                           | h level               |                       | 7                     | 12                  |      |   |

| ICC1        | Logic supply current       |    | IO = 0                           | IO = 0 All outputs at low level                              |                       |                       | 24                    | 32                  | mA   |   |

|             |                            |    |                                  | All outputs at high impedance                                |                       |                       | 4                     | 6                   |      |   |

|             |                            |    |                                  | All outputs at high level<br>IO = 0 All outputs at low level |                       |                       | 38                    | 50                  |      |   |

| ICC2        | Output supply current      |    | lo = 0                           |                                                              |                       |                       | 13                    | 20                  | mA   |   |

|             |                            |    |                                  | All outputs at hig                                           | h impedance           |                       |                       | 2                   |      |   |

NOTE 5. The V<sub>drop</sub> specification applies for I<sub>OH</sub> and I<sub>OL</sub> applied simultaneously to different output channels. V<sub>drop</sub> = V<sub>CC2</sub> - V<sub>OH</sub> + V<sub>OL</sub> - V<sub>E</sub>

# L298 DUAL FULL-H DRIVER

# switching characteristics, $V_{CC1} = 5 V$ , $V_{CC2} = 42 V$ , $V_E = 0$ , $T_A = 25 °C$

| PARAMETER                                                | TEST CONDITIONS         | MIN TYP MAX | UNIT |

|----------------------------------------------------------|-------------------------|-------------|------|

| td(on) Source current turn-on delay time from A input    |                         | 2.5         | μS   |

| td(off) Source current turn-off delay time from A input  |                         | 1.7         | μs   |

| tr Source current rise time (turning on)                 | C <sub>L</sub> = 30 pF, | 0.4         | μs   |

| tf Source current fall time (turning off)                | See Figure 1            | 0.2         | μs   |

| td(on) Source current turn-on delay time from EN input   |                         | 2.5         | μS   |

| td(off) Source current turn-off delay time from EN input |                         | 1.7         | μs   |

| td(on) Sink current turn-on delay time from A input      |                         | 1.5         | μs   |

| td(off) Sink current turn-off delay time from A input    |                         | 0.7         | μs   |

| tr Sink current rise time (turning on)                   | CL = 30 pF,             | 0.2         | μs   |

| tf Sink current fall time (turning off)                  | See Figure 2            | 0.2         | μs   |

| td(on) Sink current turn-on delay time from EN input     |                         | 1.5         | μs   |

| td(off) Sink current turn-off delay time from EN input   |                         | 0.7         | μs   |

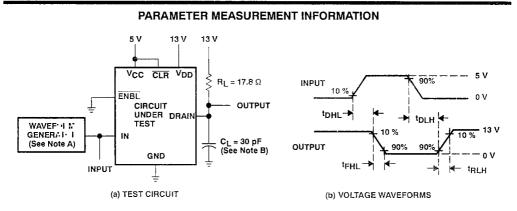

PARAMETER MEASUREMENT INFORMATION

VOLTAGE AND CURRENT WAVEFORMS

- NOTES: A. The pulse generator has the following characteristics: PRR = 2 kHz,  $Z_0 = 50 \ \Omega$ . B. EN is at 4 V if A is used as the switching input. A is at 4 V if EN is the switching input.

- - C. CL includes probe and jig capacitance.

FIGURE 1. SOURCE CURRENT SWITCHING TIMES FROM DATA AND ENABLE INPUTS

VOLTAGE AND CURRENT WAVEFORMS

- NOTES: A. The pulse generator has the following characteristics: PRR = 2 kHz,  $Z_0 = 50 \Omega$ .

- B. EN is at 4 V if A is used as the switching input. A is at 0 V if EN is the switching input.

- C. CL includes probe and jig capacitance.

FIGURE 2. SINK CURRENT SWITCHING TIMES FROM DATA AND ENABLE INPUTS

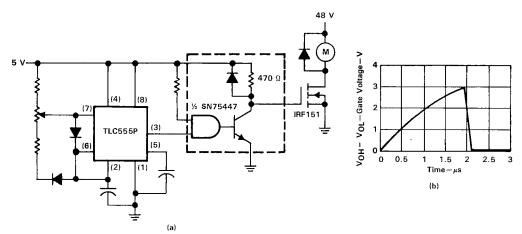

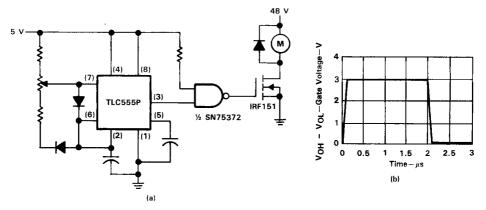

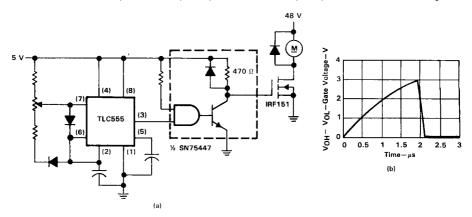

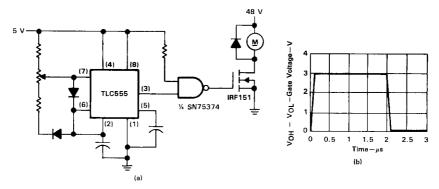

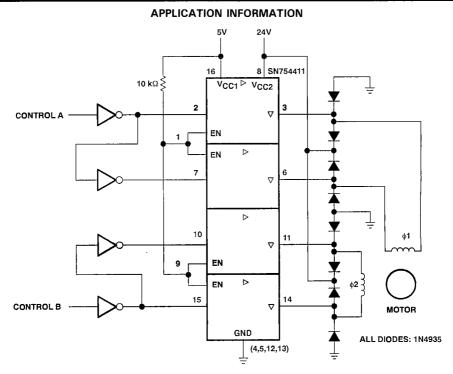

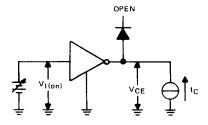

#### **APPLICATION INFORMATION**

This circuit shows one half of an L298 used to provide full-H bridge drive for a 24-V 2-A dc motor. Speed control is achieved with a TLC555 timer. This provides variable duty cycle pulses to the EN input of the L298. In this configuration, the operating frequency is approximately 1.2 kHz. The duty cycle is adjustable from 10% to 90% to provide a wide range of motor speeds. The motor direction is determined by the logic level at the direction control input. The circuit may be enabled or disabled by the logic level at the EN input. A 5-V supply for the logic and timer circuit is provided by a TL431 shunt regulator. For circuit operation, refer to the function table.

| FUNCTION    | TARIE |

|-------------|-------|

| 10100101010 | INDLL |

| ENABLE | DIRECTION<br>CONTROL | 1¥1      | 1¥2      |

|--------|----------------------|----------|----------|

| н      | н                    | source   | sink     |

| н      | L                    | sink     | source   |

| L      | x                    | disabied | disabled |

X = don't care H = high level L = low level

<sup>†</sup>Diodes are 1N4934 or equivalent.

FIGURE 3. L298 AS BIDIRECTIONAL DC MOTOR DRIVER

### SN55451B THRU SN55454B SN75451B THRU SN75454B DUAL PERIPHERAL DRIVERS

D2217, DECEMBER 1976-REVISED MAY 1990

#### PERIPHERAL DRIVERS FOR HIGH-CURRENT SWITCHING AT VERY HIGH SPEEDS

- Characterized for Use to 300 mA

- High-Voltage Outputs

- No Output Latch-Up at 20 V (After Conducting 300 mA)

- High-Speed Switching

- Circuit Flexibility for Varied Applications

- TTL-Compatible Diode-Clamped Inputs

- Standard Supply Voltages

- Plastic DIP (P) with Copper Lead Frame Provides Cooler Operation and Improved Reliability

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

| DEVICE   | LOGIC OF<br>COMPLETE CIRCUIT | PACKAGES |

|----------|------------------------------|----------|

| SN55451B | AND <sup>†</sup>             | FK,JG    |

| SN554    | NAND                         | FK,JG    |

|          | OR                           | FK,JG    |

|          | · ·                          | FK,JG    |

| SN75451B |                              | D,P      |

| SN75452B | NAND                         | D,P      |

| SN75453B | OR                           | D,P      |

| SN75454B | NOR                          | D.P      |

SUMMARY OF SERIES 55451B/75451B

<sup>†</sup>With output transistor base connected externally to output of gate.

#### description

Series SN55451B/75451B dual peripheral drivers are a family of versatile devices designed for use in systems that employ TTL logic. This family is functionally interchangeable with and replaces the SN75450 family and the SN75450A family devices manufactured previously. The speed of the SN55451B/SN75451B family is equal to that of the SN75450 family, and the parts are designed to ensure freedom from latch-up. Diode-clamped inputs simplify circuit design. Typical applications include high-speed logic buffers, power drivers, relay drivers, lamp drivers, MOS drivers, line drivers, and memory drivers.

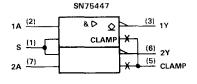

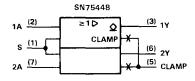

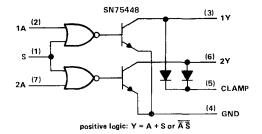

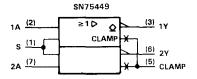

The SN55451B/SN75451B, SN55452B/SN75452B, SN55453B/SN75453B, and SN55454B/SN75454B are dual peripheral AND, NAND, OR, and NOR drivers, respectively, (assuming positive logic), with the output of the logic gates internally connected to the bases of the n-p-n output transistors.

Series SN55451B drivers are characterized for operation over the full military range of -55 °C to 125 °C. Series SN75451B drivers are characterized for operation from 0 °C to 70 °C.

PRODUCTION DATA documents contain information current as of publication data. Products conform to specifications per the terms of Texas Instruments standard warrenty. Production processing does not necessarily include testing of all parameters.

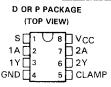

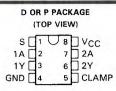

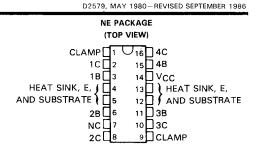

SN55451B, SN55452B, SN55453B, SN55454B...JG PACKAGE SN75451B, SN75452B, SN75453B, SN75454B...D OR P PACKAGE (TOP VIEW)

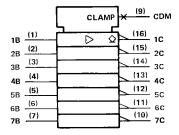

#### SN55451B, SN55452B, SN55453B, SN55454B, . . . FK PACKAGE (TOP VIEW)

|    | (   | Z<br>J<br>3 |    |    | SU VCC | U  |      |    |

|----|-----|-------------|----|----|--------|----|------|----|

| NC | 14  |             |    |    |        |    | 18   | NC |

| 1B | 5   |             |    |    |        |    | 17 [ | 2B |

| NC | 6 [ |             |    |    |        |    | 16   | NC |

| 1Y | 17  |             |    |    |        |    | 15   | 2A |

| NC | 8   |             |    |    |        |    | 14   | NC |

|    |     | 9           | 10 | 11 | 12     | 13 |      |    |

NC-No internal connection

### SN55451B THRU SN55454B, SN75451B THRU SN75454B DUAL PERIPHERAL DRIVERS

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                                                    | ,              | SN55451B   | SN75451B      |       |

|--------------------------------------------------------------------|----------------|------------|---------------|-------|

|                                                                    |                | SN55452B   | SN75452B      | UNIT  |

|                                                                    |                | SN55453B   | SN75453B      | UNIT  |

|                                                                    |                | SN55454B   | SN75454B      |       |

| Supply voltage, V <sub>CC</sub> (see Note 1)                       |                | 7          | 7             | V     |

| Input voltage                                                      |                | 5.5        | 5.5           | V     |

| Interemitter voltage (see Note 2)                                  |                | 5.5        | 5.5           | V     |

| Off-state output voltage                                           |                | 30         | 30            | V     |

| Continuous collector or output current (see Note 4)                |                | 400        | 400           | mA    |

| Peak collector or output current                                   |                | 500        | 500           | mA    |

| $(t_W \le 10 \text{ ms, duty cycle} \le 50\%, \text{ see Note 4})$ |                | 300        | 300           | 104   |

| Continuous total power dissipation                                 |                | See        | bation Rating | Fable |

| Operating free-air temperature range, TA                           |                | -55 to     | 0 to 70       | °C    |

| Storage temperature range                                          |                | -65 to 150 | -65 to 150    | °C    |

| Case temperature for 60 seconds                                    | FK package     | <u> </u>   |               | °C    |

| Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds       | JG package     |            |               | °C    |

| Lead temperature 1,6 mm (1,16 inch) from case for 10 seconds       | D or P package |            | 260           | °C    |

NOTES: 1. Voltage values are with respect to the network ground terminal unless otherwise specified.

2. This is the voltage between two emitters of a multiple-emitter transistor.

3. This value applies when the base-emitter resistance (RBE) is equal to or less than 500  $\Omega.$

4. Both halves of these dual circuits may conduct rated current simultaneously; however, power dissipation averaged over a short time interval must fall within the continuous dissipation rating.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE $T_A = 25 ^{\circ}C$ | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|-----------------------------------------------|---------------------------------------|----------------------------------------|

| D       | 725 mW                                | 5.8 mW/°C                                     | 464 mW                                |                                        |

| FK      | 1375 mW                               | 11.0 mW/°C                                    | 880 mW                                | 275 mW                                 |

| JG      | 1 <b>0</b> 50 mW                      | 8.4 mW/°C                                     | 672 mW                                | 210 mW                                 |

| P       | 1000 <b>m</b> W                       | 8.0 mW/ °C                                    | 640 mW                                |                                        |

### recommended operating conditions

|                                          | SE    | SERIES 55451B |     |      | SERIES 75451B |      |      |

|------------------------------------------|-------|---------------|-----|------|---------------|------|------|

|                                          | MIN   | NOM           | MAX | MIN  | NOM           | MAX  | UNIT |

| Supply voltage, VCC                      | . 4.5 | 5             | 5.5 | 4.75 | 5             | 0.26 | ~    |

| High-level input voltage, VIH            | 2     |               |     | 2    |               |      | ×    |

| Low-level input voltage, V <sub>1L</sub> |       |               | ΛR  | •    |               | 0.8  | V    |

| Operating free-air temperature, TA       | -55   |               | 120 | 0    |               | 70   | °C   |

## SN55451B, SN75451B DUAL PERIPHERAL POSITIVE-AND DRIVERS

### electrical characteristics over recommended operating free-air temperature range

|      |                                        | TEST CON                                     | DITIONOT                         | SN554   | 51B     | SN7545               |       |      |

|------|----------------------------------------|----------------------------------------------|----------------------------------|---------|---------|----------------------|-------|------|

|      | PARAMETER                              | TEST CON                                     | DITIONS                          | MIN TYP | MAX     | MIN TYP <sup>§</sup> | MAX   | UNIT |

| ViK  | input clamp voltage                    | $V_{CC} = MIN,$                              | $I_{\parallel} = -12 \text{ mA}$ | - 1.3   | 2 – 1.5 | - 1.2                | - 1.5 | V    |

| ЮН   | High-level output current              | $V_{CC} = MIN,$<br>$V_{OH} = 30 V$           | V <sub>IH</sub> = MIN,           |         | 300     |                      | 100   | μA   |

| Ver  | VOI Low-level output voltage           | $V_{CC} = MIN,$<br>$I_{OL} = 100 \text{ mA}$ | $V_{IL} = 0.8 V,$                | 0.2     | 5 0.5   | 0.25                 | 0.4   | v    |

| VOL  | Low-level output voltage               | $V_{CC} = MIN,$<br>$I_{OL} = 300 mA$         | $V_{1L} = 0.8 V,$                | 0 9     | 5 O.8   | 0.5                  | 0.7   |      |

| 4    | Input current at maximum input voltage | $V_{CC} = MAX,$                              | $V_{ } = 5.5 V$                  |         | 1       |                      | 1     | mA   |

| Ίн   | High-level input current               | $V_{CC} = MAX,$                              | $V_{I} = 2.4 V$                  |         | 40      |                      | 40    | μA   |

| ηL   | Low-level input current                | $V_{CC} = MAX,$                              | VI = 0.4 V                       |         | - 1.6   | - 1                  | - 1.6 | mA   |

| ІССН | Supply current, outputs high           | $V_{CC} = MAX,$                              | VI = 5 V                         |         | 7 11    | 7                    | 11    | mA   |

| ICCL | Supply current, outputs low            | $V_{CC} = MAX,$                              | V <sub>1</sub> = 0               | 53      | 2 65    | 52                   | 65    | mA   |

<sup>‡</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>§</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25 °C$

| PARAMETER                                        |                       | TEST CO                                                               | ONDITIONS          | MIN    | түр | MAX | UNIT |

|--------------------------------------------------|-----------------------|-----------------------------------------------------------------------|--------------------|--------|-----|-----|------|

| tPLH Propagation delay time, low-to-high-level o | utput                 |                                                                       |                    |        | 18  | 25  | ns   |

| tpHL Propagation delay time, high-to-low-level o | utput                 | i <mark>o</mark> ≈ 200 mA,                                            | $C_{L} = 15  pF$ , |        | 18  | 25  | ns   |

| tTLH Transition time, low-to-high-level output   | $R_{L} = 50 \Omega$ , | See Figure 1                                                          |                    | 5      | 8   | ns  |      |

| tTHL Transition time, high-to-low-level output   |                       |                                                                       |                    |        | 7   | 12  | ns   |

| Very blick level putput uptons often exitabing   | SN554518              | $V_{\rm S} = 20 \text{ V}, \text{ I}_{\rm O} \approx 300 \text{ mA},$ |                    | Vg-6.5 |     |     | mV   |

| VOH High-level output voltage after switching    | SN75451B              | See Figure 2                                                          |                    | Vg-6.  | 5   | _   | inv  |

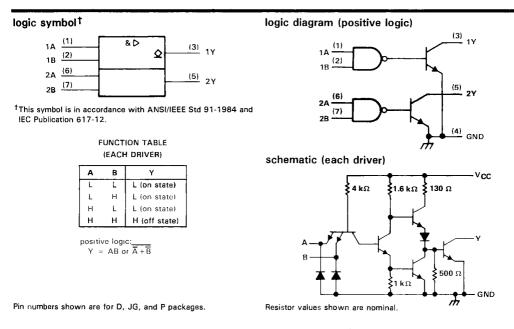

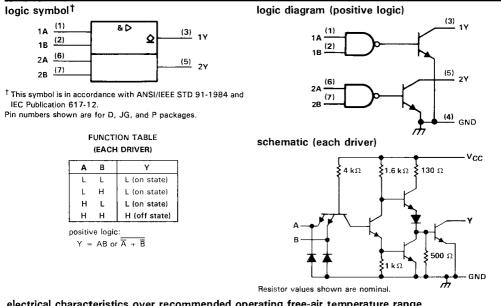

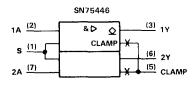

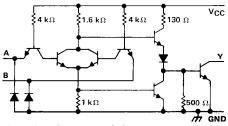

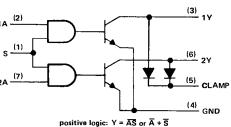

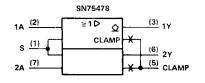

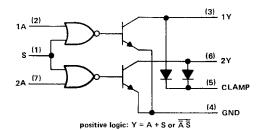

### SN55452B, SN75452B DUAL PERIPHERAL POSITIVE-NAND DRIVERS

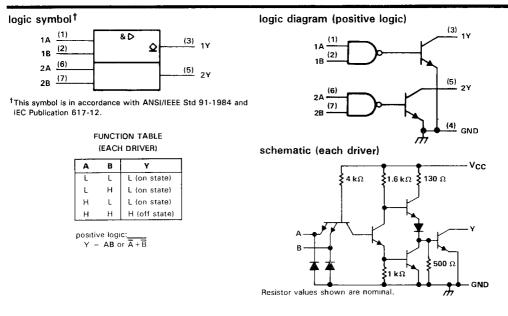

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### FUNCTION TABLE (EACH DRIVER)

| Α | В | Y             |

|---|---|---------------|

| L | L | H (off state) |

| L | н | H (off state) |

| н | L | H (off state) |

| н | н | L (on state)  |

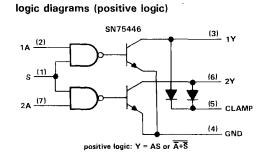

positive logic Y =  $\overrightarrow{AB}$  or  $\overrightarrow{A} + \overrightarrow{B}$

schematic (each driver)

Pin numbers shown are for D, JG, and P packages.

Resistor values shown are nominal.

### electrical characteristics over recommended operating free-air temperature range

|                   | PARAMETER                                 | TEST CON                                     |                        | S   | N55452 | 2B    | s   | N75452 | 2B    | LINUT |

|-------------------|-------------------------------------------|----------------------------------------------|------------------------|-----|--------|-------|-----|--------|-------|-------|

|                   | r AnAlvic (CR                             | IEST CON                                     |                        | MIN | TYPS   | MAX   | MIN | түр§   | MAX   | UNIT  |

| ViK               | input clamp voltage                       | V <sub>CC</sub> =                            | $l_1 = -12 \text{ mA}$ |     | -1.2   | - 1.5 |     | - 1.2  | - 1.5 | v     |

| юн                | High-level output current                 | V <sub>CC</sub> =<br>V <sub>OH</sub> = 30 V  | $V_{IL} = 0.8 V$       |     |        | 300   |     |        | 100   | μA    |

| V <sub>OL</sub> I | Low-level output voltage                  | $V_{CC} = MIN,$<br>$I_{OL} = 100 \text{ mA}$ | V <sub>IH</sub> = MIN  |     | 0.25   | 0.5   |     | 0.25   | 0.4   | v     |

|                   |                                           | $V_{CC} = MIN,$<br>$I_{OL} = 300 \text{ mA}$ | $V_{iH} = MiN,$        |     | 0.5    | 0.8   |     | 0.5    | 0.7   |       |

| ij                | Input current at maximum<br>input voltage | $V_{CC} = MAX,$                              | V <sub>l</sub> = 5.5 V |     |        | 1     |     | _      | 1     | mA    |

| Iн                | High-level input current                  | $V_{CC} = MAX,$                              | VI = 2.4 V             |     |        | 40    |     |        | 40    | μA    |

| կլ                | Low-level input current                   | $V_{CC} = MAX,$                              | $V_{1} = 0.4 V$        |     | - 1.1  | -1.6  |     | - 1.1  | - 1.6 | mA    |

| Іссн              | Supply current, outputs high              | $V_{CC} = MAX,$                              | $V_{1} = 0$            |     | 11     | 14    |     | 11     | 14    | mA    |

| ICCL              | Supply current, outputs low               | $V_{CC} = MAX,$                              | V <sub>1</sub> = 5 V   |     | 56     | 71    |     | 56     | 71    | mA    |

<sup>‡</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>§</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

## switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = $25 \,^{\circ}$ C

| PARAMETER                                        |                                                | TEST CO                    | MIN                      | ТҮР    | MAX | UNIT |    |

|--------------------------------------------------|------------------------------------------------|----------------------------|--------------------------|--------|-----|------|----|

| tPLH Propagation delay time, low-to-high-level o | utput                                          |                            |                          |        | 26  | 35   | ns |

| tPHL Propagation delay time, high-to-low-level o | i <sub>O</sub> ≈ 200 mA,                       | $C_{L} = 15  pF,$          |                          | 24     | 35  | ns   |    |

| tTLH Transition time, low-to-high-level output   | $R_L = 50 \Omega$ ,                            | See Figure 1               |                          | 5      | В   | ns   |    |

| tTHL Transition time, high-to-low-level output   | tTHL Transition time, high-to-low-level output |                            |                          |        | 7   | 12   | กร |

| Vou High lavel output voltage ofter quitables    | SN55452B                                       | $V_{\rm S} = 20 V_{\rm c}$ | l <sub>0</sub> ≈ 300 mA, | Vs-6.5 |     | 5    |    |

| VOH High-level output voltage after switching    | SN75452B                                       | See Figure 2               |                          | Vs-6.  | 5   |      | mV |

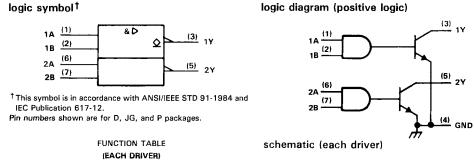

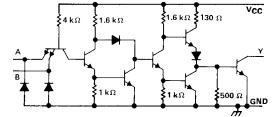

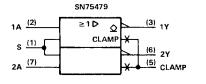

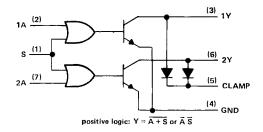

### SN55453B, SN75453B **DUAL PERIPHERAL POSITIVE OR DRIVERS**

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### FUNCTION TABLE (EACH DRIVER)

| Α | В | Y             |

|---|---|---------------|

| L | L | L (on state)  |

| L | н | H (off state) |

| н | L | H (off state) |

| н | н | H (off state) |

positive logic

$Y = A + 8 \text{ or } \overline{\overline{A}\overline{B}}$

### schematic (each driver)

Pin numbers shown are for D, JG, and P packages.

Resistor values shown are nominal.

#### electrical characteristics over recommended operating free-air temperature range

|             | PARAMETER                                 | TEST CON                                     | DITIONOT               | S   | N55453 | в     | SN75453B |      |       |      |

|-------------|-------------------------------------------|----------------------------------------------|------------------------|-----|--------|-------|----------|------|-------|------|

|             | PARAMETER                                 | TEST CON                                     |                        | MIN | TYPS   | MAX   | MIN      | TYP§ | MAX   | UNIT |

| VIK         | Input clamp voltage                       | V <sub>CC</sub> = MIN,                       | $I_{1} = -12  mA$      |     | -1.2   | -1.5  |          | -1.2 | - 1.5 | V    |

| юн          | High-level output current                 | $V_{CC} = MIN,$<br>$V_{OH} = 30 V$           | $V_{IH} = MIN,$        |     |        | 300   |          |      | 100   | μA   |

| VOL Low-lev |                                           | $V_{CC} = MIN,$<br>$I_{OL} = 100 \text{ mA}$ | $V_{IL} = 0.8 V,$      |     | 0.25   | 0.5   |          | 0.25 | 0.4   |      |

|             | Low-level output voltage                  | $V_{CC} = MIN,$<br>IOL = 300 mA              | $V_{ L} = 0.8 V,$      |     | 0.5    | 0.8   |          | 0.5  | 0.7   | v    |

| 1           | Input current at maximum<br>input voltage | V <sub>CC</sub> = MAX,                       | V <sub>i</sub> = 5.5 V |     |        | 1     |          |      | 1     | mA   |

| İн          | High-level input current                  | V <sub>CC</sub> = MAX,                       | $V_{i} = 2.4 V$        |     |        | 40    |          |      | 40    | μA   |

| μL          | Low-level input current                   | V <sub>CC</sub> = MAX,                       | V1 = 0.4 V             |     | - 1    | - 1.6 |          | - 1  | -1.6  | mΑ   |

| Іссн        | Supply current, outputs high              | V <sub>CC</sub> = MAX,                       | V <sub>1</sub> = 5 V   |     | 8      | 11    |          | 8    | 11    | mA   |

| 1CCL        | Supply current, outputs low               | $V_{CC} = MAX,$                              | Vi = 0                 |     | 54     | 68    |          | 54   | 68    | mA   |

\* For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^{\S}$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25 °C$

| PARAMETER                                                  |                           | TEST COND                                 | ITIONS | MIN                | түр | MAX | UNIT     |  |

|------------------------------------------------------------|---------------------------|-------------------------------------------|--------|--------------------|-----|-----|----------|--|

| tPLH Propagation delay time, low-to-high-level or          | utput                     |                                           |        |                    | 18  | 25  | ns       |  |

| tPHL Propagation delay time, high-to-low-level or          | lo ≈ 200 mA, CL           | = 15 pF,                                  |        | 16                 | 25  | ns  |          |  |

| t <sub>TLH</sub> Transition time, low-to-high-level output | R <sub>L</sub> = 50 Ω, Se | e Figure 1                                |        | 5                  | 8   | ns  |          |  |

| tTHL Transition time, high-to-low-level output             | Ng                        |                                           |        |                    | 7   | 12  | ns       |  |

|                                                            | SN55453R                  | $V_{S} = 20 V$ , $I_{O} \approx 300 mA$ , |        | Vs-6.5             |     |     | <u> </u> |  |

| VOH High-level output voltage after switching              | SN7E                      | See Figure 2                              |        | V <sub>S</sub> -6. | 5   |     | mν       |  |

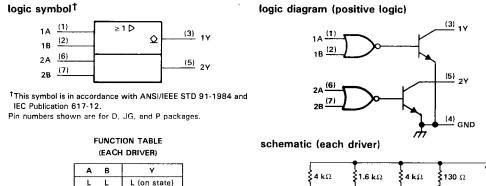

### SN55454B, SN75454B DUAL PERIPHERAL POSITIVE-NOR DRIVERS

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### FUNCTION TABLE (EACH DRIVER)

| A | В  | Y             |

|---|----|---------------|

| L | L  | H (off state) |

| L | н  | L (on state)  |

| н | L. | L (on state)  |

| н | н  | L (on state)  |

positive logic: Y  $\overline{A + B}$  or  $\overline{AB}$

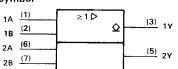

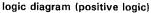

logic diagram (positive logic)

schematic (each driver)

Pin numbers shown are for D, JG, and P packages.

## electrical characteristics over recommended operating free-air temperature range

|      | PARAMETER                                 | TEST CON                             | DITIONE                | SN55454               | SN55454B |     | SN75454B                 |             |      |

|------|-------------------------------------------|--------------------------------------|------------------------|-----------------------|----------|-----|--------------------------|-------------|------|

|      | FARAMETER                                 | TEST COM                             | JIIONS                 | MIN, TYP <sup>§</sup> | MAX      | MIN | MIN TYP <sup>§</sup> MAX |             | UNIT |

| VIK  | Input clamp voltage                       | $V_{CC} = MIN,$                      | II = -12 mA            | - 1.2                 | -1.5     |     | - 1.2                    | -1.5        | v    |

| юн   | High-level output current                 | $V_{CC} = MIN,$<br>$V_{OH} = 30 V$   | $V_{IL} = 0.8 V$       | ·····                 | 300      |     |                          | 100         | μA   |

| Ve   | VOL Low-level output voltage              | $V_{CC} = MIN,$<br>$I_{OL} = 100 mA$ | V <sub>IH</sub> = MIN  | 0.25                  | 0.5      |     | 0.25                     | 0.4         |      |

| VOI. | Low-level butput voltage                  | $V_{CC} = MIN,$<br>$I_{OL} = 300 mA$ | V <sub>IH</sub> = MIN, | 0.5                   | 0.В      |     | 0.5                      | 0. <b>7</b> | v    |

| ų    | Input current at maximum<br>input voltage | V <sub>CC</sub> = MAX,               | V <sub>I</sub> = 5.5 V |                       | 1        |     |                          | 1           | mA   |

| μн   | High-level input current                  | $V_{CC} = MAX,$                      | $V_{1} = 2.4 V$        |                       | 40       |     |                          | 40          | μA   |

| ΙL   | Low-level input current                   | $V_{CC} = MAX,$                      | $V_{1} = 0.4 V$        | -1                    | - 1.6    |     | - 1                      | - 1.6       | mA   |

| 1CCH | Supply current, outputs high              | $V_{CC} = MAX,$                      | V <sub>1</sub> = 0     | 13                    | 17       |     | 13                       | 17          | mA   |

| ICCL | Supply current, outputs low               | $V_{CC} = MAX,$                      | $V_{1} = 5 V$          | 61                    | 79       |     | 61                       | 79          | mA   |

<sup>‡</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>§</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

# switching characteristics, VCC = 5 V, TA = $25 \,^{\circ}$ C

| PARAMETER                                         |                     | TEST CO                      | NDITIONS                 | MIN   | TYP    | MAX | UNIT |

|---------------------------------------------------|---------------------|------------------------------|--------------------------|-------|--------|-----|------|

| tPLH Propagation delay time, low-to-high-level or | utput               |                              |                          |       | 27     | 35  | ns   |

| tPHL Propagation delay time, high-to-low-level or | utput               | i <sub>O</sub> ≈ 200 mA      | . Cլ≃ 15 pF,             |       | 24     | 35  | ns   |

| tTLH Transition time, low-to-high-level output    | $R_L = 50 \Omega$ , | See Figure 1                 |                          | 5     | 8      | ns  |      |

| tTHL Transition time, high-to-low-level output    |                     |                              |                          |       | 7      | 12  | ns   |

| VOH High-level output voltage after switching     | SN55454B            | $V_{\rm S} = 20 \ V_{\rm c}$ | I <sub>O</sub> ≈ 300 mA, |       | Vg-6.5 | 5   |      |

|                                                   | . 54B               | See Figure 2                 |                          | Vg-6. | 5      |     | mV   |

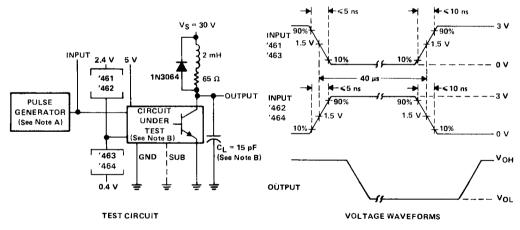

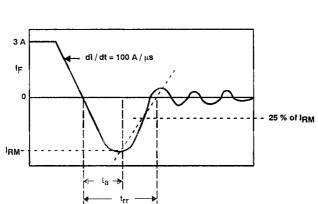

### SN55451B THRU SN55454B SN75451B THRU SN75454B DUAL PERIPHERAL DRIVERS

NOTES: A. The pulse generator has the following characteristics: PRR  $\leq$  1 MHz, Z<sub>0</sub>  $\approx$  50  $\Omega$ . B. C<sub>L</sub> includes probe and jig capacitance.

$C_{I} = 15 \text{ pF}$

(Saa Note B)

### FIGURE 1. SWITCHING TIMES OF COMPLETE DRIVERS

NOTES: A. The pulsa ganarator has tha following characteristics: PRR  $\leq$  12.5 kHz, Z<sub>0</sub> = 50  $\Omega$ . B. C<sub>L</sub> includas probe and jig capacitanca.

GND SUB

,453B

'454B [ 0.4 ∨

TEST CIRCUIT

OUTPUT

VOLTAGE WAVEFORMS

3 V

nν

3 V

0 V

۷он

Voi

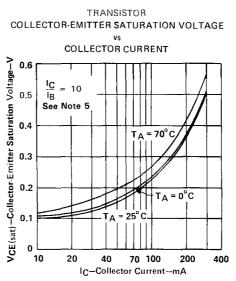

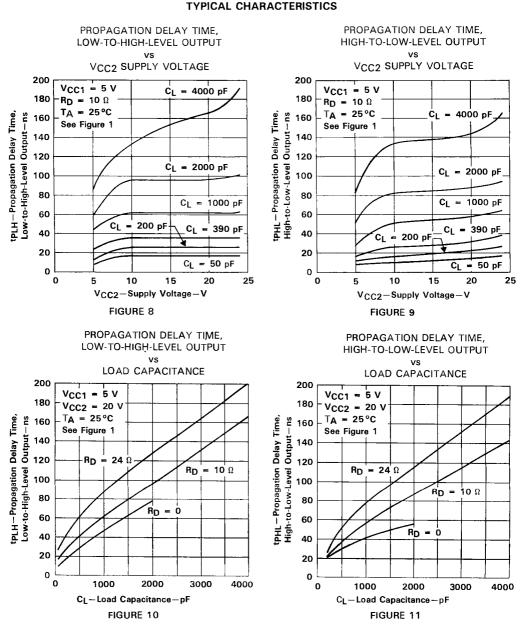

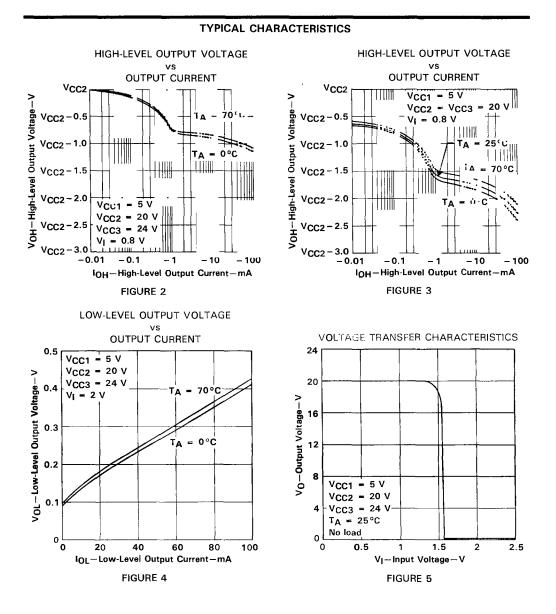

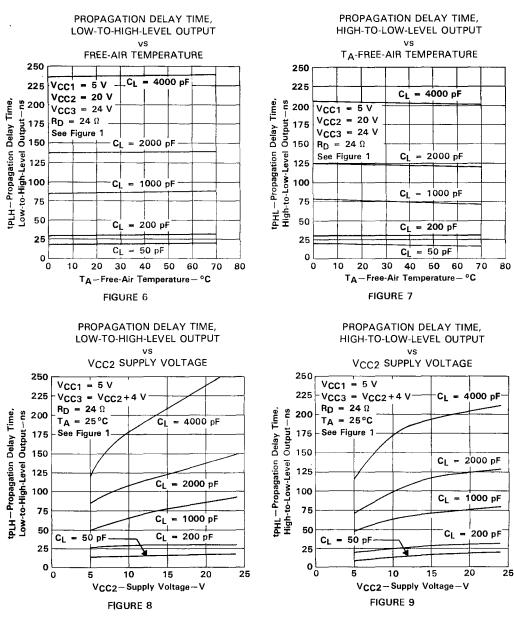

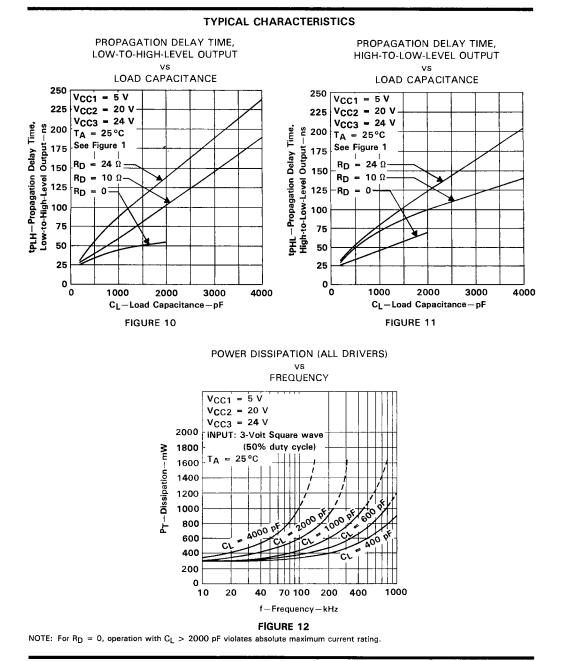

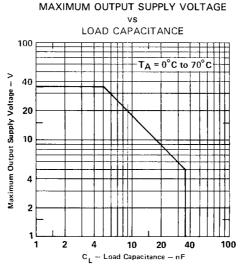

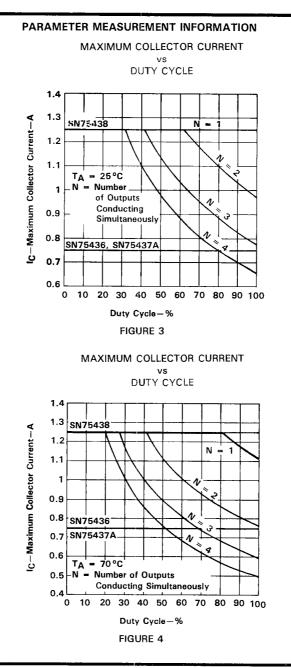

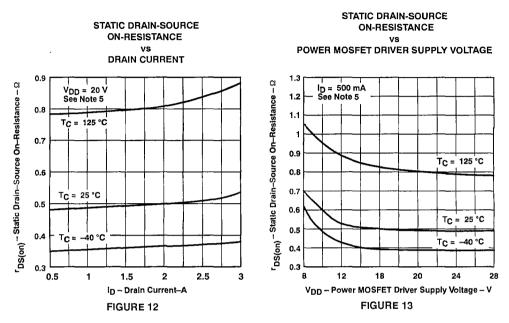

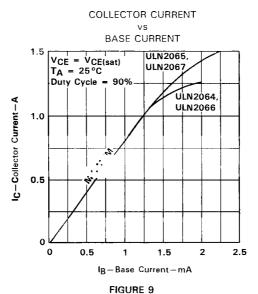

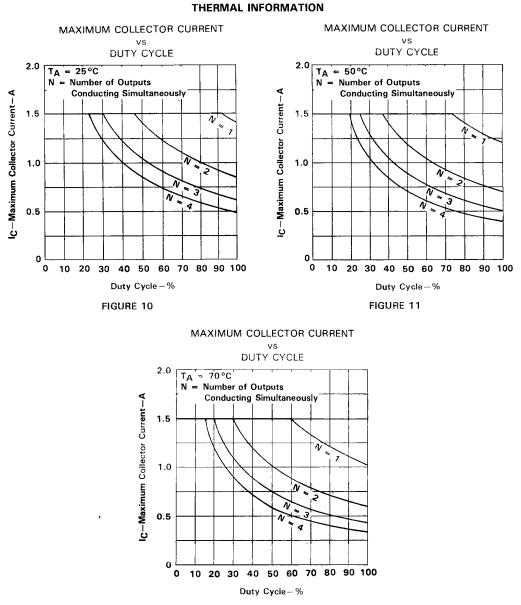

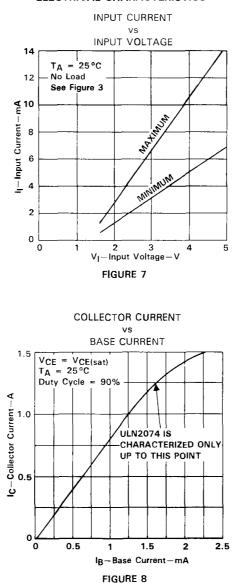

TYPICAL CHARACTERISTICS

### NOTE 5: These parameters must be measured using pulse techniques, t<sub>w</sub> = 300 $\mu$ s, duty cycle $\leq$ 2%.

FIGURE 3

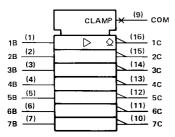

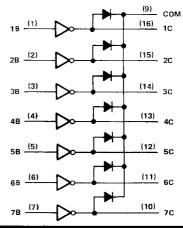

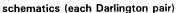

### SN55461 THRU SN55464 SN75461 THRU SN75463 DUAL PERIPHERAL DRIVERS

D2218, DECEMBER 1976-REVISED MAY 1990

#### PERIPHERAL DRIVERS FOR HIGH-VOLTAGE, HIGH-CURRENT DRIVER APPLICATIONS

- Characterized for Use to 300 mA

- High-Voltage Outputs

- No Output Latch-Up at 30 V (After Conducting 300 mA)

- Medium-Speed Switching

- Circuit Flexibility for Varied Applications and Choice of Logic Function

- TTL-Compatible Diode-Clamped Inputs

- Standard Supply Voltages

- Plastic DIP (P) with Copper Lead Frame for Cooler Operation and Improved Reliability

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

#### SUMMARY OF SERIES 55461/75461

| 11.00     | LOGIC | PACKAGES |

|-----------|-------|----------|

| · · ·     | AND   | FK,JG    |

| · · 62    | NAND  | FK,JG    |

| ·. ·63    | OR    | FK,JG    |

| ·. · · 64 | NOR   | FK,JG    |

| SN75461   | AND   | D,P      |

| SN75462   | NAND  | D,P      |

| SN75463   | OR    | D,P      |

#### description

These dual peripheral drivers are functionally interchangeable with SN55451B through SN55454B and SN75451B through SN75453B peripheral drivers, but are designed for use in systems that require higher breakdown voltages than those devices can provide at the expense of slightly slower switching speeds. Typical applications include logic buffers, power drivers, relay drivers, lamp drivers, MOS drivers, line dr**O**ers, and memory drivers.

The SN55461/SN75461, SN55462/SN75462, SN55463/SN75463, and SN55464 are dual peripheral AND, NAND, OR, and NOR drivers, respectively, (assuming positive logic), with the output of the gates internally connected to the bases of the n-p-n output transistors.

Series SN55461 drivers are characterized for operation over the full military temperature range of -55 °C to 125 °C; Series SN75461 drivers are characterized for operation from 0 °C to 70 °C.

| _     | _ |    | -     |

|-------|---|----|-------|

| 1 A 🗌 | 1 | 08 | □ vcc |

| 1 B [ | 2 | 7  | _ 2B  |

| 1 Y 🗍 | 3 | 6  | 🗌 2 A |

| GND [ | 4 | 5  | ] 2Y  |