### ATTENTION

These devices contain circuits to protect the inputs and outputs against damage due to high static voltages or electrostatic fields; however, it is advised that precautions be taken to avoid application of any voltage higher than maximumrated voltages to these high-impedance circuits.

Unused inputs must always be connected to an appropriate logic voltage level, preferably either supply voltage or ground.

Additional information concerning the handling of ESD sensitive devices is provided in Section 12 in a document entitled *''Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies.''*

MBER 1985

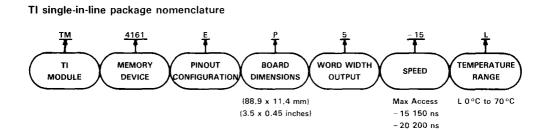

|   |                                                                                                                       | JULY 1984 - REVISED NOVEMBER                                                        |

|---|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

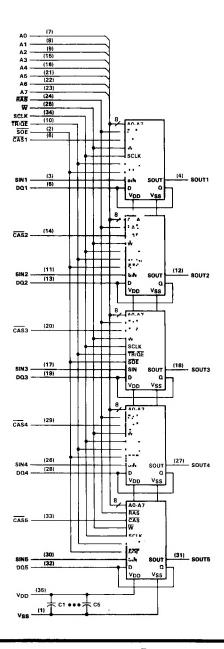

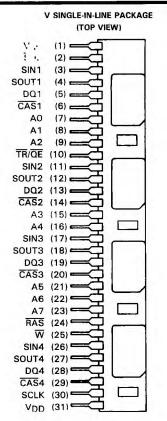

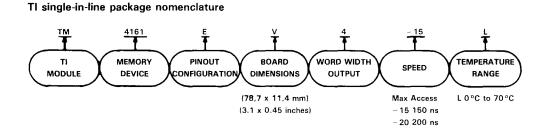

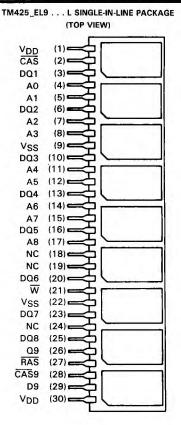

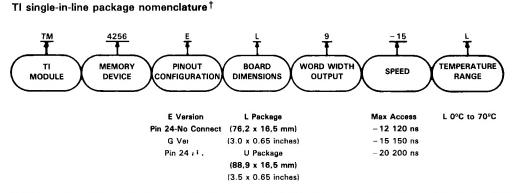

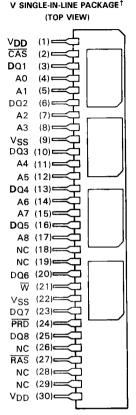

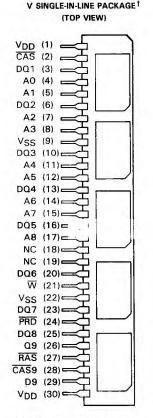

| • | 65,536 X 5 Organization                                                                                               | P SINGLE-IN-LINE PACKAGE                                                            |

| • | Single 5-V Supply (10% Tolerance)                                                                                     | (TOP VIEW)                                                                          |

| • | 35-Pin Single-in-Line Package (SIP)                                                                                   |                                                                                     |

| • | Utilizes Five Multiport Video RAMs in Plastic<br>Chip Carriers                                                        | SOE (2)<br>SIN1 (3)<br>SOUT1 (4)                                                    |

| • | Serial In/Serial Out Capability                                                                                       |                                                                                     |

| • | Dual Accessibility — One Port Sequential<br>Access, One Port Random Access                                            | $\begin{array}{c} \hline CAS1 & (6) \\ A0 & (7) \\ A1 & (8) \end{array}$            |

| • | Five Serial Shift Registers for Sequential<br>Access Applications, Each Comprised of<br>Four Cascaded 64-Bit Segments | A2 (9)<br>TR/OE (10)<br>SIN2 (11)<br>SOUT2 (12)                                     |

| • | Designed for both Video and Non-Video<br>Applications                                                                 | DQ2 (13)<br>CAS2 (14)                                                               |

| • | Fast Serial Port Can Be Configured for<br>Video Data Rates in Excess of 150 MHz                                       | A3 (15)<br>A4 (16)<br>SIN3 (17)                                                     |

| • | TR/QE as Output Enable Allows Direct<br>Connection of DQ and Address Lines to<br>Simplify System Design               | SOUT3 (18)<br>DO3 (19)<br>CAS3 (20)                                                 |

| • | Separate Serial In and Serial Out to Allow<br>Simultaneous Shift In and Out                                           | $\begin{array}{c} A5 \\ A6 \\ (22) \end{array}$                                     |

| • | Supported by TI's TMS34061 Video System<br>Controller (VSC)                                                           | A7 (23)<br>RAS (24)<br>W (25)                                                       |

| • | SOE Simplifies Multiplexing of Serial Data<br>Streams                                                                 | SIN4 (26)                                                                           |

| • | Long Refresh Period 4 ms (256 Cycles)                                                                                 | $\begin{array}{c} DQ4  (28) \\ \hline CAS4  (29) \\ \hline \end{array}$             |

| • | All Inputs, Outputs, Clocks Fully TTL<br>Compatible                                                                   | SIN5 (30)<br>SOUT5 (31)                                                             |

| • | 3-State Outputs                                                                                                       | $\begin{array}{c} DQ5 \\ CAS5 \\ (33) \end{array}$                                  |

|   | Performance Ranges:                                                                                                   | SCLK (34)                                                                           |

|   | ACCESS ACCESS READ                                                                                                    | V <sub>DD</sub> (35)                                                                |

|   | TIME TIME OR                                                                                                          |                                                                                     |

|   | ROW COLUMN WRITE<br>ADDRESS ADDRESS CYCLE                                                                             | PIN NOMENCLATURE                                                                    |

|   | (MAX) (MAX) (MIN)<br>TM4161EP5-15 150 ns 100 ns 240 ns                                                                | A0-A7 Address Inputs                                                                |

|   | TM4161EP5-20 200 ns 135 ns 315 ns                                                                                     | CAS1-CAS5 Column-Address Strobes<br>DQ1-DQ5 Random-Access Data In/Data Out          |

| ٠ | Separate CAS Control with Common Data-                                                                                | RAS Row-Address Strobe                                                              |

|   | In and Data-Out Lines                                                                                                 | SCLK Serial Data Clock                                                              |

| • | Low Power Dissipation:<br>—Operating 1250 mW (Typ)<br>—Standby 400 mW (Typ)                                           | SIN1-SIN5 Serial Data In<br>SOE Serial Output Enable<br>SOUT1-SOUT5 Serial Data Out |

| • | Operating Free-Air Temperature 0°C to                                                                                 | TR/QE         Register Transfer/Q Output Enable           VDD         5-V Supply    |

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warenty. Production processing does not necessarily include testing of all parameters.

70°C

Copyright © 1985, Texas Instruments Incorporated

Write Enable

Ground

Vss

W

#### description

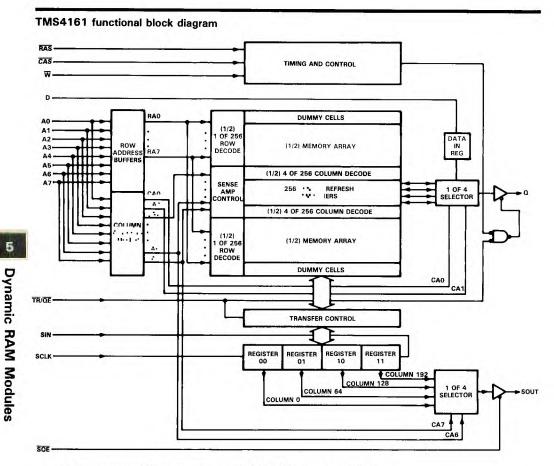

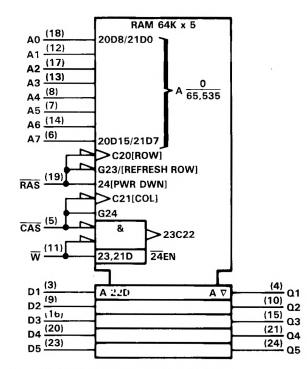

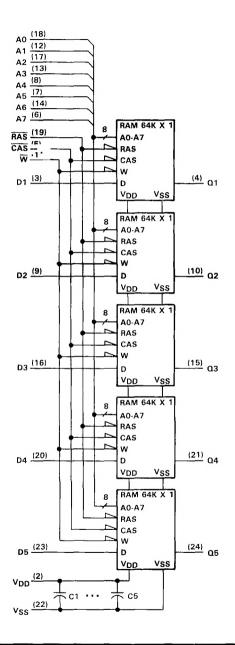

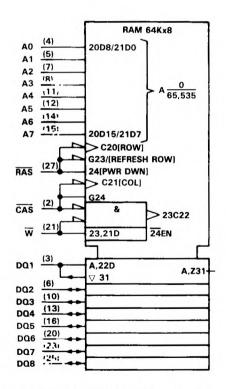

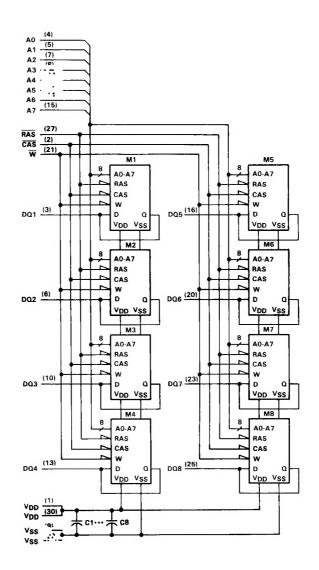

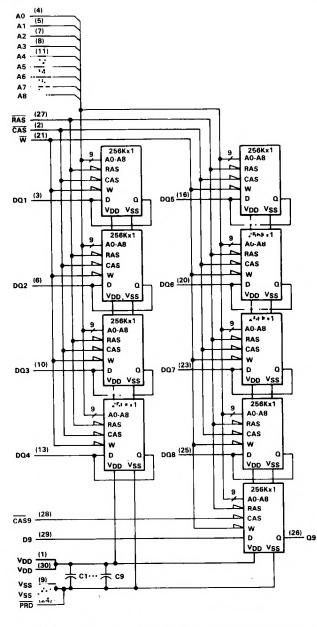

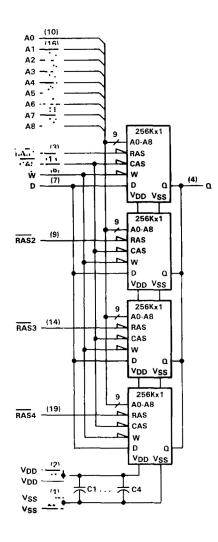

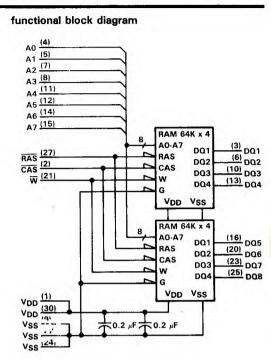

The TM4161EP5 is a 320K dual-access dynamic random-access memory module organized as  $65,536 \times 5$ -bits in a 35-pin single-in-line package comprising five TMS4161FML,  $65,536 \times 1$ -bit Multiport Video RAMs in 22-lead plastic chip carriers mounted on top of a substrate together with five decoupling capacitors. The random-access port makes the module look like it is organized as 65,536 words of five bits each. The sequential-access port is interfaced to five internal 256-bit dynamic shift registers each organized as four cascaded 64-bit shift register segments which are accessed serially. One, two, three, or four 64-bit shift register segments can be sequentially read out after a transfer cycle depending on a two-bit code applied to the two most significant column address inputs.

The TM4161EP5 features full asynchronous dual access capability except when transferring data between the shift registers and the memory array.

Refresh period is extended to 4 milliseconds, and during this period each of the 256 rows must be strobed with RAS in order to retain data. CAS can remain high during the refresh sequence to conserve power. Note that the transfer of a row of data from the memory array to the shift registers also refreshes that row.

All inputs and outputs, including clocks, are compatible with Series 74 TTL. All address lines and data in are latched on chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The TM4161EP5 is guaranteed for operation from 0°C to 70°C.

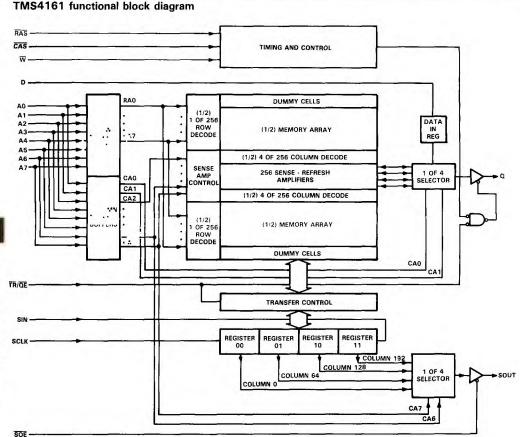

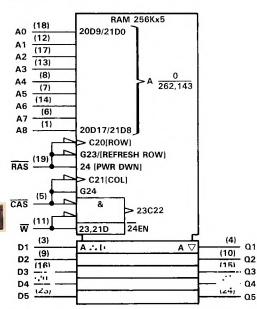

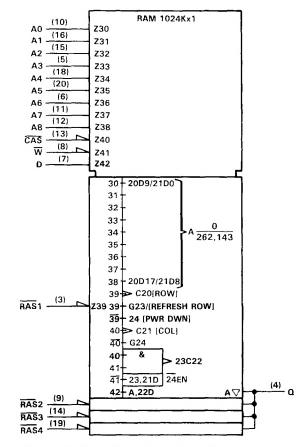

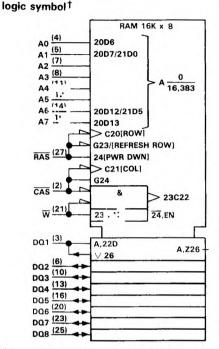

### functional block diagram

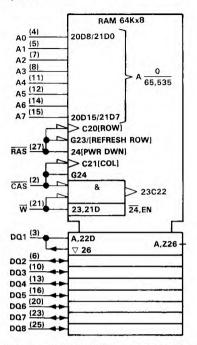

#### random-access address space to sequential address space mapping

The TM4161EP5 is designed with each row divided into four, 64-column sections which map directly onto the four segments of each shift register (see TMS4161 functional block diagram). The first column section to be shifted out is selected by the two most-significant column-address bits. If the two bits represent binary 00, then one to four register segments can be shifted out in order. If the two bits represent binary 01, then only 1 to 3 (the most significant) register segments can be shifted out in order. If the two bits represent 10, then one to two of the most-significant register segments can be shifted out in order. If the two bits represent 10, then one to two of the most-significant register segment can be shifted out in order. All register segments are shifted out with the least-significant bit (bit 0) first and the most-significant bit (bit 63) last. Note that if the two column-address bits equal 00 during the last register transfer cycle (TR/ $\overline{\Omega}$ E at logic level "0" as RAS falls) a total of 256 bits can be sequentially read out of each serial output pin.

5-6

### random-access operation

### TR/QE

The TR/QE pin has two functions. First, it selects either register transfer or random-access operation as RAS falls, and second, during a random-access operation, it functions as an output enable after CAS falls.

To use the TM4161EP5 in the random-access mode,  $\overline{TR}/\overline{\Omega E}$  must be high as  $\overline{RAS}$  falls. Holding  $\overline{TR}/\overline{\Omega E}$  high as RAS falls keeps the 256 elements of the shift registers disconnected from the corresponding 256 bit lines of the memory array. If data is to be shifted, the shift registers must be disconnected from the bit lines. Holding TR/QE low as RAS falls enables the 256 switches that connect the shift registers to the bit lines and indicates that a transfer will occur between the shift registers and one of the memory rows.

During random-access operation, once CAS has been pulled low, TR/QE controls when the data will appear at the Q output (if this is a read cycle). Whenever  $\overline{TR}/\overline{QE}$  is held high during random-access operation, the Q output will be in the high-impedance state. This feature removes the possibility of an overlap between data on the address lines and data appearing on the Q output making it possible to connect the address lines to the Q and D lines (Use of this organization prohibits the use of the early write cycle.).

### address (A0 through A7)

Sixteen address bits are required to decode 1 of 65,536 storage cell locations. Eight row-address bits are set up on pins A0 through A7 and latched onto the chip by the row-address strobe (RAS). Then the eight column-address bits are set up on pins A0 through A7 and latched onto the chip by the column-address strobe (CAS). All addresses must be stable on or before the falling edges of RAS and CAS. RAS is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder. CAS is used as a chip select activating the column decoder and the input and outputs buffers.

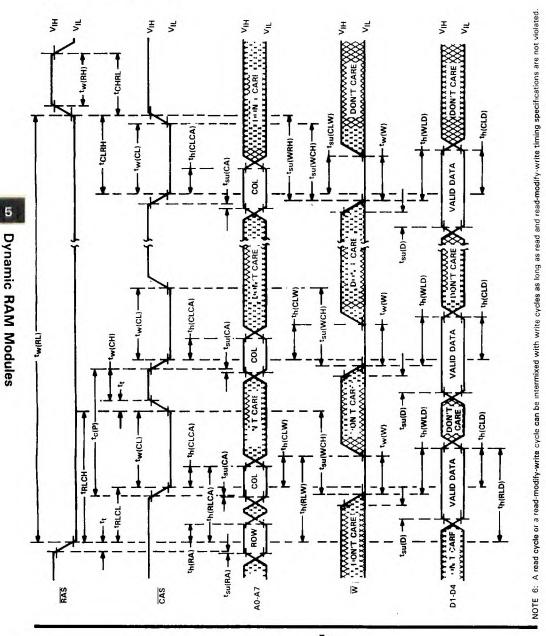

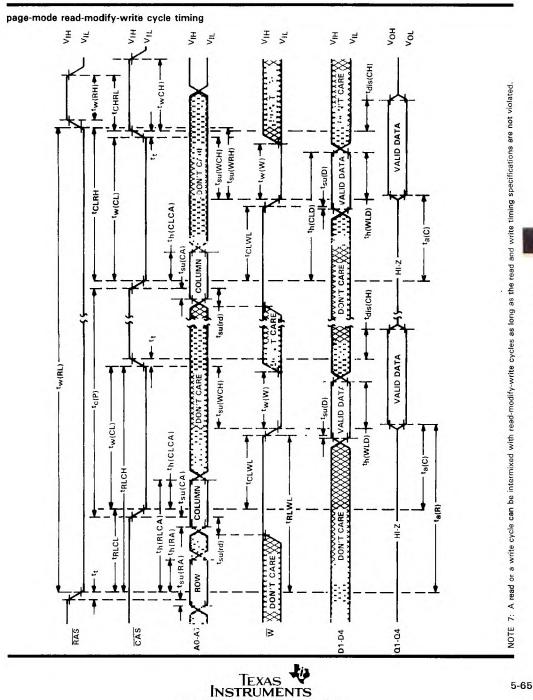

### write enable (W)

The read or write mode is selected through the write-enable ( $\overline{W}$ ) input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write-enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data inputs are disabled when the read mode is selected. The common I/O feature of the TM4161EP5 dictates the use of early write cycles to prevent contention on DQ. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , the data outputs will remain in the high-impedance state for the entire cycle permitting common I/O operation.

### data in (DQ1-DQ5)

Data is written during a write or read-modify-write cycle. The falling edge of CAS or W strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle, W is brought low prior to CAS and the data is strobed in by CAS with setup and hold times referenced to this signal.

### data out (DQ1-DQ5)

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan out of two Series 74 TTL loads. Data C:\* i- the same polarity as data in. The output is in the high-impedance  $\cdot \cdots$  ng) state as long as  $\overline{CAS}$  or  $\overline{TR} \cdot i$  is held high. Data will not appear on the output until after both \*\* and TR/QE have been brought low. In a read cycle, the guaranteed maximum output enable access time is valid only if tCOE is greater than tCOE MAX, and tRLCL is greater than tRLCL MAX. Likewise, ta(C) MAX is valid only if tRLCL is greater than tRLCL MAX. Once the output is valid, it will remain valid while CAS and TR/QE are both low; CAS or TR/QE going high will return the output to a high-impedance state. In an early write cycle, the output is always in a high-impedance state. In a register transfer cycle, the output will always be in a high-impedance state.

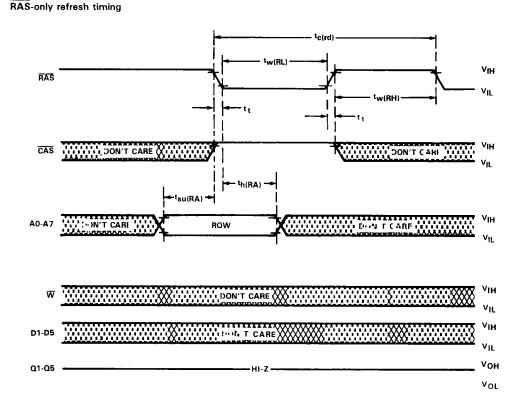

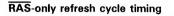

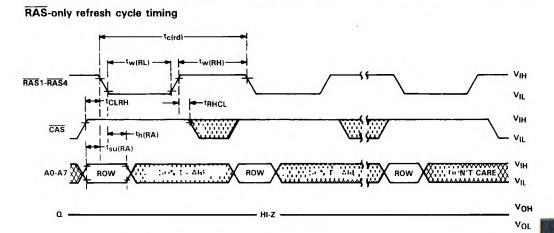

#### refresh

A refresh operation must be performed at least every four milliseconds to retain data. Since the output buffer is in high-impedance state unless CAS is applied, the RAS-only refresh : ... nce avoids any output during refresh. Strobing each of the 256 row addresses (A0 through A7) with the causes all bits in each row to be refreshed. CAS can remain high (inactive) for this refresh sequence to conserve power.

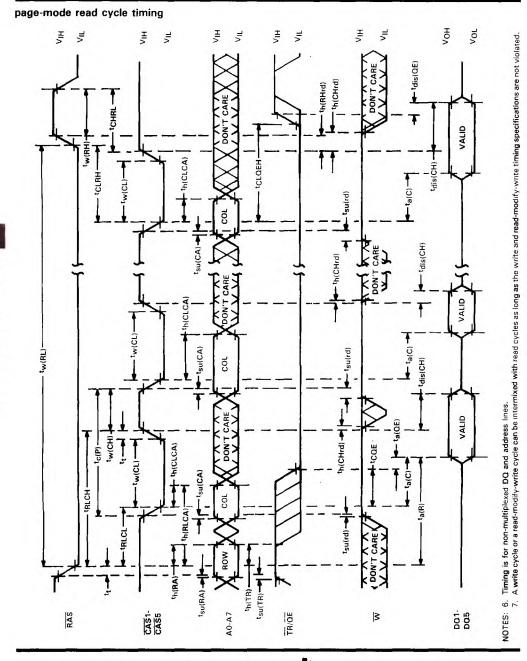

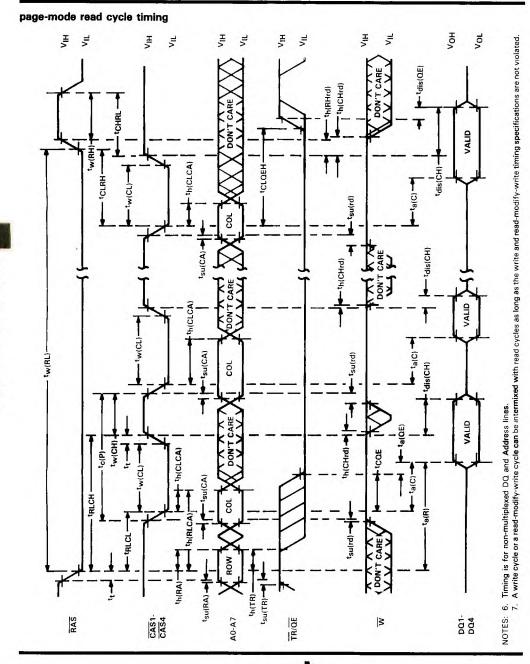

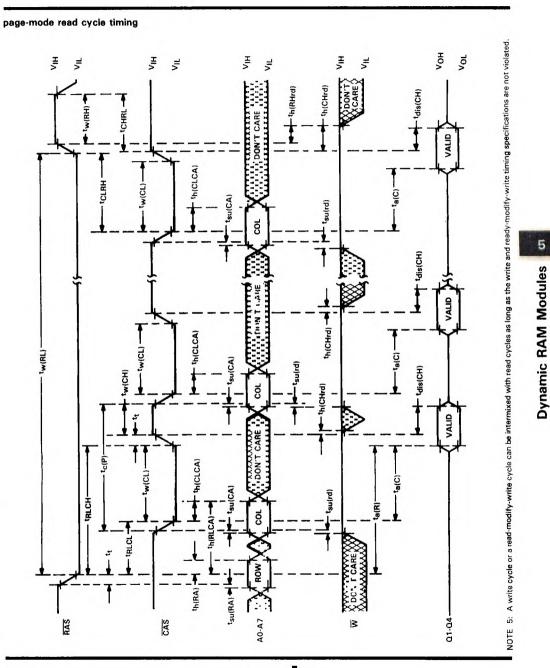

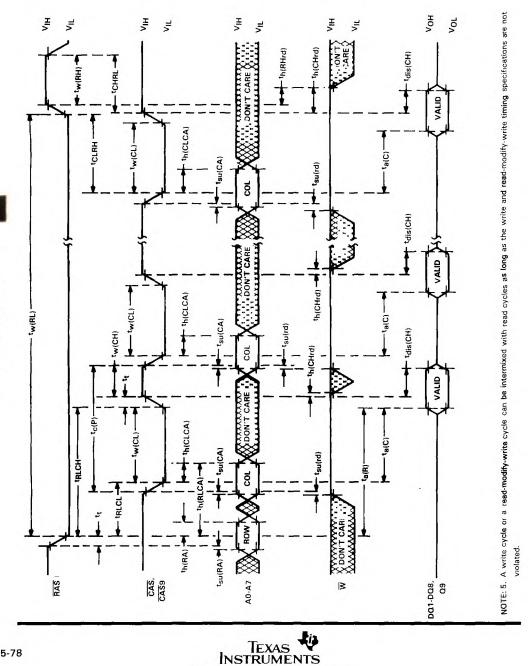

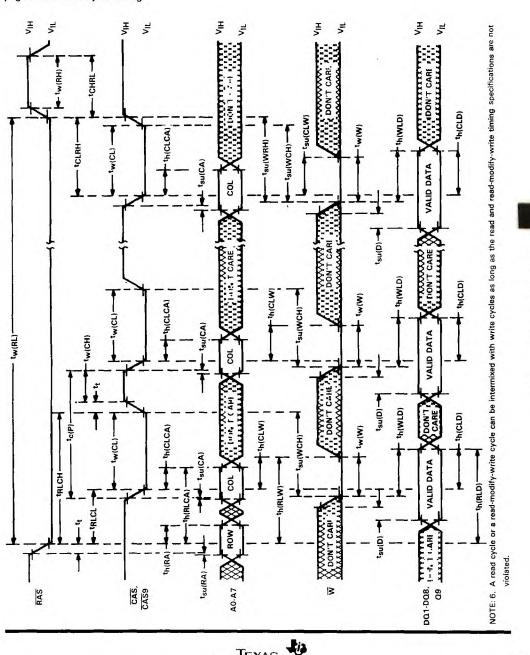

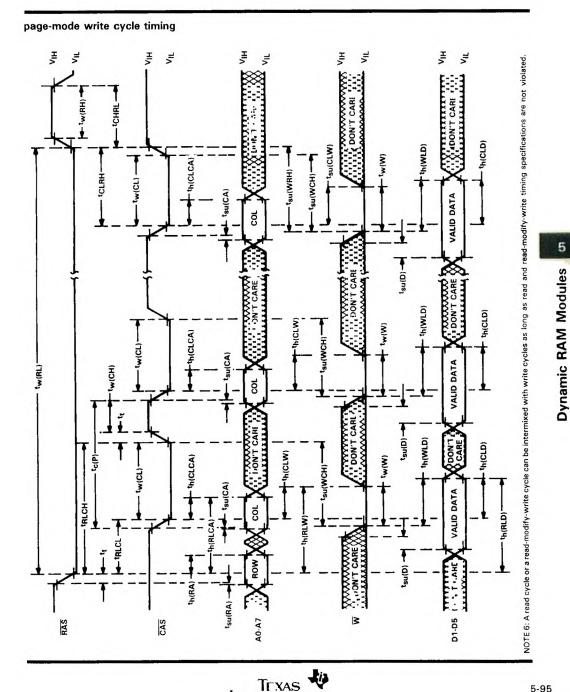

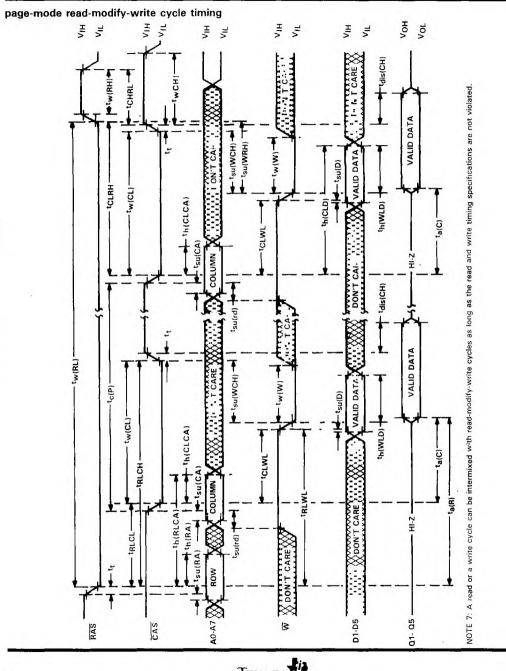

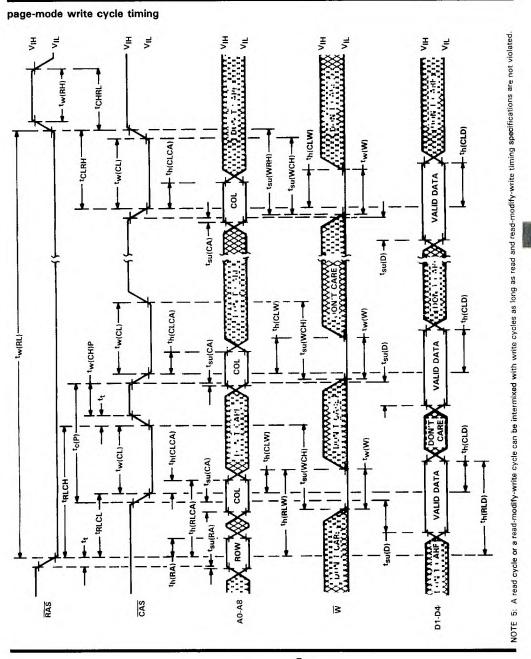

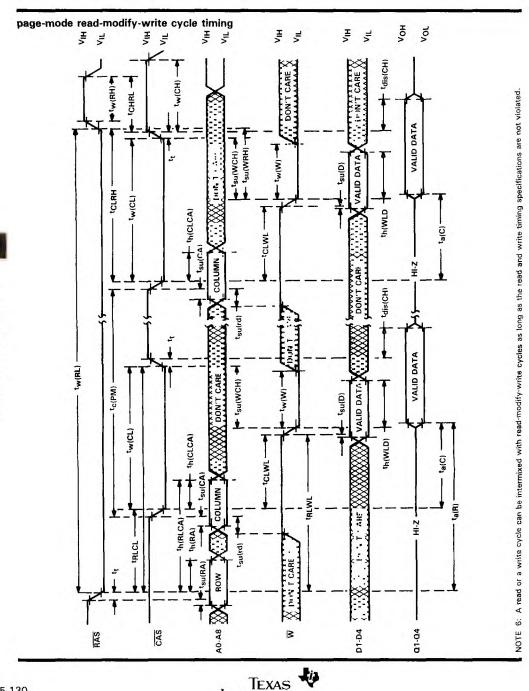

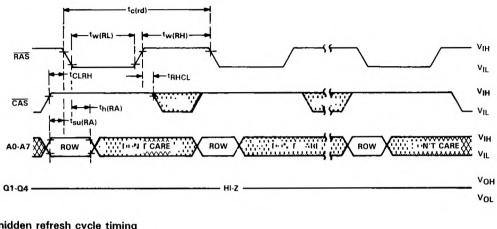

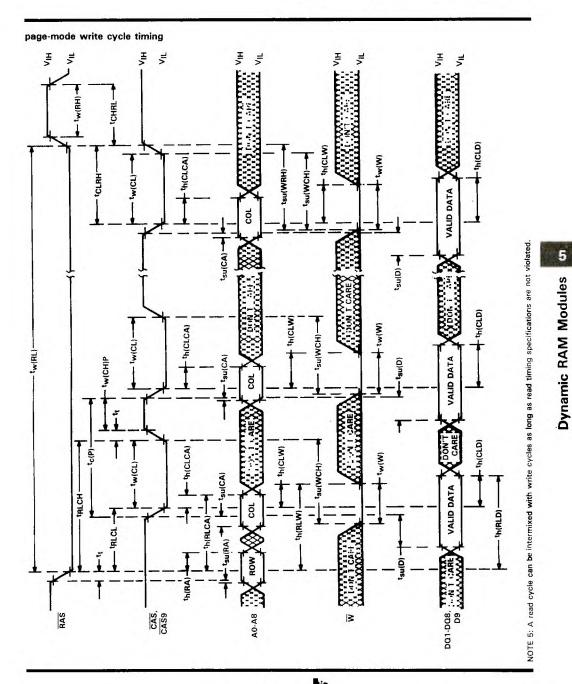

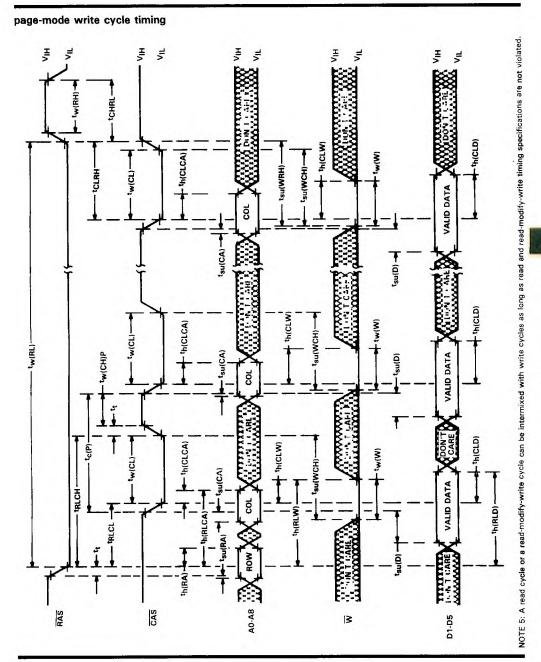

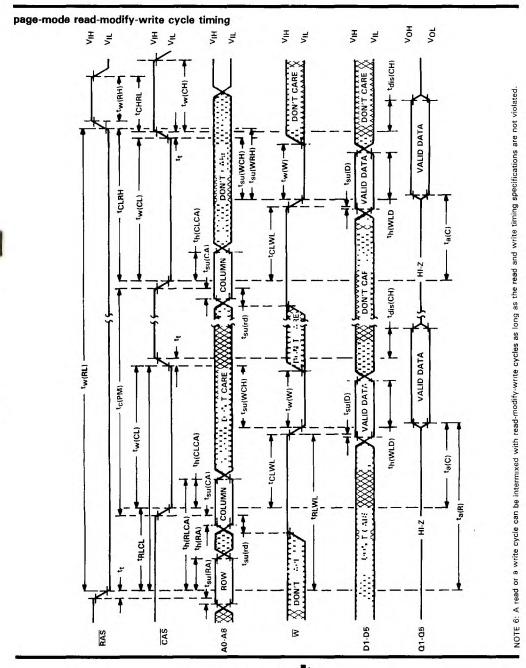

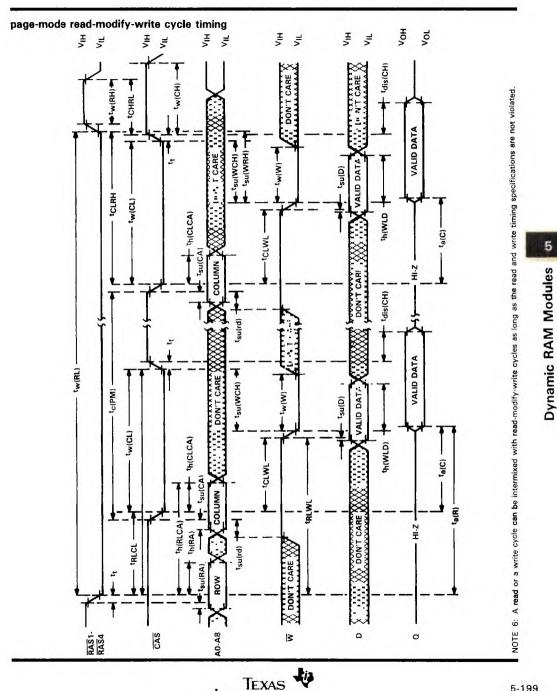

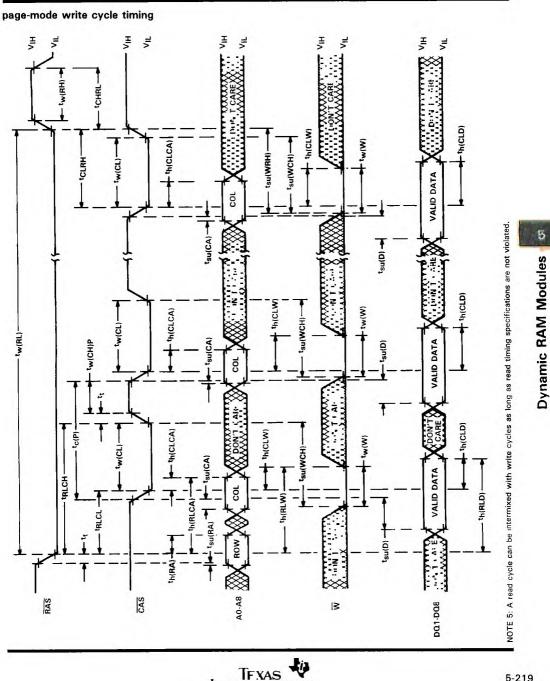

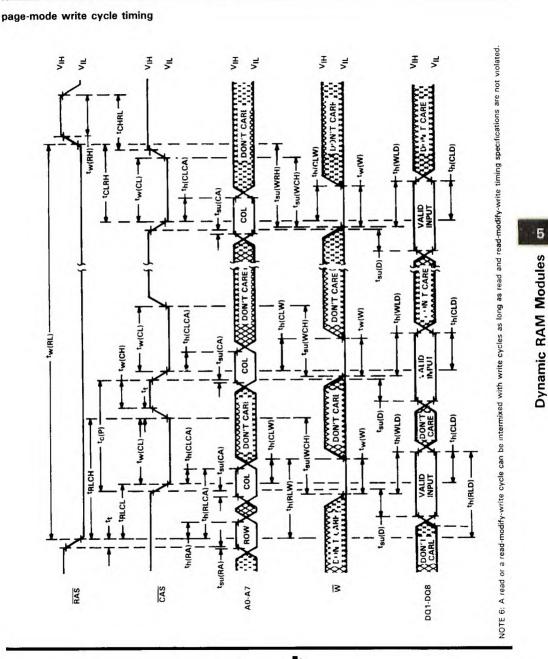

#### page mode

Page-mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the module. Thus, the time required to setup and strobe sequential row addresses for the same page is eliminated. To extend beyond the 256 column locations on M1-M5, the row address and RAS are applied to multiple modules. CAS is then decoded to select the proper module.

#### power up

After power up, the power supply must remain at its steady-state value for 1 ms. In addition,  $\overline{RAS}$  must remain high for 100  $\mu$ s immediately prior to initialization. Initialization consists of performing eight  $\overline{RAS}$  cycles before proper device operation is achieved.

### sequential-access operation

### TR/QE

Memory tran  $\cdots$  operations involving parallel use of the shift registers are first indicated by bringing  $\overline{TR}/\overline{QE}$  low before I:  $\cdot$  falls low. This enables the switches connecting the 256 elements of the shift registers to the 256 bit lines of the memory array. The  $\overline{W}$  line determines whether the data will be transferred from or to the shift registers.

### write enable (W)

In the sequential-access mode,  $\overline{W}$  determines whether a transfer will occur from the shift registers to the memory array, or from the memory array to the shift registers. To transfer from the shift registers to the memory array,  $\overline{W}$  is held low as  $\overline{RAS}$  falls, and, to transfer from the memory array to the shift registers,  $\overline{W}$  is held high as  $\overline{RAS}$  falls. Thus, reads and writes are always with respect to the memory array. The write setup and hold times are referenced to the falling edge of  $\overline{RAS}$  for this mode of operation.

#### row address (A0 through A7)

Eight address bits are required to select one of  $\cdots$  256 possible rows involved in the transfer of data to or from the shift registers. A0-A7,  $\overline{W}$ , and  $\overline{TR} \cdots$  are latched on the falling edge of  $\overline{RAS}$ .

#### register column address (A7, A6)

To select one of the four shift register segments within each shift register (transfer from memory to register only), the appropriate 2-bit column address (A7, A6) must be valid when CAS falls. However, the CAS and segment address signals need not be supplied every transfer cycle, only when it is desired to change or select a new segment.

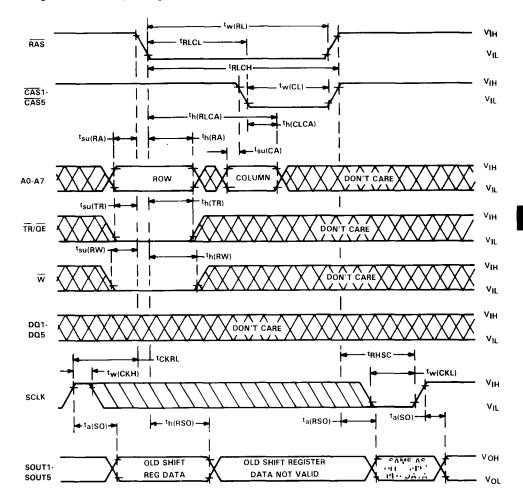

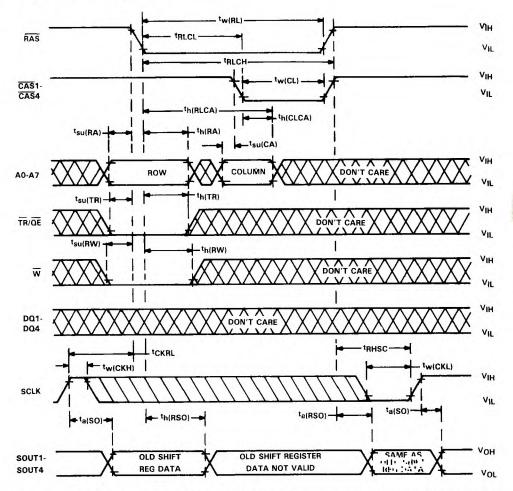

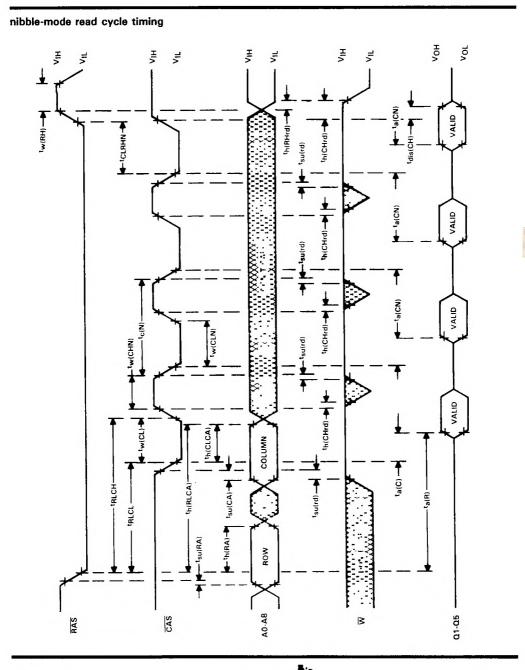

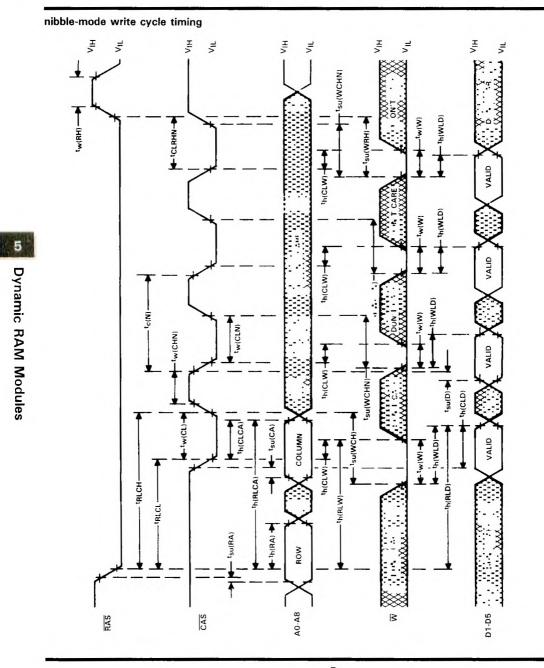

#### SCLK

Data is shifted in and out on the rising edge of SCLK. This makes it possible to view each shift register as though it were made of 256 rising edge D flip-flops connected D to Q. The TM4161EP5 is designed to work with a wide range duty cycle clock to simplify system design. Note that data will appear at the SOUT pins not only on the rising edge of SCLK but also after an access time of  $t_a(RSO)$  from RAS high during a parallel load of the shift registers.

### SIN and SOUT

Data is shifted in through the SIN pins and is shifted out through the SOUT pins. The TM4161EP5 is designed such that it requires 3 ns hold time on SIN as SCLK rises. SOUT is guaranteed not to change for at least

8 ns after SCLK rises. When loading data into the shift registers from the serial inputs in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times. To guarantee proper serial clock sequence after power up, a transfer cycle must be initiated before a serial data stream is applied at SIN.

### SOE

The serial output enable pin controls the impedance of the serial outputs, allowing multiplexing of more than one bank of TM4161EP5 memories into the same external video circuitry. When SOE is at a logic low level, the SOUTs will be enabled and the proper data read out. When SOE is at a logic high level, the SOUTs will be disabled and be in the high-impedance state.

### refresh

The shift registers are also dynamic storage elements. The data held in the registers will be lost unless SCLK goes high to shift the data one bit position, a transfer write operation is invoked, or the data is reloaded from the memory array. See specifications for maximum register data retention times. Important: If the shift registers have remained idle for a time period which exceeds the maximum SCLK high or SCLK low time, the dynamic clock circuits will lose charge. Under these conditions, the shift register clocks must be re-enabled by performing any transfer cycle before data can be shifted into or out of the shift registers.

### single-in-line package and components

PC substrate: 0,79 mm (0.031 inch) minimum thickness Bypass capacitors: Multilayer ceramic Leads: Tin/lead solder coated over phosphor-bronze

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Voltage range on any pin except VDD and data out (see Note 1) |

|---------------------------------------------------------------|

| Voltage range on VDD supply and data out with respect to VSS  |

| Short circuit output current                                  |

| Power dissipation                                             |

| Operating free-air temperature range                          |

| Storage temperature range                                     |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

### recommended operating conditions

| 1   |                                             | MIN  | NOM | MAX    | UNIT |

|-----|---------------------------------------------|------|-----|--------|------|

| VDD | Supply voltage                              | 4.5  | 5   | 5.5    | V    |

| Vss | Supply voltage                              |      | 0   |        | V    |

| VIH | High-level input voltage                    | 2.4  | ١   | DD+0.3 | V    |

| VIL | Low-level input voltage (see Notes 2 and 3) | -0.6 |     | 0.8    | ۷    |

| TA  | Operating free-air temperature              | 0    |     | 70     | °C   |

NOTES: 2. The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

Due to input protection circuitry, the applied voltage may begin to clamp at -0.6 V; test conditions must comprehend this occurrence.

4. See application report entitled "TMS4164A and TMS4416 Input Protection Diode" on page 9-5.

|                   | PARAMETER                                                | TM4161EP5-15 TM4161EP5-20                                                                                                                                              |     |     | TEST CONDITIONS TM4161EP5-15 TM | 5-20 |                  |      |    |

|-------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------|------|------------------|------|----|

|                   | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                        | MIN | TYP | MAX                             | MIN  | TYP <sup>†</sup> | MAX  |    |

| Vон               | High-level output voltage<br>(DQ1-DQ5, SOUT1-SOUT5)      | l <sub>OH</sub> = -5 mA                                                                                                                                                | 2.4 |     |                                 | 2.4  |                  |      | v  |

| VOL               | Low-level output voltage<br>(DQ1-DQ5, SOUT1-SOUT5)       | I <sub>OL</sub> = 4.2 mA                                                                                                                                               |     |     | 0.4                             |      |                  | 0.4  | v  |

| 4                 | Input current (leakage)                                  | $V_1 = 0 V$ to 5.8 V,<br>$V_{DD} = 5 V$ ,<br>All other pins = 0 V                                                                                                      |     |     | ± 10                            |      |                  | ±10  | μA |

| 10                | Output current (leakage)<br>(DQ1-DQ5, SOUT1-SOUT5)       | $V_{O} = 0.4 V \text{ to } 5.5 V,$<br>$V_{DD} = 5 V$                                                                                                                   |     |     | ±10                             |      |                  | ± 10 | μA |

| IDD 1             | Average operating current<br>during read or write cycle  | t <sub>c(rd)</sub> = minimum cycle time,<br>TR/QE low after RAS falls, <sup>‡</sup><br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5            |     | 250 | 350                             |      | 250              | 350  | mA |

| IDD2 <sup>§</sup> | Standby current                                          | After 1 RAS cycle,<br>RAS and CAS high,<br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5                                                        |     | 80  | 100                             |      | 80               | 100  | m# |

| IDD3              | Average refresh current                                  | = minimum cycle time,<br>                                                                                                                                              |     | 210 | 275                             |      | 185              | 250  | mA |

| IDD4              | Average page-mode current                                | t <sub>c(P)</sub> = minimum cycle time,<br>RAS low, CAS cycling,<br>TR/QE low after RAS falls,<br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5 |     | 225 | 275                             |      | 200              | 250  | mA |

| IDD5              | Average shift register<br>current (includes IDD2)        | RAS and CAS high,<br>t <sub>c(SCLK)</sub> = t <sub>c</sub> (SCLK) min,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5                                                        |     | 150 | 200                             |      | 150              | 200  | mA |

| IDD6              | Worst case average<br>DRAM and shift<br>register current | t <sub>c(rd)</sub> = minimum cycle time,<br>· · · · · · = minimum cycle time,<br>· · · · · ow after RAS falls,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5                |     | 425 | 475                             |      | 400              | 450  | mA |

electrical characteristics over full range of recommended operating conditions (unless otherwise noted)

$^{\dagger}All$  typical values are at  $T_A$  = 25°C and nominal supply voltages. \*See appropriate timing diagram.  $^{\$}V_{IL}$  > -0.6 V

### capacitance over recommended supply voltage and operating free-air temperature range, f = 1 MHz

|          | PARAMETER                                  | MAX | UNI |

|----------|--------------------------------------------|-----|-----|

| Ci(A)    | Input capacitance, address inputs          | 35  |     |

|          | Input capacitance, data inputs             | 25  | [   |

| Ci(RC)   | Input capacitance, strobe inputs           | 50  |     |

| Ci(W)    | Input capacitance, write enable input      | 50  | pF  |

| CI(CK)   | Input capacitance, serial clock            | 50  | pr  |

| Ci(SI)   | Input capacitance, serial in               | 25  |     |

| Ci(SOE)  | Input capacitance, serial output enable    | 30  |     |

| Ci(TR)   | Input capacitance, register transfer input | 35  |     |

| Co(SOUT) | Output capacitance, serial out             | 35  |     |

<sup>†</sup>All typical values are at T<sub>A</sub> = 25 °C and nominal supply voltages.

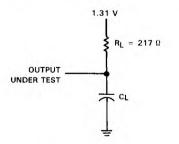

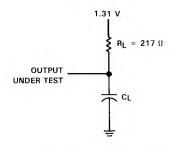

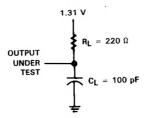

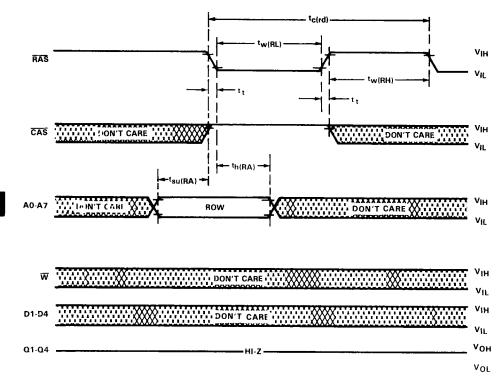

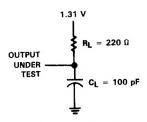

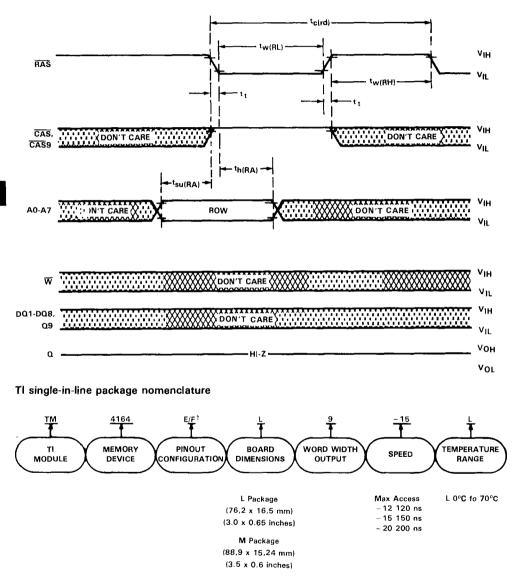

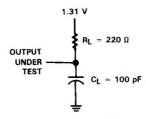

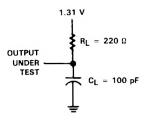

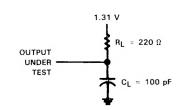

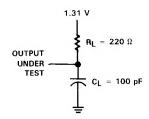

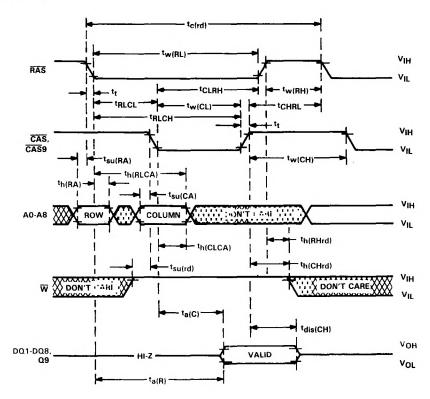

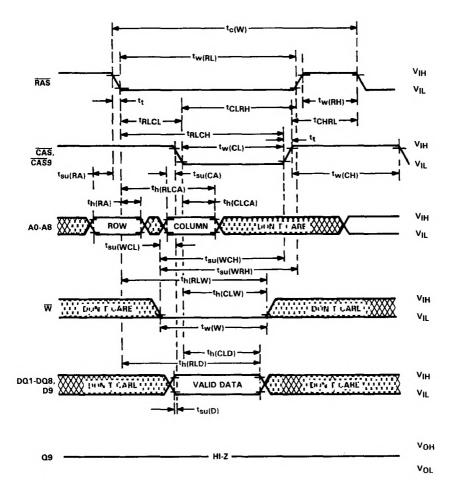

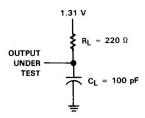

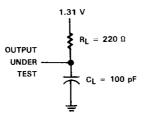

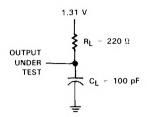

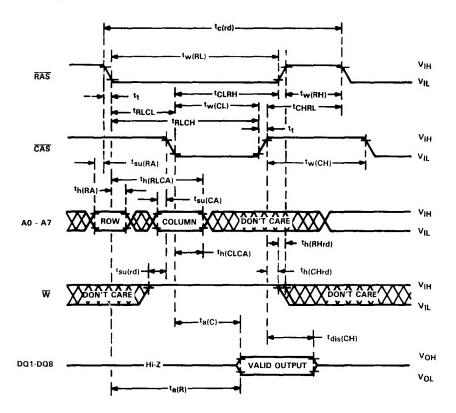

# switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 1)

| 1                                  |                                          | TTOT CONDITIONOT                     | ALT.             | TM4161EP5-15 | TM4161EP5-20 |     |

|------------------------------------|------------------------------------------|--------------------------------------|------------------|--------------|--------------|-----|

| P/                                 | ARAMETER                                 | TEST CONDITIONS <sup>†</sup>         | SYMBOL           | MIN MAX      | MIN MAX      | UNI |

| ta(C)                              | Access time from CAS                     | C <sub>L</sub> = 100 pF              | <sup>t</sup> CAC | 100          | 135          |     |

| <sup>t</sup> a(QE)                 | Access time of Q from<br>TR/QE low       | C <sub>L</sub> = 100 pF              |                  | 40           | 50           |     |

| t <sub>a(R)</sub>                  | Access time from RAS                     | $t_{RLCL} = MAX,$<br>$C_L = 100  pF$ | tRAC             | 150          | 200          |     |

| t <sub>a(RSO)</sub>                | SOUT access time from<br>RAS high        | C <sub>L</sub> = 30 pF               |                  | 65           | 85           |     |

| <sup>t</sup> a(SOE)                | Access time from SOE<br>low to SOUT      | C <sub>L</sub> = 30 pF               |                  | 30           | 30           | ns  |

| ta(SO)                             | Access time from SCLK                    | $C_L = 30 \text{ pF}$                |                  | 45           | 50           |     |

| <sup>t</sup> dis(CH) <sup>‡</sup>  | Ω output disable time<br>from CAS high   | C <sub>L</sub> = 100 pF              | tOFF             | 40           | 40           |     |

| <sup>t</sup> dis(QE) <sup>‡</sup>  | Q output disable time<br>from TR/QE high | $C_L = 100 \text{ pF}$               |                  | 40           | 40           |     |

| <sup>t</sup> dis(SOE) <sup>‡</sup> | Serial output disable time from SOE high | C <sub>L</sub> = 30 pF               |                  | 30           | 30           |     |

<sup>†</sup>Figure 1 shows the load circuit.

\*The maximum values for tdis(CH), tdis(QE), and tdis(SOE) define the time at which the output achieves the open circuit condition and are not referenced to VOH or VOL.

|                       |                                                        | ALT.             | TM416 | 1EP5-15 | TM416 | 1EP5-20 | UNF |

|-----------------------|--------------------------------------------------------|------------------|-------|---------|-------|---------|-----|

|                       |                                                        | SYMBOL           | MIN   | MAX     | MIN   | MAX     | UNI |

| c(P)                  | Page-mode cycle time                                   | tPC              | 160   |         | 225   |         | ns  |

| c(rd)                 | Read cycle time <sup>†</sup>                           | <sup>t</sup> RC  | 240   |         | 315   |         | ns  |

| c(W)                  | Write cycle time                                       | twc              | 240   |         | 315   |         | ns  |

| tc(TW)                | Transfer write cycle time <sup>‡</sup>                 |                  | 240   |         | 315   |         | ns  |

| tc(Trd)               | Transfer read cycle time                               |                  | 240   |         | 315   |         | ns  |

| tc(SCLK)              | Serial-clock cycle time                                | tscc             | 45    | 50,000  | 50    | 50,000  | ns  |

| tw(CH)                | Pulse duration, CAS high (precharge time) <sup>§</sup> | t <sub>CP</sub>  | 50    |         | 80    |         | ns  |

| tw(CL)                | Pulse duration, CAS low                                | tCAS             | 100   | 10,000  | 135   | 10,000  | ns  |

| tw(RH)                | Pulse duration, PAS high (precharge time)              | tRP              | 80    |         | 105   |         | กร  |

| tw(RL)                | Pulse duration, low                                    | tRAS             | 150   | 10,000  | 200   | 10,000  | ns  |

| tw(W)                 | Write pulse duration                                   | twp              | 45    |         | 45    |         | ns  |

| tw(CKL)               | Pulse duration, SCLK low                               |                  | 10    | -,      | 10    |         | ns  |

| tw(CKH)               | Pulse duration, SCLK high                              |                  | 12    |         | 12    |         | ns  |

| tw(QE)                | TR/QE pulse duration low time (read cycle)             |                  | 40    |         | 40    |         | ns  |

| t <sub>t</sub>        | Transition times (rise and fall)<br>RAS, CAS, and SCLK | тт               | 3     | 50      | 3     | 50      | ns  |

| t <sub>su</sub> (CA)  | Column-address setup time                              | tASC             | 0     |         | 0     |         | ns  |

| t <sub>su(RA)</sub>   | Row-address setup time                                 | tASR             | 0     |         | 0     |         | ns  |

| t <sub>su</sub> (RW)  | W setup time before RAS low<br>with TR/QE low          |                  | 0     |         | o     |         | ns  |

| t <sub>su(D)</sub>    | Data setup time                                        | tDS              | 0     |         | 0     |         | ns  |

| tsu(rd)               | Read-command setup time                                | tRCS             | 0     |         | 0     |         | ns  |

| t <sub>su</sub> (WCL) | Early write-command setup time<br>before CAS low       | twcs             | - 5   |         | - 5   |         | ns  |

| t <sub>su</sub> (WCH) | Write-command setup time before CAS high               | tCWL             | 40    |         | 60    |         | ns  |

| t <sub>su</sub> (WRH) | Write-command setup time befora RAS high               | tRWL             | 40    |         | 60    |         | ns  |

| <sup>t</sup> su(TR)   | TR/QE setup time before RAS low                        |                  | 0     |         | 0     |         | ns  |

| t <sub>su</sub> (SI)  | Serial-data setup time before SCLK high                |                  | 6     |         | 6     |         | ns  |

| th(SI)                | Serial-data-in hold tima after SCLK high               |                  | 3     |         | 3     |         | ns  |

| th(CLCA)              | Column-address hold time after CAS low                 | <sup>t</sup> CAH | 45    |         | 55    |         | ns  |

| th(RA)                | Row-address hold time                                  | tRAH             | 20    |         | 25    |         | ns  |

| th(RW)                | W hold time after RAS low with TR/QE low               |                  | 20    |         | 20    |         | ns  |

| th(RLCA)              | Column-address hold time after RAS low                 | tAR              | 95    |         | 120   |         | ns  |

| <sup>t</sup> h(CLD)   | Data hold time after CAS low                           | tDH              | 60    | _       | 80    |         | ns  |

| th(RLD)               | Data hold time after RAS low                           | <sup>1</sup> DHR | 110   |         | 145   |         | ns  |

| th(WLD)               | Data hold time after W low                             |                  | 45    |         | 55    |         | ns  |

| th(CHrd)              | Read-command hold time after CAS high                  |                  | 0     |         | 0     |         | ns  |

(Continued next page.)

NOTE 5: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, VIL max and VIH min must be met at the 10% and 90% points.

<sup>†</sup>All cycle times assume  $t_t = 5$  ns axcept  $t_c(SCLK)$  which assumes  $t_t = 3$  ns. <sup>‡</sup>Multiple transfer write cycles require separation by either a 500-ns RAS-precharge interval or any other active RAS-cycle. §Page-mode onlγ.

|                          |                                                                                                    | ALT.             | TM416 | 1EP5-15 | TM416 | 1EP5-20 |      |

|--------------------------|----------------------------------------------------------------------------------------------------|------------------|-------|---------|-------|---------|------|

|                          | Contractor and the contractor of the                                                               | SYMBOL           | MIN   | MAX     | MIN   | MAX     | UNIT |

| th(RHrd)                 | Read-command hold time after RAS high                                                              | <sup>t</sup> RRH | 5     |         | 5     |         | ns   |

| th(CLW)                  | Write-command hold time after CAS low                                                              | tWCH             | 60    |         | 80    |         | ns   |

| th(RLW)                  | Write-command hold time after RAS low                                                              | tWCR             | 110   |         | 145   |         | ns   |

| th(RSO)                  | Serial-data-out hold time after<br>RAS low with TR/QE low                                          |                  | 30    | 11      | 30    |         | ns   |

| th(SO)                   | Serial-data-out hold time after SCLK high                                                          |                  | 8     |         | 8     |         | ns   |

| th(TR)                   | TR/QE hold time after RAS low (transfer)                                                           |                  | 20    |         | 20    |         | ns   |

| TRLCH                    | Delay time, RAS low to CAS high                                                                    | tCSH             | 150   | 1       | 200   |         | ns   |

| tCHRL                    | Delay time, CAS high to RAS low                                                                    | tCRP             | 0     |         | 0     |         | ns   |

| <b><sup>t</sup>CLQEH</b> | Delay time, CAS low to OF high                                                                     |                  | 100   |         | 135   |         | ns   |

| tCLRH                    | Delay time, CAS low to high                                                                        | trsh             | 100   |         | 135   |         | ns   |

| †CQE                     | Delay time, CAS low to us low<br>(maximum value specified only<br>to guarantee tergs) access time) |                  |       | 60      |       | 85      | ns   |

| TRHSC                    | Delay time, nigh to SCIK high                                                                      |                  | 80    | 50,000  | 80    | 50,000  | ns   |

| <sup>t</sup> RLCL        | Delay time, RAS low to : low (maximum value specified only to guarantee access time)               | <sup>t</sup> RCD | 25    | 50      | 30    | 65      | ns   |

| <sup>t</sup> CKRL        | Delay time, SCLK high before<br>RAS low with TR/QE low¶                                            |                  | 10    | 50,000  | 10    | 50,000  | ns   |

| trf(MA)                  | Refresh time interval, memory array                                                                | tREF1            | -     | 4       |       | 4       | ms   |

| trf(SR)                  | Refresh time interval, shift register#                                                             | tREF2            | 1     | 50,000  |       | 50,000  | ns   |

timing requirements over recommended supply voltage range and operating free-air temperature range (concluded)

NOTE 5: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, VIL max and VIH min must be met at the 10% and 90% points.

SCLK may be high or low during  $t_{W(RL)}$ , but there can not be any positive edge transitions on SCLK for a minimum of 10 ns prior to RAS going low with TR/QE low (i.e., before a transfer cycle).

#See "refresh" on page 5-9.

### PARAMETER MEASUREMENT INFORMATION

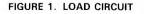

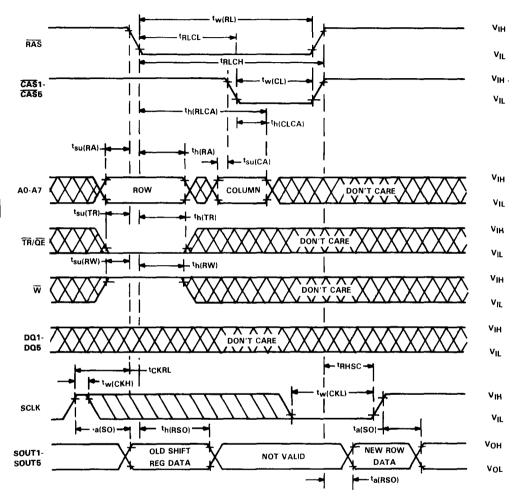

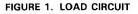

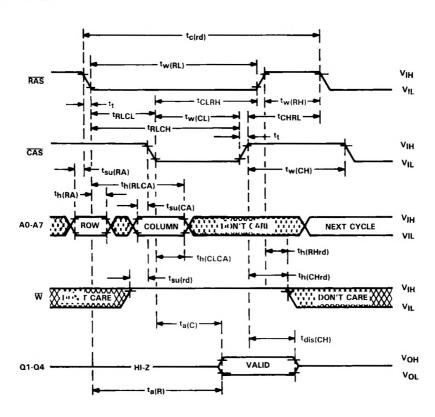

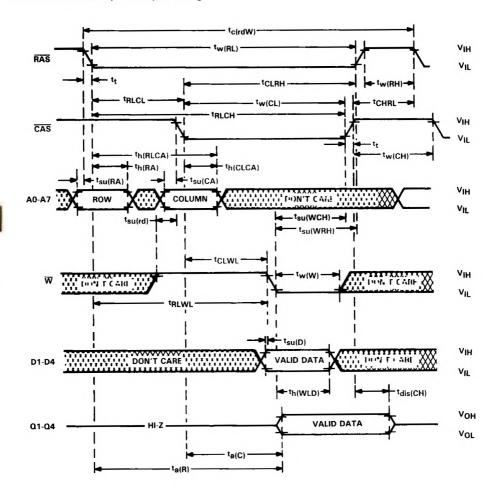

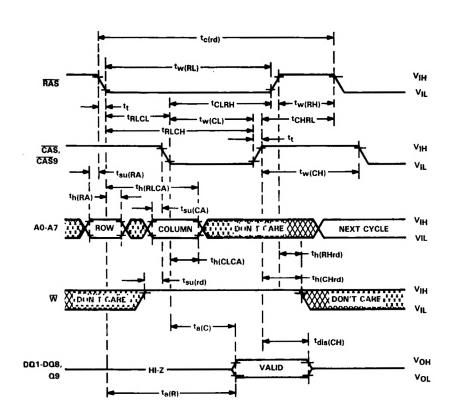

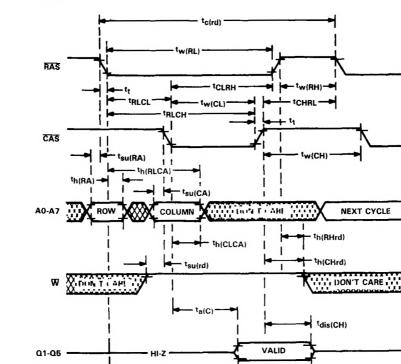

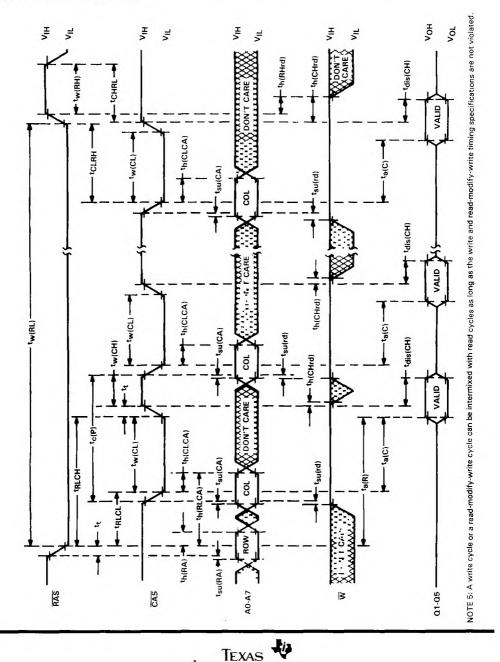

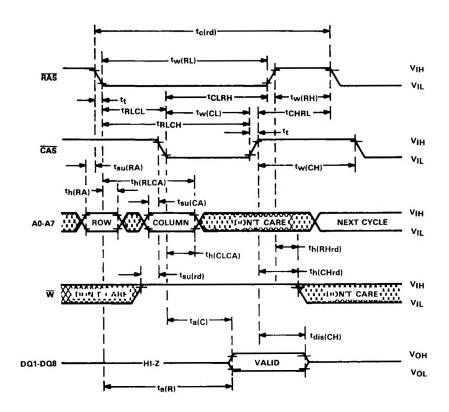

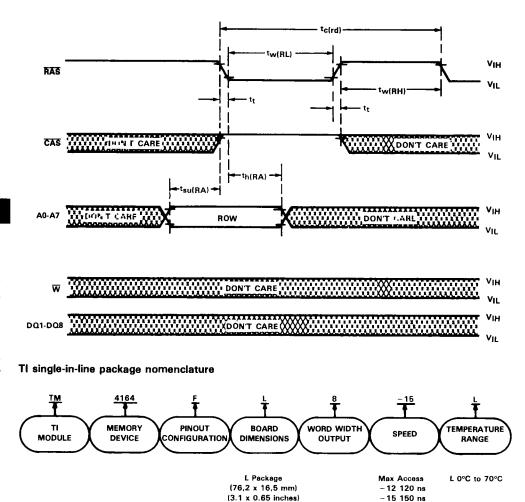

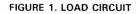

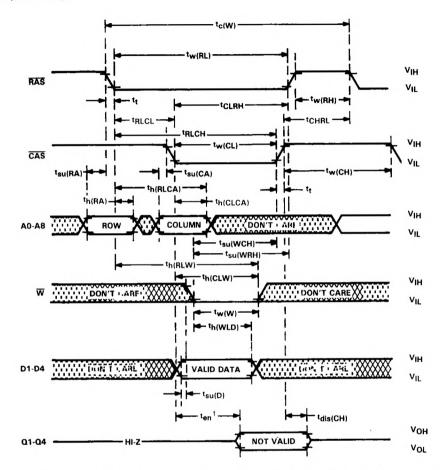

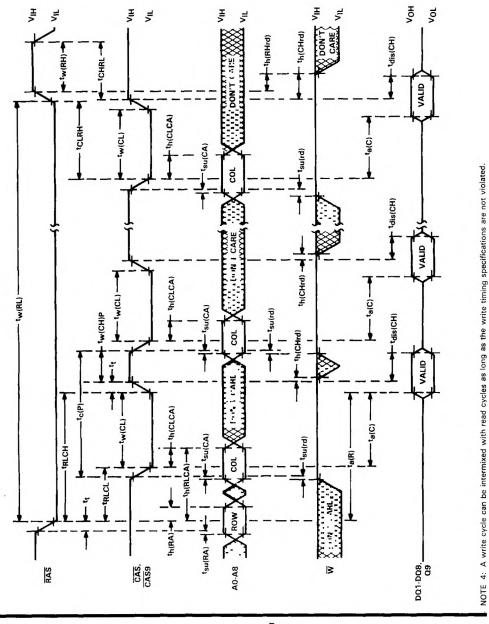

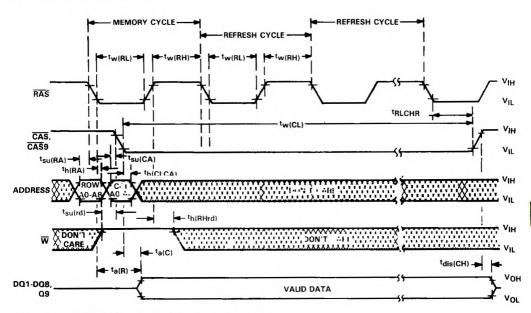

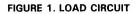

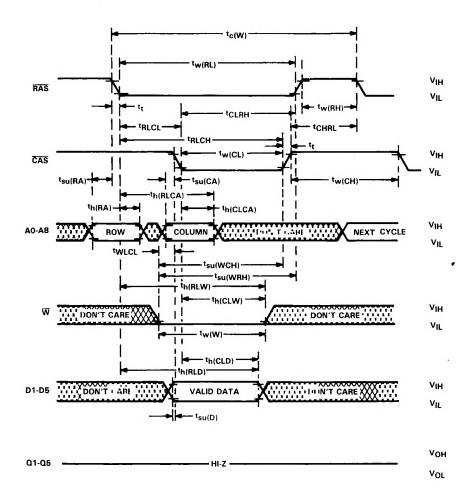

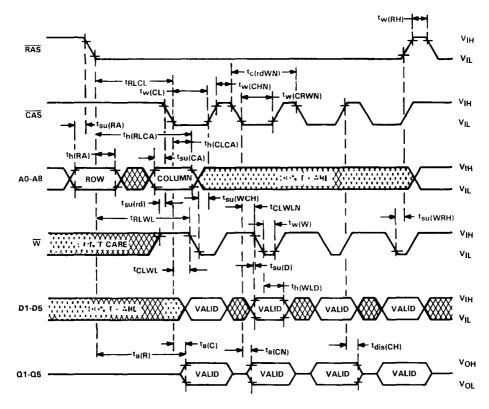

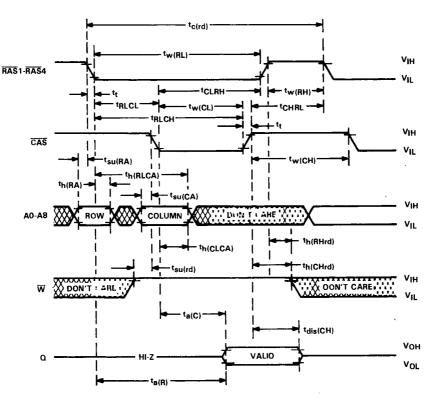

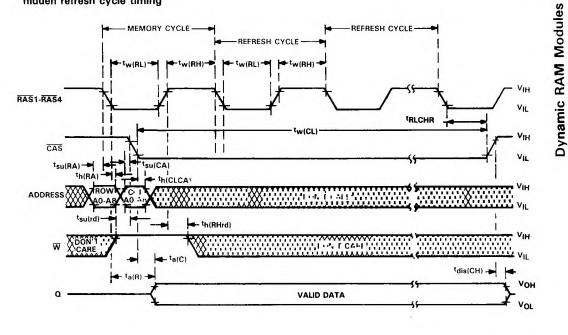

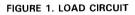

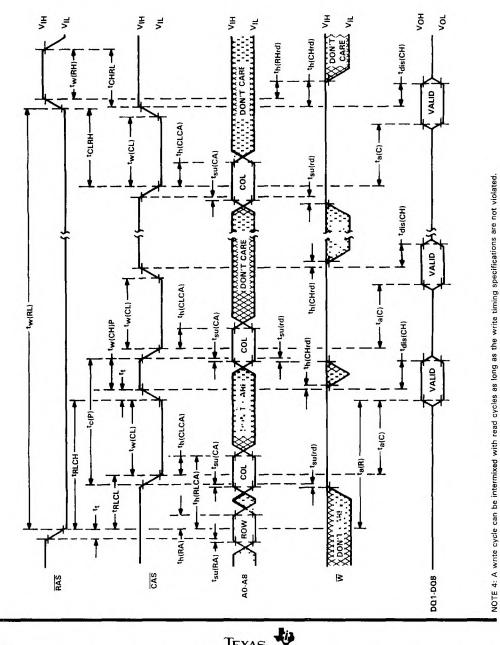

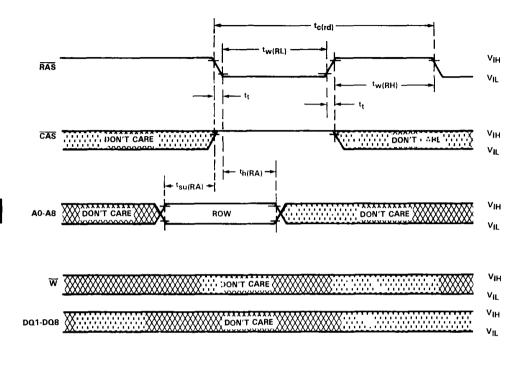

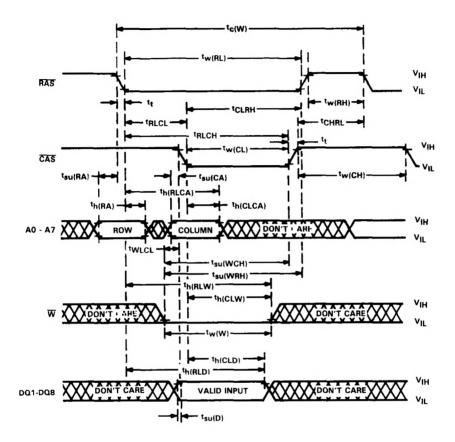

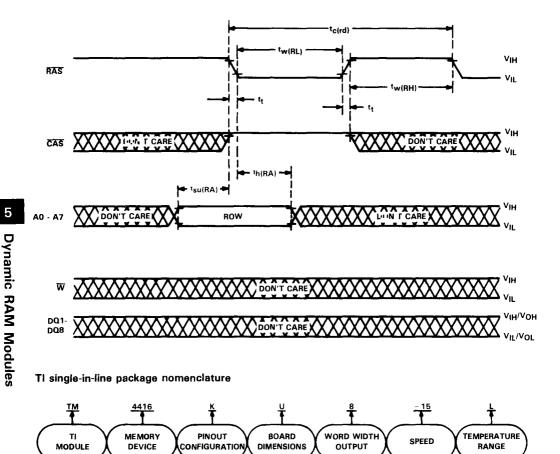

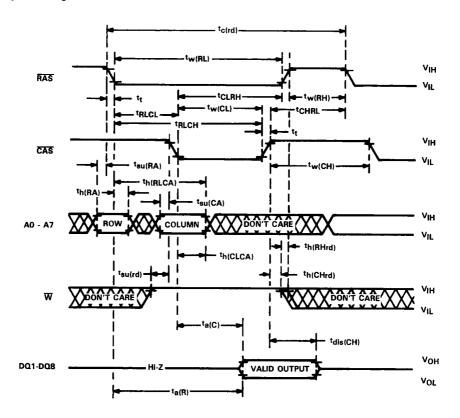

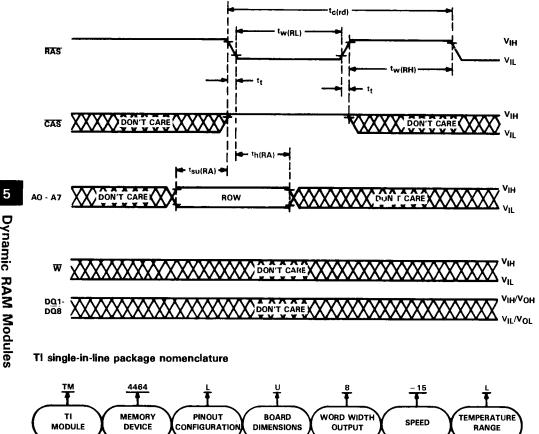

read cycle timing

.

**Dynamic RAM Modules**

.

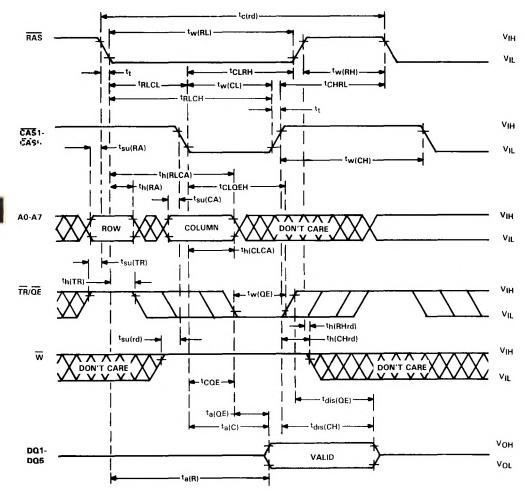

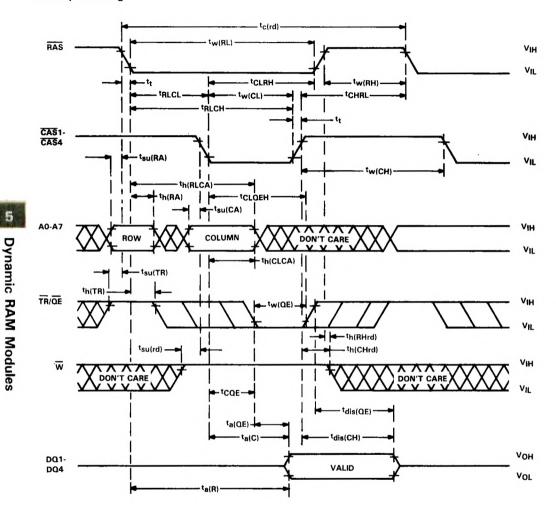

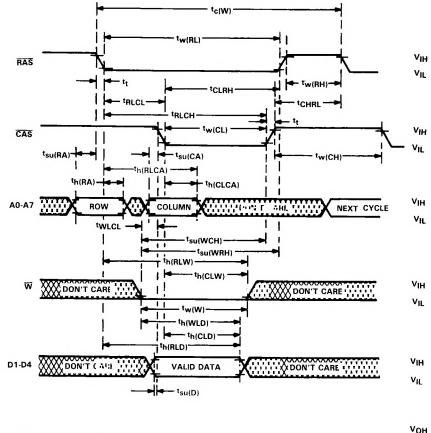

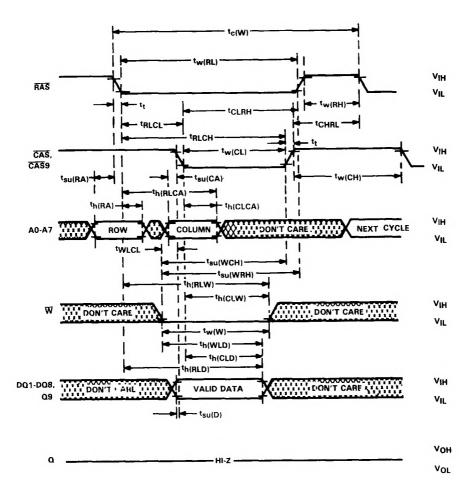

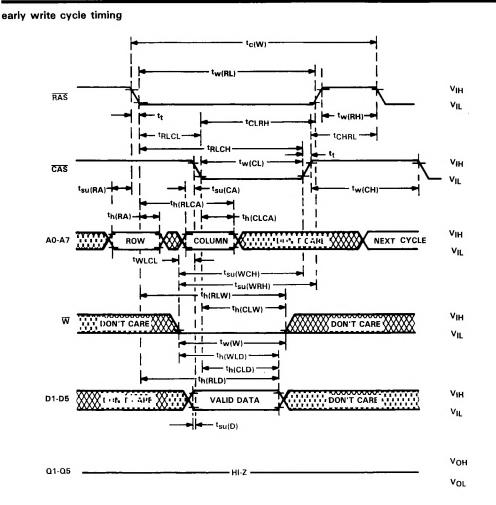

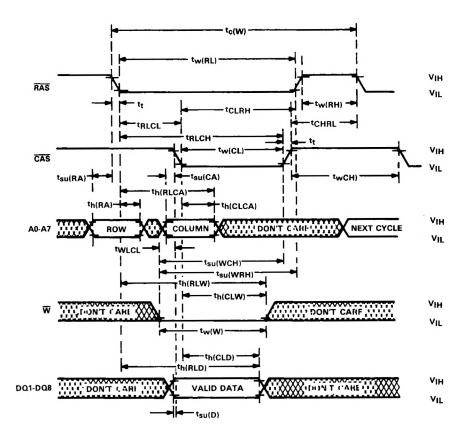

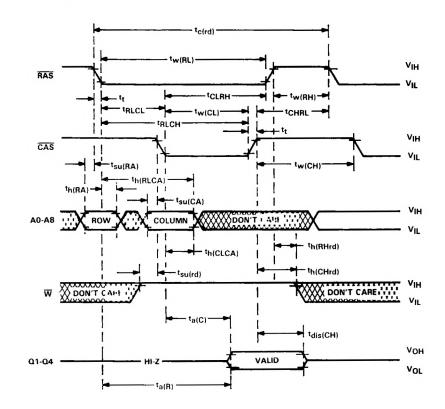

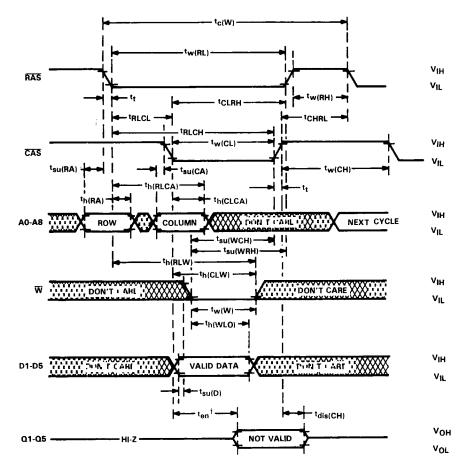

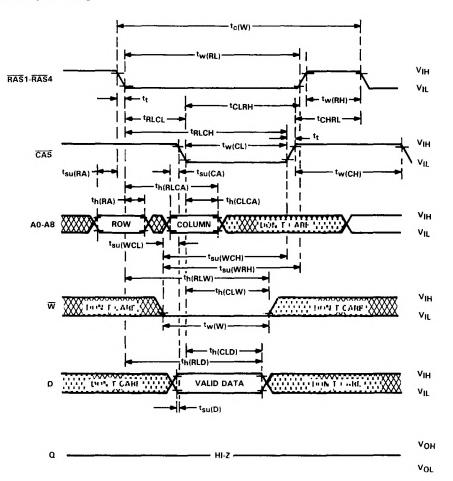

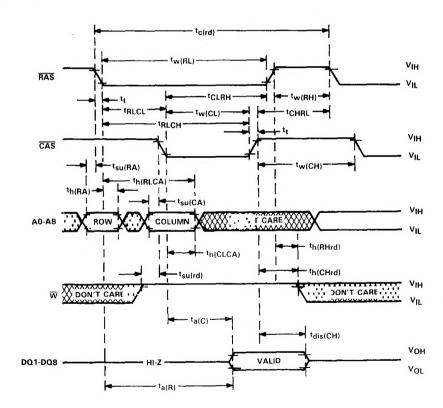

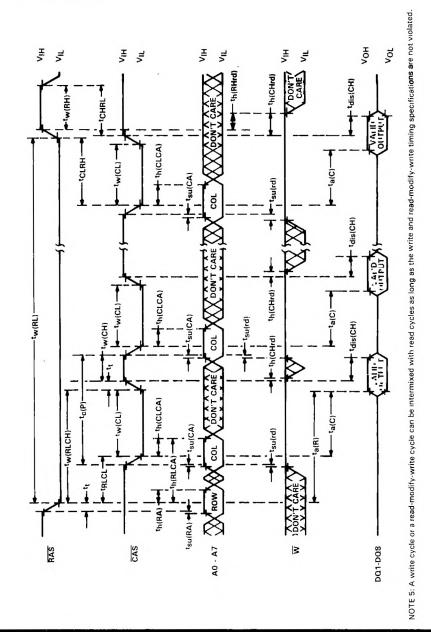

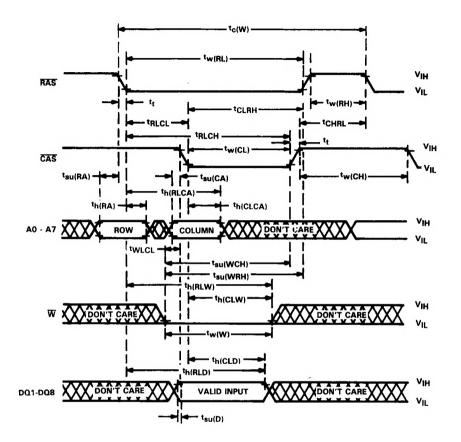

early write cycle timing

TEXAS V INSTRUMENTS

5-16

5

**Dynamic RAM Modules**

5-17

5

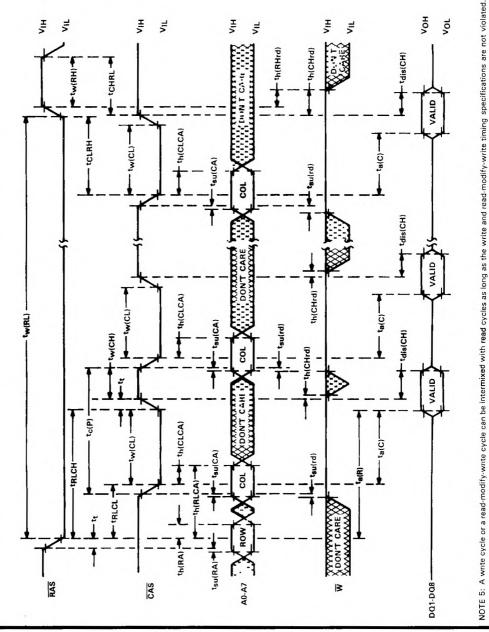

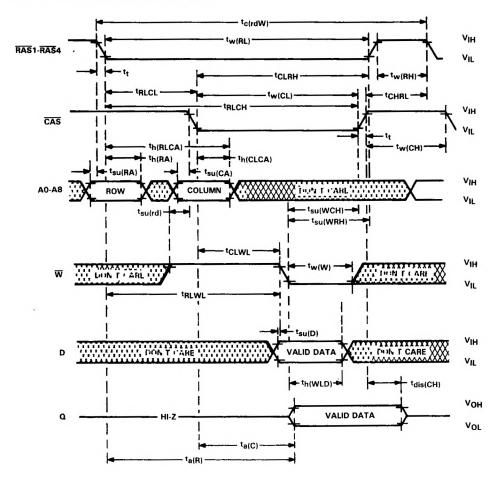

**Dynamic RAM Modules**

POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

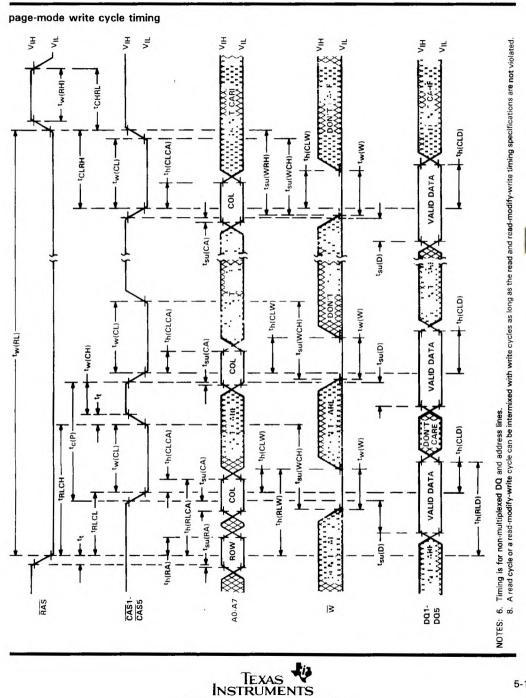

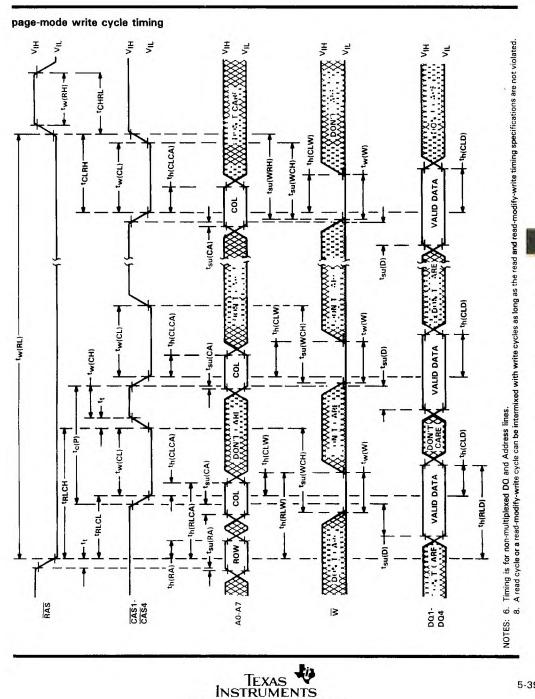

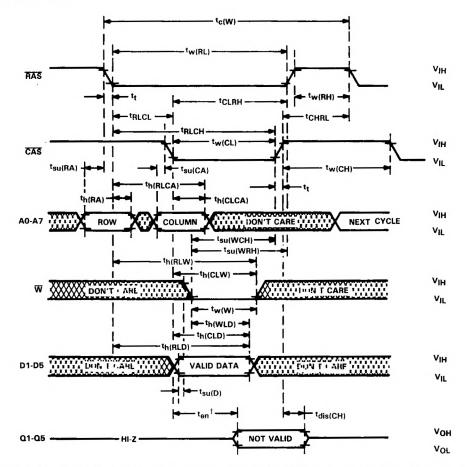

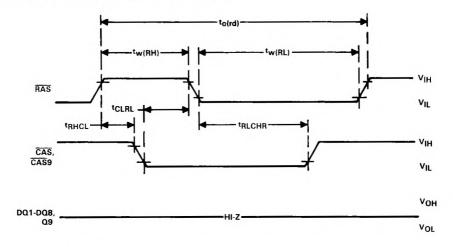

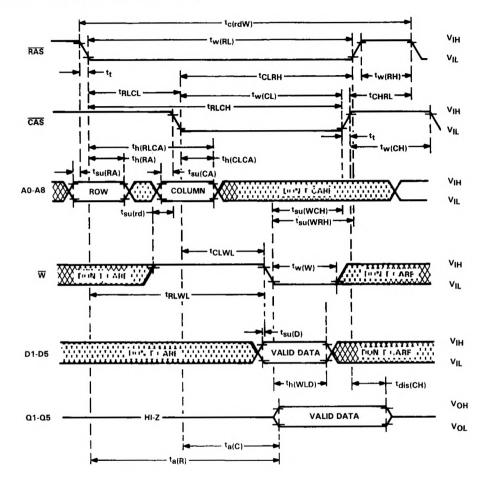

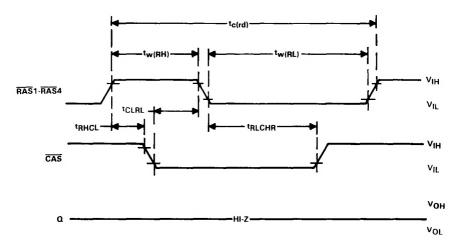

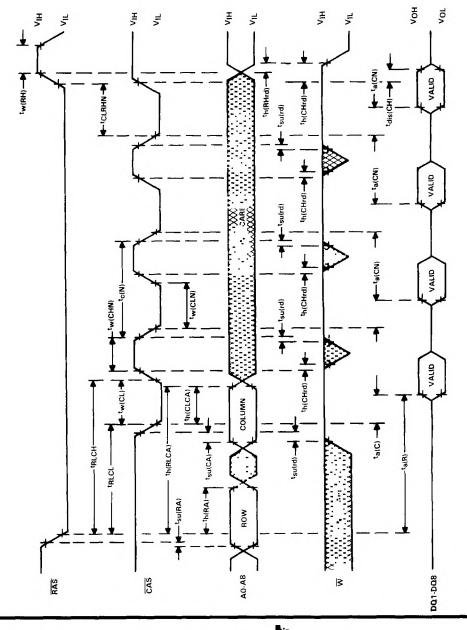

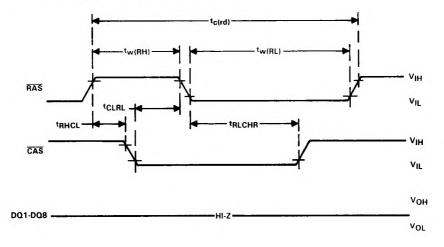

**RAS**-only refresh timing

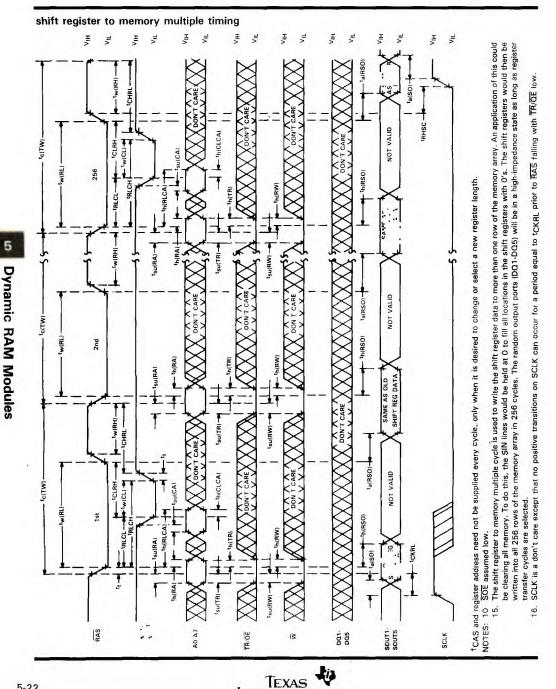

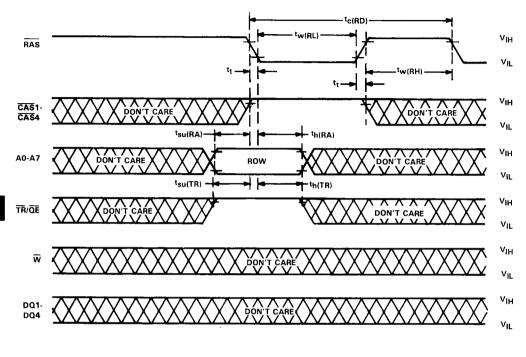

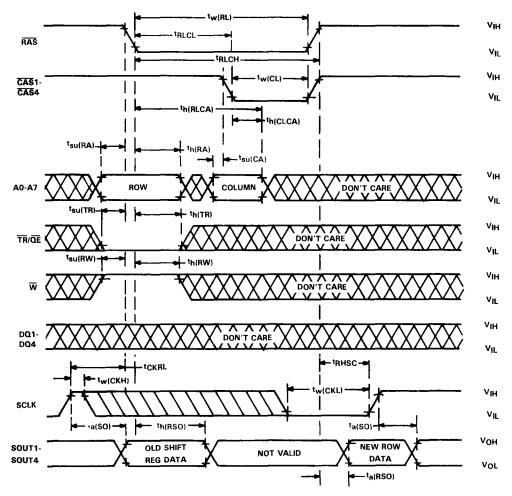

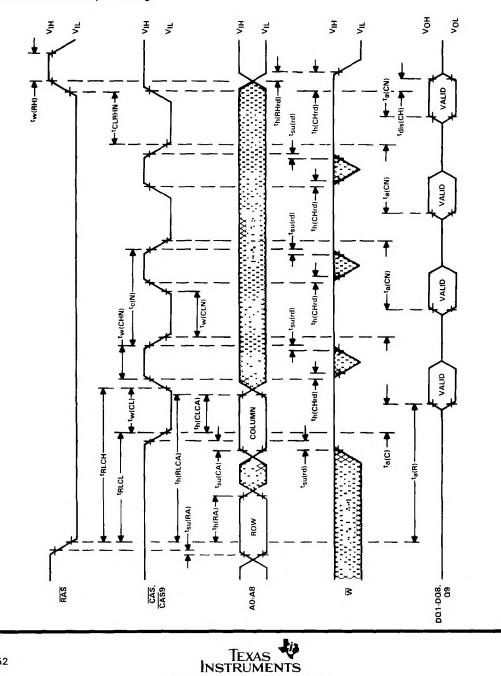

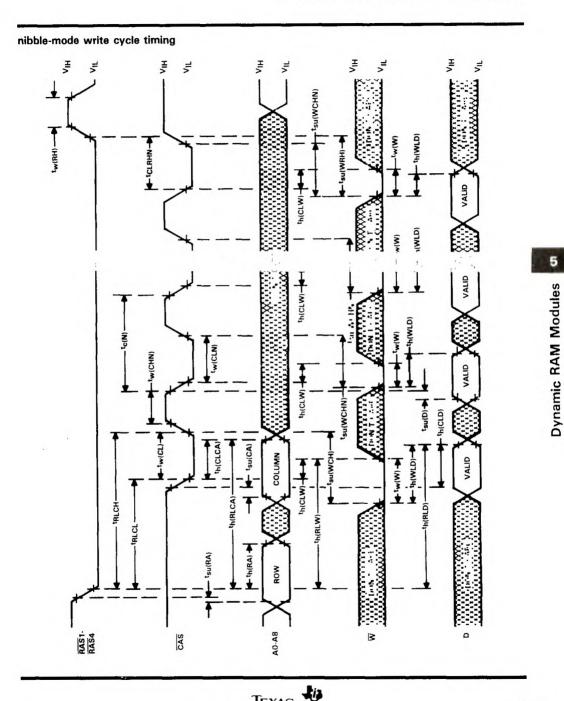

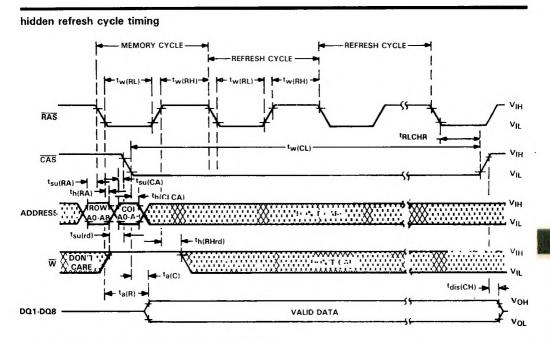

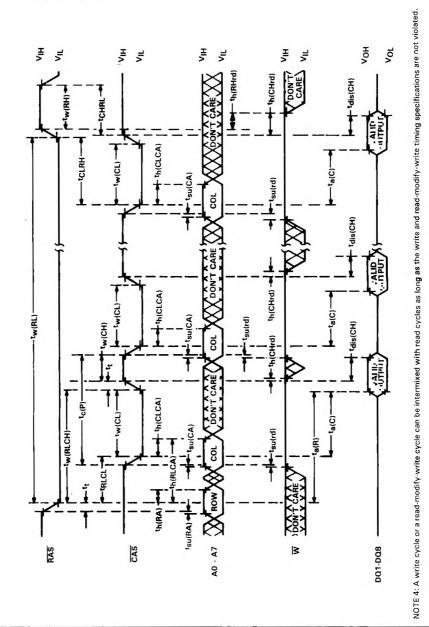

shift register to memory timing

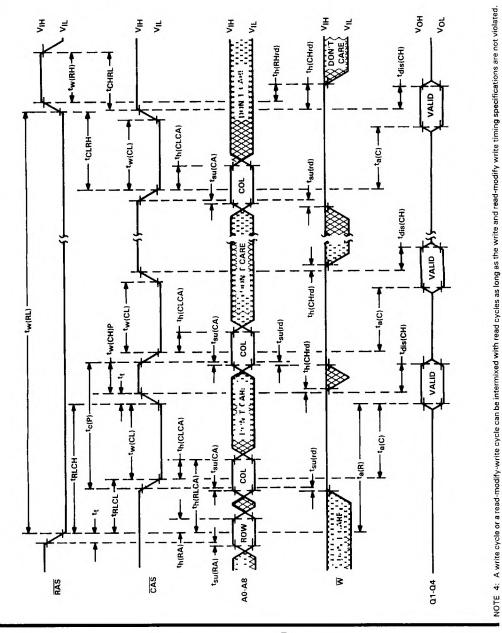

- NOTES: 9. The shift register to memory cycle is used to transfer data from the shift registers to the memory array. Every one of the 256 locations in each shift register is written into the 256 columns of the selected row. Note that the data that was in the shift registers may have resulted, either from a serial shift in or from a parallel load of the shift registers from one of the ory array rows. 10

- assumed low

- SCLK may be high or low during tw(RL)-11

Б

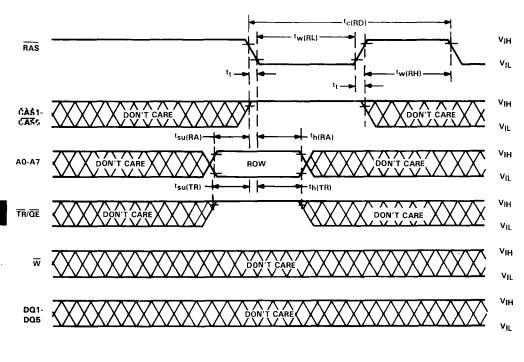

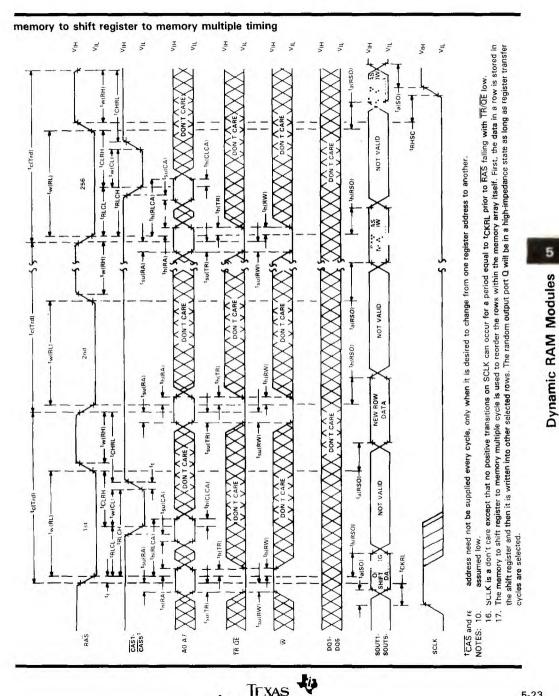

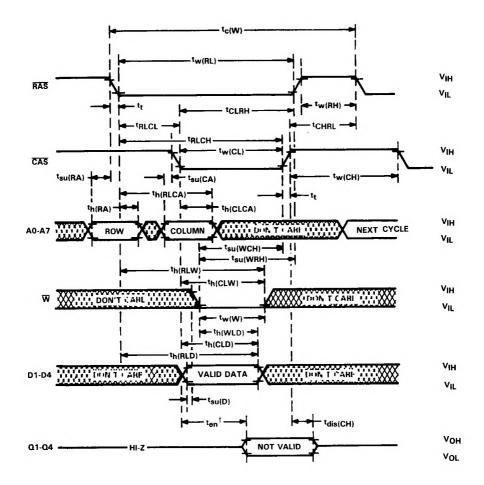

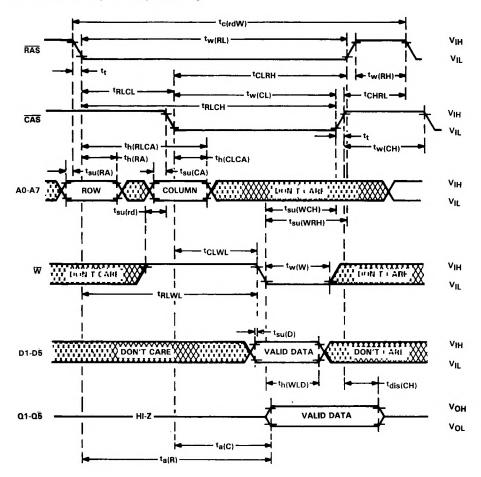

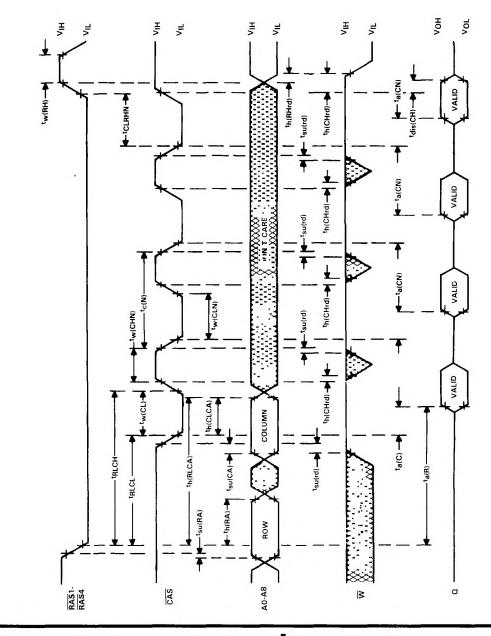

memory to shift register timing

NOTES: 10. SOE assumed low.

11. SCLK may be high or low during tw(RL).

12. The memory to shift register cycle is used to load the shift registers in parallel from the memory array. Every one of the 256 locations in each shift register are written into from the 256 columns of the selected row. Note that the data that is loaded into the shift registers may be either shifted out or written back into another row.

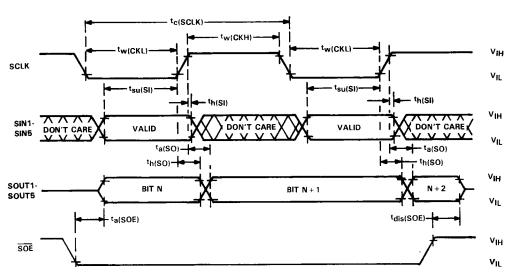

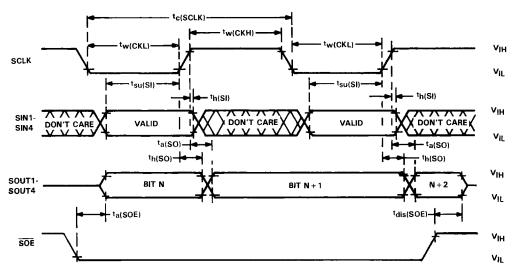

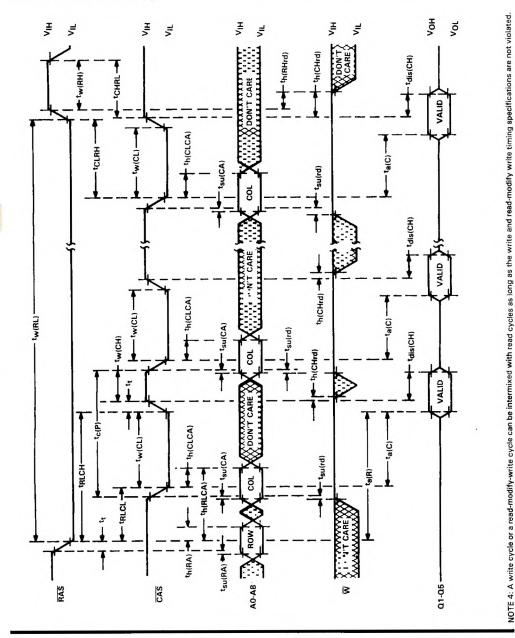

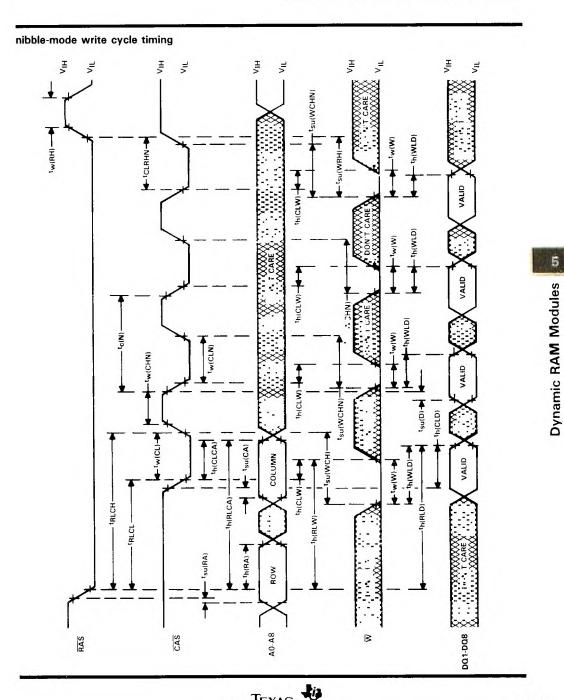

serial data shift timing

- NOTES: 13. When loading data into the shift registers from the serial input in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times.

- 14. While shifting data through the serial shift registers, the state of TR/QE is a don't care as long as TR/QE is held high when RAS goes low and t<sub>su(TR)</sub> and t<sub>h(TR)</sub> timings are observed. This requirement avoids the initiation of a register-to-memory or memory-to-register data transfer operation. The serial data transfer cycle is used to shift data in and/or out of the shift registers.

INSTRUMENTS POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

5-22

5-23

5

INSTRUMENTS POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

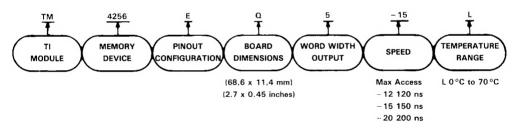

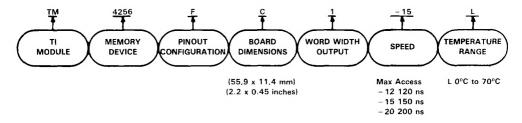

JULY1984 - REVISED NOVE \*\* \* 1985

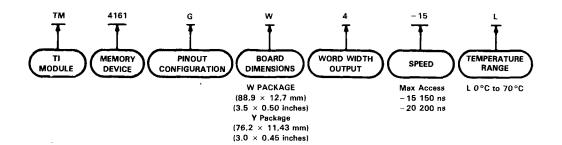

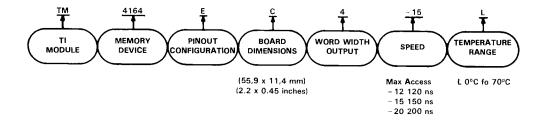

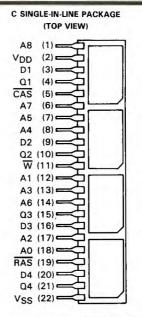

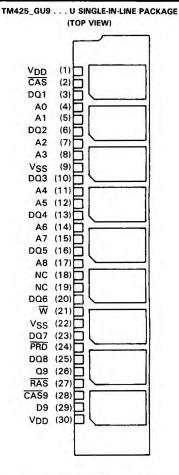

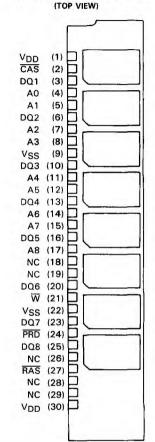

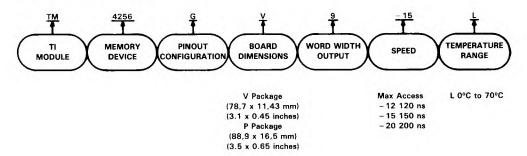

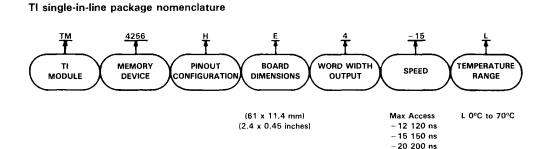

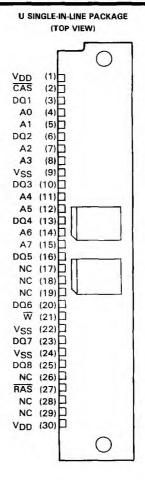

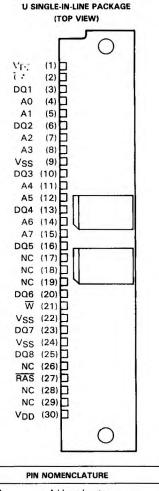

- 65,536 X 4 Organization

- Single 5-V Supply (10% Tolerance)

- 31-Pin Single-in-Line Package (SIP)

- Utilizes Four Multiport Video RAMs in Plastic Chip Carriers

- Serial In/Serial Out Capability

- Dual Accessibility One Port Sequential Access, One Port Random Access

- Four Serial Shift Registers for Sequential Access Applications, Each Comprised of Four Cascaded 64-Bit Segments

- Designed for both Video and Non-Video Applications

- Fast Serial Port . . . Can Be Configured for Video Data Rates in Excess of 150 MHz

- TR/QE as Output Enable Allows Direct Connection of DQ and Address Lines to Simplify System Design

- Separate Serial In and Serial Out to Allow Simultaneous Shift In and Out

- Supported by TI's TMS34061 Video System Controller (VSC)

- SOE Simplifies Multiplexing of Serial Data Streams

- Long Refresh Period . . . 4 ms (256 Cycles)

- All Inputs, Outputs, Clocks Fully TTL Compatible

- 3-State Outputs

- Performance Ranges:

|              | ACCESS  | ACCESS  | READ   |

|--------------|---------|---------|--------|

|              | TIME    | TIME    | OR     |

|              | ROW     | COLUMN  | WRITE  |

|              | ADDRESS | ADDRESS | CYCLE  |

|              | (MAX)   | (MAX)   | (MIN)  |

| TM4161EV4-15 | 150 ns  | 100 ns  | 240 ns |

| TM4161EV4-20 | 200 ns  | 135 ns  | 315 ns |

|              |         |         |        |

- Separate CAS Control with Common Data-In and Data-Out Lines

- Low Power Dissipation:

Operating . . . 1000 mW (Typ)

Standby . . . 320 mW (Typ)

- Operating Free-Air Temperature . . . 0 °C to 70 °C

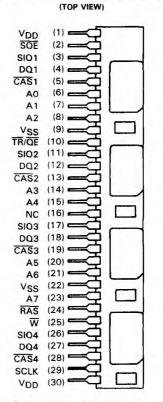

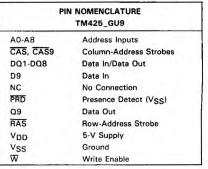

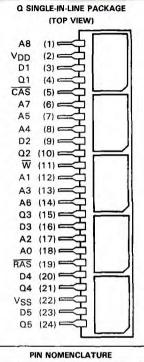

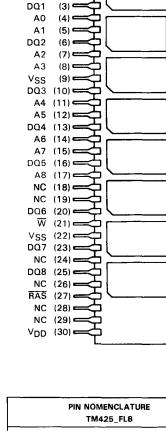

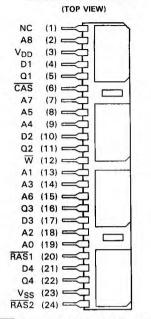

| 1 | Pil                     | PIN NOMENCLATURE                  |  |  |  |  |  |

|---|-------------------------|-----------------------------------|--|--|--|--|--|

|   | A0-A7                   | Address Inputs                    |  |  |  |  |  |

|   | CAS1-CAS4               | Column-Address Strobes            |  |  |  |  |  |

|   | DQ1-DQ4                 | Random-Access Data In/Data Out    |  |  |  |  |  |

|   | RAS                     | Row-Address Strobe                |  |  |  |  |  |

|   | SCLK                    | Serial Data Clock                 |  |  |  |  |  |

|   | SIN1-SIN4               | Serial Data In                    |  |  |  |  |  |

|   | SOE                     | Serial Output Enable              |  |  |  |  |  |

|   | SOUT1-SOUT4             | Serial Data Out                   |  |  |  |  |  |

|   | TR/QE                   | Register Transfer/Q Output Enable |  |  |  |  |  |

| Ĩ | VDD                     | 5-V Supply                        |  |  |  |  |  |

|   | VSS                     | Ground                            |  |  |  |  |  |

|   | $\overline{\mathbf{w}}$ | Write Enable                      |  |  |  |  |  |

PRODUCTION DATA documents contain information current as of publication data. Products conform to specifications per the terms of Texas Instruments standard warrenty. Production processing does not necessarily include testing of all parameters.

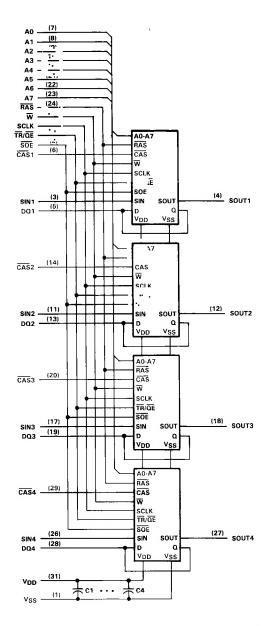

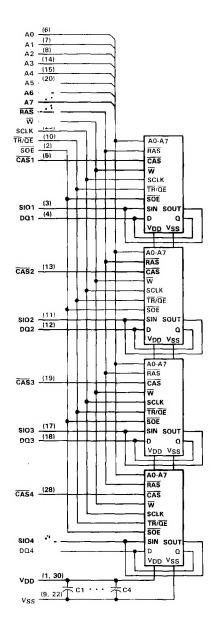

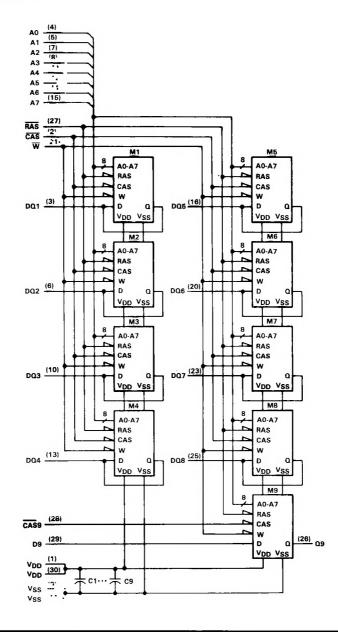

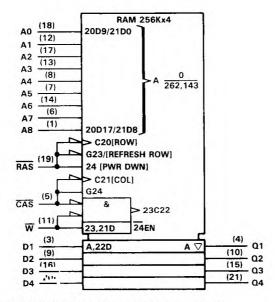

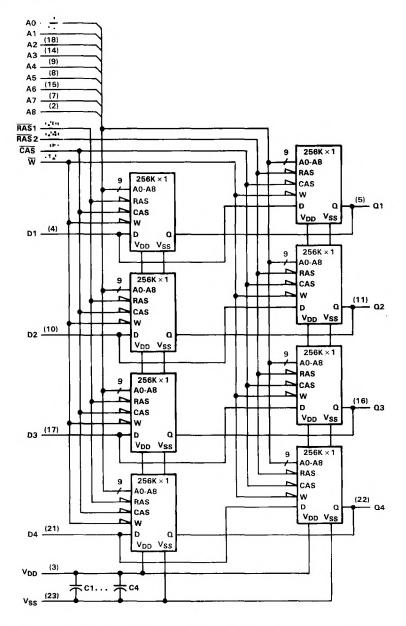

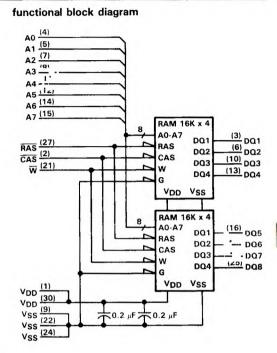

### description

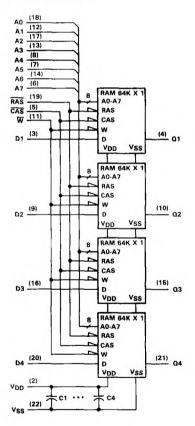

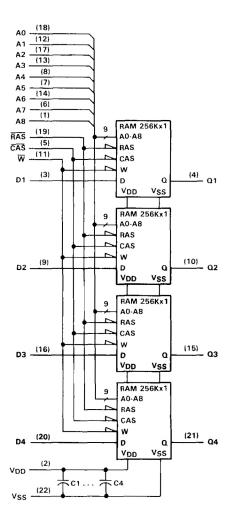

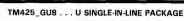

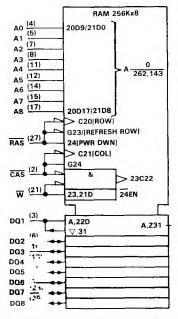

The TM4161EV4 is a 256K dual-access dynamic random-access memory module organized as 65,536  $\times$  4-bits in a 31-pin single-in-line package comprising four TMS4161FML, 65,536  $\times$  1-bit Multiport Video RAMs in 22-lead plastic chip carriers mounted on top of a substrate together with four decoupling capacitors. The random-access port makes the memory look like it is organized as 65,536 words of four bits each. The sequential access port is interfaced to four internal 256-bit dynamic shift registers each organized as four cascaded 64-bit shift register segments which are accessed serially. One, two, three, or four 64-bit shift register segments can be sequentially read out after a transfer cycle depending on a two-bit code applied to the two most significant column address inputs.

The TM4161EV4 features full asynchronous dual access capability except when transferring data between the shift registers and the memory array.

All inputs and outputs, including clocks, are compatible with Series 74 TTL. All address lines and data in are latched on chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The TM4161EV4 is guaranteed for operation from 0°C to 70°C.

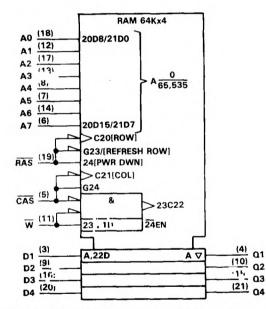

### functional block diagram

#### random-access address space to sequential-address space mapping

**Dynamic RAM Modules**

#### random-access operation

### TR/QE

The TR/QE pin has two functions. First, it selects either register transfer or random-access operation as RAS falls, and second, during a random-access operation, it functions as an output enable after CAS falls.

To use the TM4161EV4 in the random-access mode,  $\overline{TR}/\overline{QE}$  must be high as  $\overline{RAS}$  falls. Holding  $\overline{TR}/\overline{QE}$  high as  $\overline{RAS}$  falls keeps the 256 elements of the shift registers disconnected from the corresponding 256 bit lines of the maximum ry array. If data is to be shifted, the shift registers must be disconnected from the bit lines. Holding  $\frac{15}{2E}$  low as  $\overline{RAS}$  falls enables the 256 switches that connect the shift registers to the bit lines and indicates that a transfer will occur between the shift registers and one of the memory rows.

During random-access operation, once  $\overline{CAS}$  has been :...: low,  $\overline{TR}/\overline{QE}$  controls when the data will appear at the Q output (if this a read cycle). Whenever  $\overline{TI}$  :: is held high during random-access operation, the Q output will be in the high-impedance state. This feature removes the possibility of an overlap between data on the address lines and data appearing on the Q output making it possible to connect the address lines to the Q and D lines (Use of this organization prohibits the use of the early write cycle.).

### address (A0 through A7)

Sixteen address bits are required to decode 1 of 65,536 storage cell locations. Eight row-address bits are set up on pins A0 through A7 and latched onto the chip by the row-address strobe ( $\overline{RAS}$ ). Then the eight column-address bits are set up on pins A0 through A7 and latched onto the chip by the column-address strobe ( $\overline{CAS}$ ). All addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ .  $\overline{RAS}$  is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder.  $\overline{CAS}$  is used as a chip select activating the column decoder and the input and output buffers.

### write enable (W)

The read or write mode is selected through the write-enable  $(\overline{W})$  input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write-enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data inputs are disabled when the read mode is selected. The common I/O feature of the TM4161EV4 dictates the use of early write cycles to prevent contention on DQ. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , the data outputs will remain in the high-impedance state for the entire cycle permitting common I/O operation.

#### data in (DQ1-DQ4)

Data is written during a write or read-modify-write cycle. The falling edge of  $\overline{CAS}$  or  $\overline{W}$  strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle,  $\overline{W}$  is brought low prior to  $\overline{CAS}$  and the data is strobed in by  $\overline{CAS}$  with setup and hold times referenced to this signal.

### data out (DQ1-DQ4)

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan out of two Series 74 TTL loads. Data out is the same polarity as data in. The output is in the high-impedance (floating) state as long as  $\overline{CAS}$  or  $\overline{TR}/\overline{QE}$  is held high. Data will not appear on the output until after both  $\overline{CAS}$  and  $\overline{TR}/\overline{QE}$  have been brought low. In a read cycle, the guaranteed maximum output enable access time is valid only if tCQE is greater than tCQE MAX, and tRLCL is greater than tRLCL MAX. Likewise, ta(C) MAX is valid only if tRLCL is greater than '19 CL MAX. Once the output is valid, it will remain valid while  $\overline{CAS}$  and  $\overline{TR}/\overline{QE}$  are both low;  $\overline{CAS}$  or  $\overline{TR}$  '19 CL MAX. Once the output to a high-impedance state. In an early write cycle, the output is always in a high-impedance state. In a register transfer cycle, the output will always be in a high-impedance state.

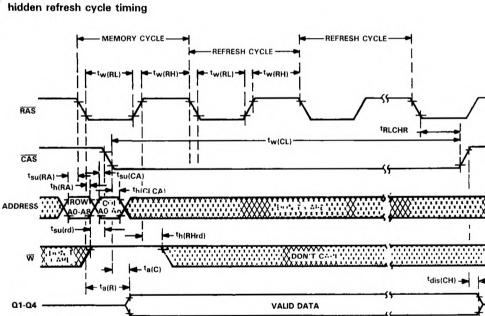

### refresh

A refresh operation must be performed at least every four milliseconds to retain data. Since the output buffer is in high-impedance state unless CAS is applied, the RAS-only refresh sequence avoids any output

during refresh. Strobing each of the 256 row addresses (A0 through A7) with  $\overline{RAS}$  causes all bits in each row to be refreshed.  $\overline{CAS}$  can remain high (inactive) for this refresh sequence to conserve power.

### page mode

Page-mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the module. Thus, the time required to setup and strobe sequential row addresses for the same page is eliminated. To extend beyond the 256 column locations on M1-M4, the row address and RAS are applied to multiple modules. CAS is then decoded to select the proper module.

#### power up

After power up, the power supply must remain at its steady-state value for 1 ms. In addition, RAS must remain high for 100  $\mu$ s immediately prior to initialization. Initialization consists of performing eight RAS cycles before proper device operation is achieved.

#### sequential-access operation

#### TR/QE

Memory transfer operations involving parallel use of the shift registers are first indicated by bringing TR/QE low before  $\overline{RAS}$  falls low. This enables the switches connecting the 256 elements of the shift registers to the 256 bit lines of the memory array. The  $\overline{W}$  line determines whether the data will be transferred from or to the shift registers.

### write enable (W)

In the sequential-access mode,  $\overline{W}$  determines whether a transfer will occur from the shift registers to the memory array, or from the memory array to the shift registers. To transfer from the shift registers to the memory array,  $\overline{W}$  is held low as  $\overline{RAS}$  falls, and, to transfer from the memory array to the shift registers,  $\overline{W}$  is held high as  $\overline{RAS}$  falls. Thus, reads and writes are always with respect to the memory array. The write setup and hold times are referenced to the falling edge of  $\overline{RAS}$  for this mode of operation.

#### row address (A0 through A7)

Eight address bits are required to select one of the 256 possible rows involved in the transfer of data to or from the shift registers. A0-A7,  $\overline{W}$ , and  $\overline{TR}/\overline{QE}$  are latched on the falling edge of  $\overline{RAS}$ .

### register column address (A7, A6)

To select one of the four shift register segments within each shift register (transfer from memory to register only), the appropriate 2-bit column address (A7, A6) must be valid when  $\overline{CAS}$  falls. However, the  $\overline{CAS}$  and segment address signals need not be supplied every transfer cycle, only when it is desired to change or select a new segment.

#### SCLK

Data is shifted in and out on the rising edge of SCLK. This makes it possible to view each shift register as though it were made of 256 rising edge D flip-flops connected D to Q. The TM4161EV4 is designed to work with a wide range duty cycle clock to simplify system design. Note that data will appear at the SOUT pins not only on the rising edge of SCLK but also after an access time of  $t_{a}(RSO)$  from RAS high during a parallel load of the shift registers.

#### SIN and SOUT

Data is shifted in through the SIN pins and is shifted out through the SOUT pins. The TM4161EV4 is designed such that it requires 3 ns hold time on SIN as SCLK rises. SOUT is guaranteed not to change for at least 8 ns after SCLK rises. When loading data into the shift registers from the serial inputs in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times. To guarantee proper serial clock sequence after power up, a transfer cycle must be initiated before a serial data stream is applied at SIN.

### SOE

The serial output enable pin controls the impedance of the serial outputs, allowing in the serial outputs allowing in the series into the same external video circuitry. When the series is at a logic low level, the SOUTs will be enabled and the proper data read out. When SOE is at a logic high level, the SOUTs will be disabled and be in the high-impedance state.

### refresh

The shift registers are also dynamic storage elements. The data held in the registers will be lost unless SCLK goes high to shift the data one bit position, a transfer write operation is invoked, or the data is reloaded from the memory array. See specifications for maximum register data retention times. Important: If the shift registers have remained idle for a time period which exceeds the maximum SCLK high or SCLK low time, the dynamic clock circuits will lose charge. Under these conditions, the shift register clocks must be re-enabled by performing any transfer cycle before data can be shifted into or out of the shift registers.

### single-in-line package and components

PC substrate: 0,79 mm (0.031 inch) minimum thickness Bypass capacitors: Multilayer ceramic Leads: Tin/lead solder coated over phosphor-bronze

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Voltage range on any pin except VDD and data out (see Note 1) | - 1.5 V to 10 V |

|---------------------------------------------------------------|-----------------|

| Voltage range on VDD supply and data out with respect to VSS  | 1 V to 6 V      |

| Short circuit output current                                  | 50 mA           |

| Power dissipation                                             | 4 W             |

| Operating free-air temperature range                          | 0°C to 70°C     |

| Storage temperature range                                     | 65°C to 150°C   |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

### recommended operating conditions

|     |                                             | MIN  | NOM | MAX    | UNIT |

|-----|---------------------------------------------|------|-----|--------|------|

| VDD | Supply voltage                              | 4.5  | 5   | 5.5    | V    |

| Vss | Supply voltage                              |      | 0   |        | ۷    |

| VIH | High-level input voltage                    | 2.4  |     | DD+0.3 | ٧    |

| VIL | Low-level input voltage (see Notes 2 and 3) | -0.6 |     | 0.8    | V    |

| TA  | Operating free-air temperature              | 0    |     | 70     | °C   |

NOTES: 2. The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

Due to input protection circuitry, the applied voltage may begin to clamp at -0.6 V; test conditions must comprehend this occurrence.

4. See application report entitled "TMS4164A and TMS4416 Input Protection Diode" on page 9-5.

|                   | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                                                                                       | TM4161EV4-15 |                  |     | TM4161EV4-20 |      |      | UNIT |

|-------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-----|--------------|------|------|------|

|                   | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                                                                                       | MIN          | TYP <sup>†</sup> | MAX | MIN          | TYPT | MAX  | UNI  |

| Vон               | High-level output voltage<br>(DQ1-DQ4, SOUT1-SOUT4)      | l <sub>OH</sub> = -5 mA                                                                                                                                                                                                               | 2.4          |                  |     | 2.4          |      |      | v    |

| VOL               | Low-level output voltage<br>(DQ1-DQ4, SOUT1-SOUT4)       | I <sub>OL</sub> = 4.2 mA                                                                                                                                                                                                              |              |                  | 0.4 |              |      | 0.4  | v    |

| ų                 | Input current (leakage)                                  | $V_I = 0 V \text{ to } 5.8 V,$<br>$V_{DD} = 5 V,$<br>All other pins = 0 V                                                                                                                                                             |              |                  | ±10 |              |      | ± 10 | μΑ   |

| 0                 | Output current (leakage)<br>(DQ1-DQ4, SOUT1-SOUT4)       | $V_{O} = 0.4 V \text{ to } 5.5 V,$<br>$V_{DD} = 5 V$                                                                                                                                                                                  |              |                  | ±10 |              |      | ±10  | μA   |

| וסס <sup>ן</sup>  | Average operating current<br>during read or write cycle  | t <sub>c(rd)</sub> = minimum cycle time,<br>TR/ΩE low after RAS falls, <sup>‡</sup><br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ4<br>and SOUT1-SOUT4                                                                           |              | 200              | 280 |              | 200  | 280  | mA   |

| IDD2 <sup>§</sup> | Standby current                                          | After 1 RAS cycle,<br>RAS and CAS high,<br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ4<br>and SOUT1-SOUT4                                                                                                                       |              | 64               | 80  |              | 64   | 80   | mA   |

| IDD3              | Average refresh current                                  | t <sub>c(rd)</sub> = minimum cycle time,<br>CAS high, RAS cycling,<br>SCLK and SIN low,<br>SOE high, TR/QE high,<br>No load on DQ1-DQ4<br>and SOUT1-SOUT4                                                                             |              | 168              | 220 |              | 148  | 220  | mA   |

| IDD4              | Average page-mode current                                | t <sub>c(P)</sub> = minimum cycle time,<br>RAS low, CAS cycling,<br>TR/QE low after RAS falls,<br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ4<br>and SOUT1-SOUT4                                                                |              | 180              | 220 |              | 160  | 220  | mA   |

| IDD5              | Average shift register<br>current (includes IDD2)        | $\overline{RAS}$ and $\overline{CAS}$ high,<br>$t_{c(SCLK)} = t_{c(SCLK)}$ min,<br>No load on DQ1-DQ4<br>and SOUT1-SOUT4                                                                                                              |              | 120              | 160 |              | 120  | 160  | mA   |

| IDD6              | Worst case average<br>DRAM and shift<br>register current | $\label{eq:tc(rd)} = \mbox{minimum cycle time,} \\ t_{c(SCLK)} = \mbox{minimum cycle time,} \\ \hline TR/\overline{\Omega E} \mbox{ low after RAS falls,} \\ No \mbox{ load on } DQ1-DQ4 \\ \mbox{and } SOUT1-SOUT4 \\ \end{tabular}$ |              | 340              | 380 |              | 320  | 360  | mA   |

### electrical characteristics over full range of recommended operating conditions (unless otherwise noted)

$^{\dagger}All$  typical values are at  $T_A=25\,^oC$  and nominal supply voltages. \*See appropriate timing diagram. §V\_{JL}>~-0.6 V

### capacitance over recommended supply voltage and operating free-air temperature range, $f\,=\,1\,\,\text{MHz}$

|          | PARAMETER                                  | MAX | UNIT |

|----------|--------------------------------------------|-----|------|

| Ci(A)    | Input capacitance, address inputs          | 35  |      |

| Ci(DQ)   | Input capacitance, data inputs             | 20  |      |

| Ci(RC)   | Input capacitance, strobe inputs           | 40  |      |

| Ci(W)    | Input capacitance, write enable input      | 40  | pF   |

| Ci(CK)   | Input capacitance, serial clock            | 30  | pr   |

| Ci(SI)   | Input capacitance, serial in               | 20  |      |

| Ci(SOE)  | Input capacitance, serial output enable    | 30  |      |

| Ci(TR)   | Input capacitance, register transfer input | 30  |      |

| Co(SOUT) | Output capacitance, serial out             | 20  |      |

<sup>†</sup>All typical values are at  $T_A = 25 \,^{\circ}C$  and nominal supply voltages.

# switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 1)

| PARAMETER                         |                                          | TEST CONDITIONS                      | ALT.             | TM4161EV4-15 | TM4161EV4-20 | UNIT |

|-----------------------------------|------------------------------------------|--------------------------------------|------------------|--------------|--------------|------|

|                                   |                                          | TEST CONDITIONS                      | SYMBOL           | MIN MAA      | MIN MAX      |      |

| ta(C)                             | Access time from CAS                     | C <sub>L</sub> = 100 pF              | tCAC             | 100          | 135          |      |

| <sup>t</sup> a(QE)                | Access time of Q from<br>TR/QE low       | $C_L = 100 \text{ pF}$               |                  | 40           | 50           |      |

| t <sub>a(R)</sub>                 | Access time from RAS                     | $t_{RLCL} = MAX,$<br>$C_L = 100  pF$ | <sup>t</sup> RAC | 150          | 200          |      |

| ta(RSO)                           | SOUT access time from<br>RAS high        | $C_L = 30  pF$                       |                  | 65           | 85           |      |

| ta(SOE)                           | Access time from SOE<br>low to SOUT      | C <sub>L</sub> = 30 pF               |                  | 30           | 30           | ns   |

| ta(SO)                            | Access time from SCLK                    | CL = 30 pF                           |                  | 45           | 50           |      |

| <sup>t</sup> dis(CH) <sup>‡</sup> | Q output disable time from CAS high      | C <sub>L</sub> = 100 pF              | tOFF             | 40           | 40           |      |

| t <sub>dis(QE)</sub> ‡            | Q output disable time from TR/QE high    | $C_L = 100 \text{ pF}$               |                  | 40           | 40           |      |

| tdis(SOE) <sup>‡</sup>            | Serial output disable time from SOE high | $C_L = 30 \text{ pF}$                |                  | 30           | 30           |      |

<sup>†</sup>Figure 1 shows the load circuit.

<sup>+</sup>The maximum values for t<sub>dis(CH)</sub>, t<sub>dis(QE)</sub>, and t<sub>dis(SOE)</sub> define the time at which the output achieves the open circuit condition and are not referenced to V<sub>OH</sub> or V<sub>OL</sub>.

|                       |                                                        | ALT.             | TM416 | 1EV4-15           | TM416 | EV4-20  | UNIT |

|-----------------------|--------------------------------------------------------|------------------|-------|-------------------|-------|---------|------|

|                       |                                                        | SYMBOL           | MIN   | MAX               | MIN   | MAX     | UNH  |

| t <sub>c(P)</sub>     | Page-mode cycle time                                   | tPC              | 100   |                   |       |         | ns   |

| tc(rd)                | Read cycle time <sup>†</sup>                           | tRC              | 240   |                   | 315   |         | ns   |

| tc(W)                 | Write cycle time                                       | twc              | 240   |                   | 315   |         | ns   |

| tc(TW)                | Transfer write cycle time <sup>‡</sup>                 |                  | 240   |                   | 315   |         | ns   |

| tc(Trd)               | Transfer read cycle time                               |                  | 240   |                   | 315   |         | ns   |

| tc(SCLK)              | Serial-clock cycle time                                | tscc             | 45    | 50,000            | 50    | 50,000  | ПS   |

| tw(CH)                | Pulse duration, CAS high (precharge time)§             | tCP              | 50    | 2.5               | 80    |         | ns   |

| tw(CL)                | Pulse duration, CAS low                                | <sup>t</sup> CAS | 100   | 10,000            | 135   | 10,000  | ns   |

| tw(RH)                | Pulse duration, RAS high (precharge time)              | tRP              | 80    |                   | 105   |         | ns   |

| tw(RL)                | Pulse duration, RAS low                                | tRAS             | 150   | 10,000            | 200   | 10,000  | ns   |

| tw(W)                 | Write pulse duration                                   | tWP              | 45    |                   | 45    |         | пѕ   |

| tw(CKL)               | Pulse duration, SCLK low                               |                  | 10    | 6 I.              | 10    |         | ns   |

| tw(CKH)               | Pulse duration, SCLK high                              |                  | 12    |                   | 12    |         | ПS   |

| tw(QE)                | TR/QE pulse duration low time (read cycle)             |                  | 40    |                   | 40    |         | ns   |

| tt                    | Transition times (rise and fall)<br>RAS, CAS, and SCLK | ۲Ť               | 3     | 50                | 3     | 50      | ns   |

| tsu(CA)               | Column-address setup time                              | tASC             | 0     |                   | 0     | 1990    | ns   |

| tsu(RA)               | Row-address setup time                                 | tASR             | 0     |                   | 0     |         | ns   |

| <sup>t</sup> su(RW)   | W setup time before RAS low<br>with TR/QE low          |                  | 0     |                   | 0     |         | ns   |

| t <sub>su(D)</sub>    | Data setup time                                        | tDS              | 0     | 01.0              | 0     | -2 - 22 | ns   |

| tsu(rd)               | Read-command setup time                                | tRCS             | 0     |                   | 0     | 5 i i i | ns   |

| t <sub>su</sub> (WCL) | Early write-command setup time before CAS low          | twcs             | - 5   |                   | - 5   |         | ns   |

| t <sub>su</sub> (WCH) | Write-command setup time before CAS high               | tCWL             | 40    |                   | 60    |         | ns   |

| t <sub>su</sub> (WRH) | Write-command setup time before RAS high               | tRWL             | 40    |                   | 60    |         | ns   |

| tsu(TR)               | TR/QE setup time before RAS low                        |                  | 0     |                   | 0     |         | ns   |

| tsu(SI)               | Serial-data setup time before SCLK high                | 1                | 6     | · · · · · · · · · | 6     | -       | ns   |

| th(SI)                | Serial-data-in hold time after SCLK high               |                  | 3     |                   | 3     |         | ns   |

| th(CLCA)              | Column-address hold time after CAS low                 | <sup>t</sup> CAH | . 45  |                   | 55    |         | ns   |

| th(RA)                | Row-address hold time                                  | tRAH             | 20    |                   | 25    |         | ns   |

| th(RW)                | W hold time after RAS low with TR/QE low               |                  | 20    |                   | 20    |         | ns   |

| th(RLCA)              | Column-address hold time after RAS low                 | tAR              | 95    |                   | 120   |         | ns   |

| th(CLD)               | Data hold time after CAS low                           | tDH              | 60    |                   | 80    |         | ns   |

| th(RLD)               | Data hold time after RAS low                           | tDHR             | 110   |                   | 145   |         | ns   |

| th(WLD)               | Data hold time after ₩ low                             | tDH              | 45    |                   | 55    |         | ns   |

| th(CHrd)              | Read-command hold time after CAS high                  | tRCH             | 0     |                   | 0     |         | ns   |

### timing requirements over recommended supply voltage range and operating free-air temperature range

(Continued next page.)

NOTE 5: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, VIL max and VIH min must be met at the 10% and 90% points.

<sup>†</sup>All cycle times assume  $t_t = 5$  ns except  $t_{c(SCLK)}$  which assumes  $t_t = 3$  ns. <sup>‡</sup>Multiple transfer write cycles require separation by either a 500 ns RAS-precharge interval or any other active RAS-cycle. SPage-mode only.

|                      |                                                                                                                | ALT.             | TM4161EV4-15 |        | TM4161EV4-20 |        |      |

|----------------------|----------------------------------------------------------------------------------------------------------------|------------------|--------------|--------|--------------|--------|------|

|                      |                                                                                                                | SYMBOL           | MIN          | MAX    | MIN          | MAX    | UNIT |

| th(RHrd)             | Read-command hold time after RAS high                                                                          | <sup>t</sup> RRH | 5            |        | 5            |        | ns   |

| th(CLW)              | Write-command hold time after CAS low                                                                          | tWCH             | 60           |        | 80           |        | ns   |

| th(RLW)              | Write-command hold time after RAS low                                                                          | tWCR             | 110          |        | 145          |        | ns   |

| t <sub>h</sub> (RSO) | Serial-data-out hold time after<br>RAS low with TR/QE low                                                      |                  | 30           |        | 30           |        | ns   |

| th(SO)               | Interout hold time after SCLK high                                                                             |                  | 8            |        | 8            |        | ns   |

| th(TR)               | . nold time after RAS low (transfer)                                                                           |                  | 20           |        | 20           |        | ns   |

| TRLCH                | Delay time, RAS low to CAS high                                                                                | tCSH             | 150          |        | 200          |        | ns   |

| tCHRL                | Delay time, CAS high to RAS low                                                                                | tCRP             | 0            |        | 0            |        | ΠS   |

| <sup>t</sup> CLQEH   | Delay time, CAS low to OF high                                                                                 |                  | 100          |        | 135          |        | ns   |

| <sup>t</sup> CLRH    | Delay time, CAS low to migh                                                                                    | tRSH             | 100          |        | 135          |        | ns   |

| <sup>t</sup> CQE     | Delay time, CAS low to ue low<br>(maximum value specified only<br>to guarantee t <sub>a(QE)</sub> access time) |                  |              | 60     |              | 85     | ns   |

| TRHSC                | Delay time, RAS high to SCLK high                                                                              |                  | 80           | 50,000 | 80           | 50,000 | ns   |

| TRLCL                | Delay time, RAS low to CAS low (maximum value specified only to guarantee access time)                         | tRCD             | 25           | 50     | 30           | 65     | ns   |

| <sup>t</sup> CKRL    | Delay time, SCLK high before<br>RAS low with TR/QE low¶                                                        |                  | 10           | 50,000 | 10           | 50,000 | ns   |

| trf(MA)              | Refresh time interval, memory array                                                                            | tREF1            |              | 4      |              | 4      | ms   |

| trf(SR)              | Refresh time interval, shift register#                                                                         | tREF2            |              | 50,000 |              | 50,000 | ns   |

# timing requirements over recommended supply voltage range and operating free-air temperature range (concluded)

NOTE 5: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, VIL max and VIH min must be met at the 10% and 90% points.

SCLK may be high or low during  $t_{W(RL)}$ , but there can not be any positive edge transitions on SCLK for a minimum of 10 ns prior to RAS going low with TR/QE low (i.e., before a transfer cycle).

#See "refresh" on page 5-31.

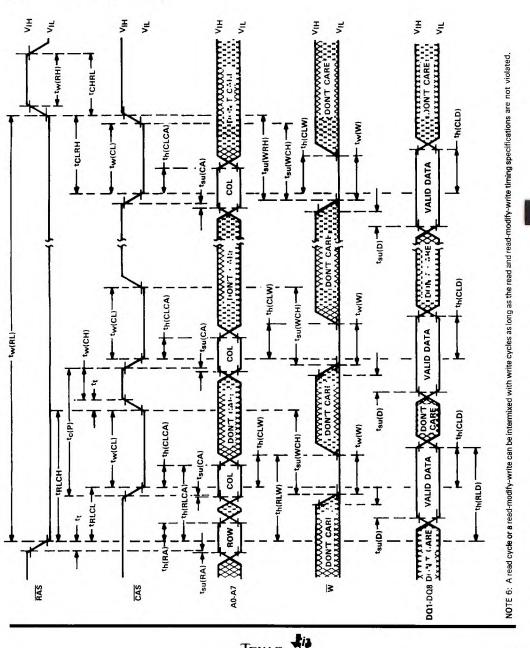

### PARAMETER MEASUREMENT INFORMATION

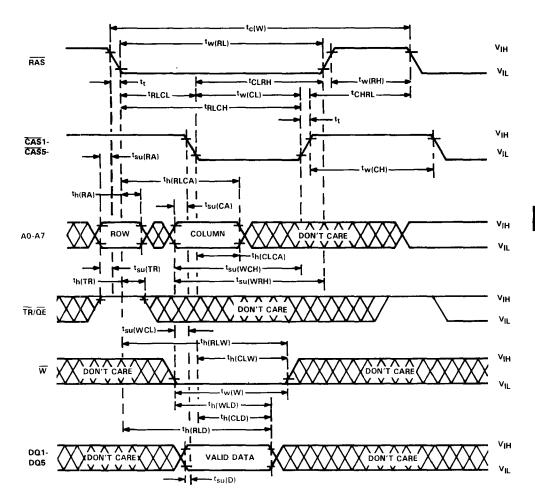

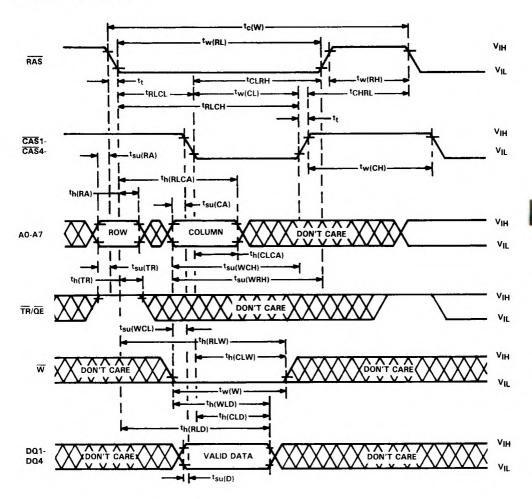

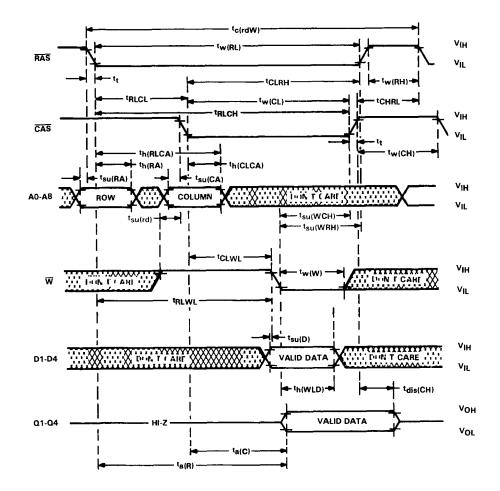

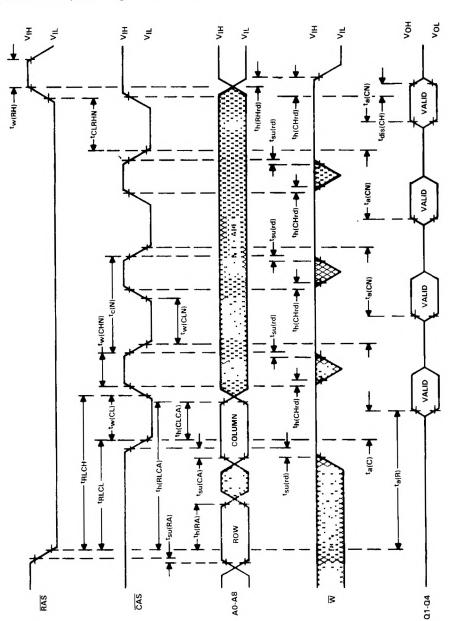

read cycle timing

early write cycle timing

5

TEXAS V INSTRUMENTS

5-38

5

POST OFFICE BOX 1443 . HOUSTON TEXAS 77001

5-39

5

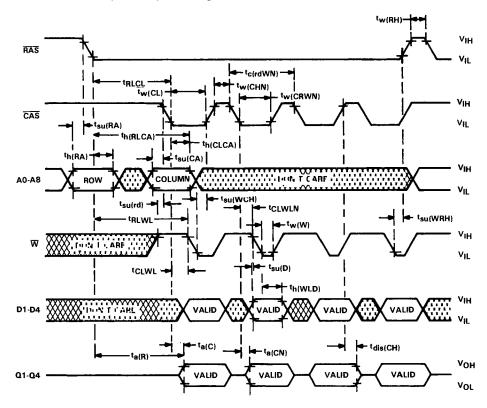

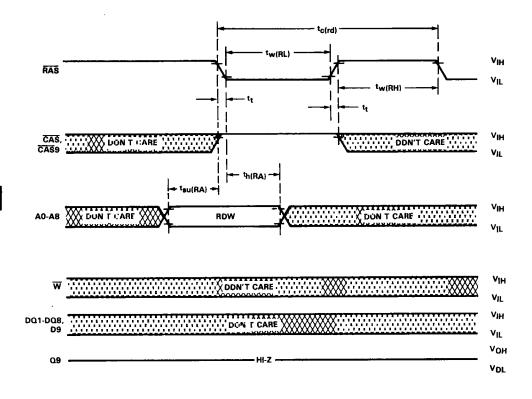

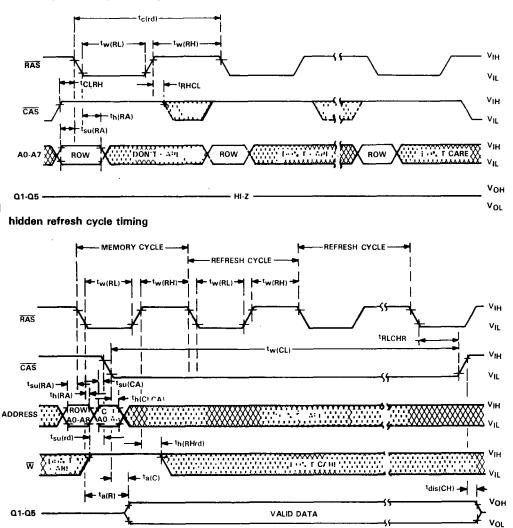

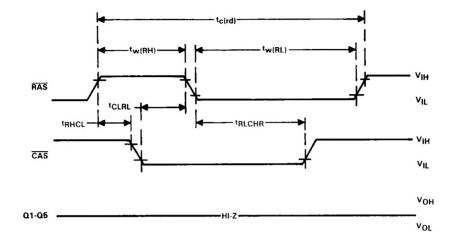

RAS-only refresh timing

**Dynamic RAM Modules**

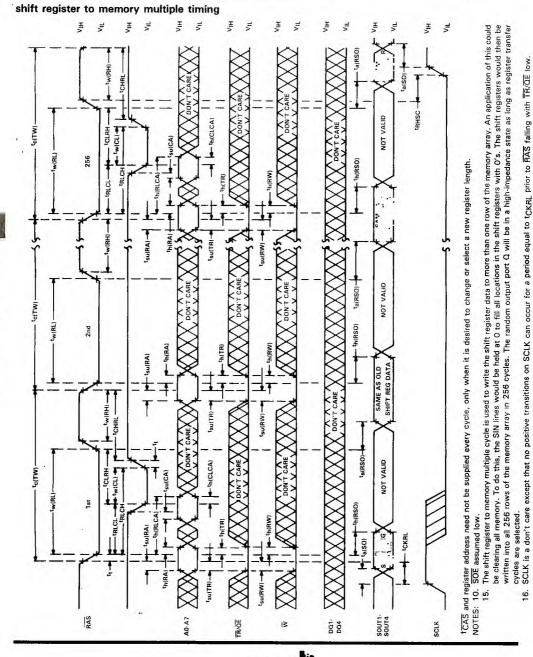

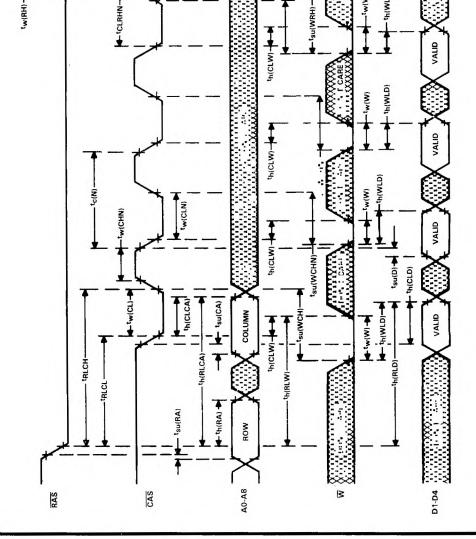

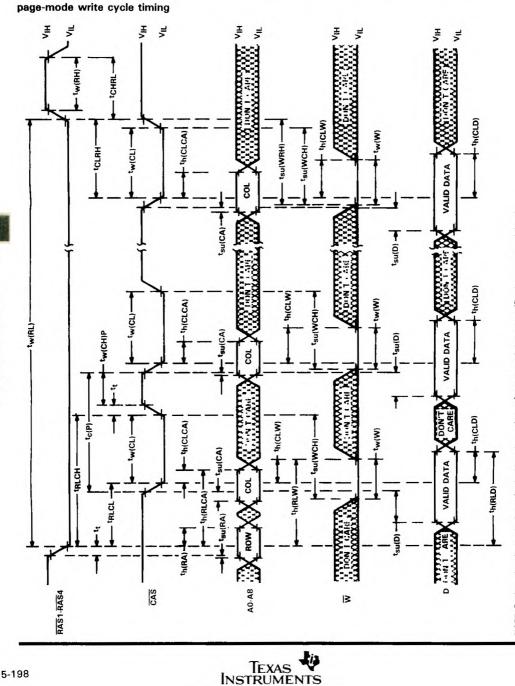

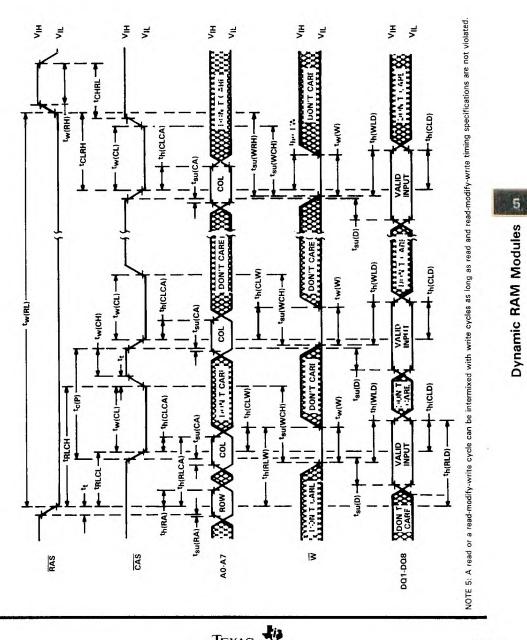

shift register to memory timing

NOTES: 9. The shift register to memory cycle is used to transfer data from the shift registers to the memory array. Every one of the 256 locations in each shift register is written into the 256 columns of the selected row. Note that the data that was in the shift registers may have resulted, either from a serial shift in or from a parallel load of the shift registers from one of the 1 m my array rows.

10. 'ssumed low.

11. SULK may be high or low during tw(RL).

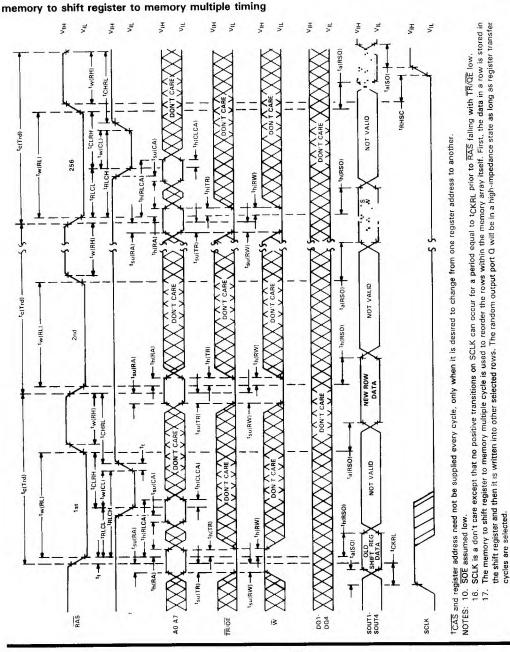

5