# CHAPTER 4 Hardware Design: Architecture and Interfacing Techniques

## INTRODUCTION

Hardware Design: Architecture and Interfacing Techniques

#### INTRODUCTION

Describing the 9900 system from a hardware standpoint clearly requires detailed descriptions of a large number of design features as well as the interaction between the 9900 and peripheral circuits. In this chapter, material is arranged to develop a 9900 system from the viewpoint of the 9900 microprocessor chip. In the architecture section, the concepts of instruction fetch and decode, the memory-to-microprocessor bus structures, and memory partitioning (the use of volatile and non-volatile memories) are explained. Other topics include descriptions of the registers on the microprocessor chip and the working registers, the concept of memory-to-memory architecture, timing and descriptions of interface signals.

A special section covers memory in detail, especially the controls and timing, multichip memory structure, static and dynamic RAM, and DMA (direct memory access).

Following the architecture and memory sections are sections devoted to the instruction set, design considerations for input/output techniques especially in CRU development, the interrupt structure and electrical requirements.

A special section devoted to the unique features of the single chip microcomputer, the TMS9940, is included at the end of the chapter.

Information in this chapter flows from the most basic fundamentals to an understanding of the more complex design features of the 9900 and the chip family. When very specific and detailed information regarding pin assignments and speed is given, the TMS9900 device specifications are used. These examples will give direction and illustration for interpreting the data sheet information found in Chapter 8.

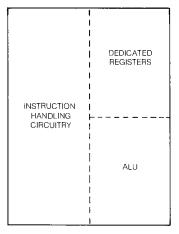

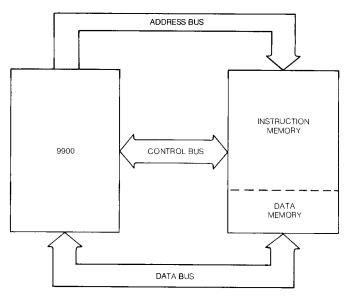

The 9900 family of 16-bit microprocessors includes several device types each aimed at a specific market segment. The same basic architecture and instruction set are maintained throughout. Consider first the single-chip microprocessor which consists of an ALU (arithmetic and logic unit), a few registers, and instruction handling circuitry (*Figure 4-1*). There is no memory on the chip for instructions and data so it must be interfaced to memory devices, usually RAM for data (and instructions which must be modified) and ROM, PROM, or EPROM for instructions (*Figure 4-2*). It is often desirable to store instructions in a non-volatile memory to eliminate the requirement for loading the program into memory immediately following application of power. This is especially important in dedicated applications where the program is fixed and power off-on cycles are common occurrences.

The microprocessor is connected to memory devices and external input/output (I/O) devices via sets of signals or busses (*Figure 4-2*). An address bus selects a word of memory. The contents of this word will be transferred to or from the microprocessor via the data bus. Control signals required to effect the transfer of information between the microprocessor and the memory are grouped into a control bus.

#### Hardware Design: Architecture and Interfacing Techniques

## INTRODUCTION

Figure 4-1. The 9900 Microprocessor

The interface to external devices (I/O) may be accomplished by using the address, data and control busses. This technique is known as parallel I/O or memory mapped I/O because data is transferred in parallel and the I/O devices occupy locations in the memory address space.

Figure 4-2. 9900 Microprocessor and Memory

### INTRODUCTION

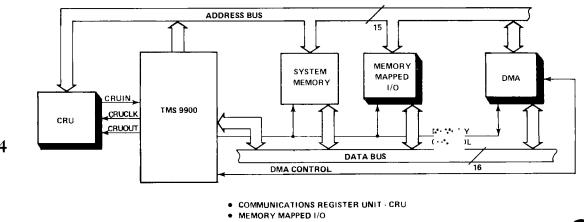

The extension of parallel I/O is direct memory access (DMA). External hardware is employed to act as a separate special purpose processor for transferring large blocks of contiguous memory words to or from an external device (such as a disc memory). Once such a transfer is set up (via a string of instructions in the program), the DMA controller automatically synchronizes the transfer of data between the external device and memory, sharing the buses timewise with the microprocessor.

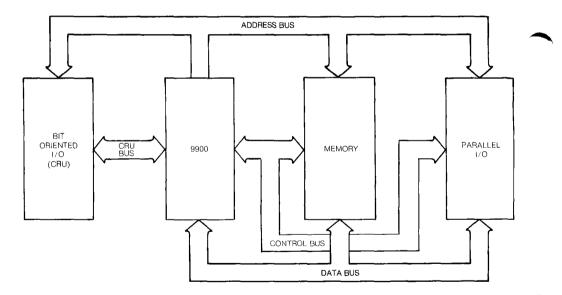

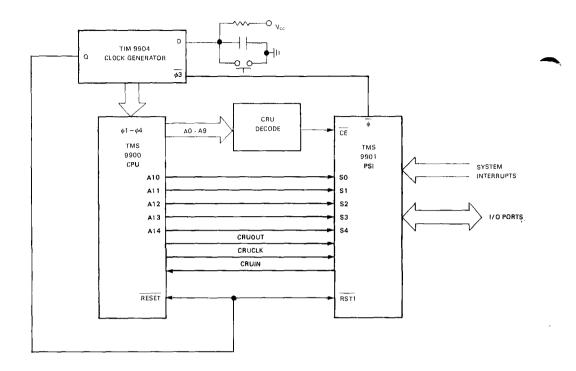

The 9900 architecture includes one other important I/O technique. Designed primarily for single bit I/O transfers, the communications register unit (CRU) provides a powerful alternative to parallel, memory mapped I/O (*Figure 4-3*). The address bus is used to select one of 4096 individual input or output bits in the CRU address space. During the execution of one of the single bit CRU instructions, the processor transfers one bit in or out. Multiple bit instructions are also available which provide for transfer of up to sixteen bits via a single CRU operation.

While this chapter describes primarily the basic TMS9900 16-bit microprocessor, all of the 9900 family CPU's are covered in detail in the *Product Data* chapter.

Figure 4-3. 9900 Bus Architecture

▶4

#### Hardware Design: Architecture and Interfacing Techniques

An overview is given here to establish design paths for microprocessor systems. Listed below are the processors in the 9900 family.

|              |            | ••••••••                                    |

|--------------|------------|---------------------------------------------|

| Device       | Technology | Description                                 |

| TMS 9900     | N-MOS      | 16-bit CPU 3 MHz                            |

| TMS 9900-40  | N-MOS      | 16-bit CPU 4 MHz                            |

| SBP 9900A    | $I^{2}L$   | 16-bit CPU $-55^{\circ}$ to $125^{\circ}$ C |

| TMS 9980A/81 | N-MOS      | 16-bit CPU 40-pin package                   |

| TMS 9985     | N-MOS      | 16-bit CPU 40-pin package                   |

| TMS 9940     | N-MOS      | 16-bit CPU with 2 k on-chip ROM             |

|              |            |                                             |

General purpose applications are designed around the TMS9900 device. The same is true for systems with severe environmental specs; however, a transition to the SBP9900A is made after the design is complete and the software completely debugged. The TMS980A/81 and the TMS9985 are used where the 40-pin package is advantageous and a slightly slower speed is acceptable. The TMS9940 is a single-chip microcomputer for small special purpose controllers.

At the end of this chapter and in the *Product Data* chapter there is detailed design data for application of the LSI (large scale integration) peripheral support circuits in the 9900 family which are available for use in 9900 microprocessor-based systems. But in order to read and understand the data presented in this chapter and in this book, an understanding of the basic fundamentals of microprocessors is needed.

#### ARCHITECTURE

#### BASIC MICROPROCESSOR CHIP

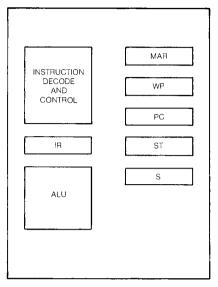

The 9900 is an advanced 16-bit LSI microprocessor with minicomputer-like architecture and instructions. It is easy to understand and easy to use. Consider first the microprocessor device itself (*Figure 4-4*). Operations are carried out with a set of dedicated registers, an ALU, and instruction handling circuits. As clock signals are applied, the processor will fetch an instruction word from a memory (external to the chip), will execute it, fetch another instruction, execute it and so on. In each case the instruction is saved in an instruction register (IR) on the chip. The decode circuit sets up the appropriate controls based on the content of the instruction register for a multi-step execution phase. A memory address register (MAR) is used to hold address information on the address bus. The ALU and the other registers perform their specified functions during the execute phase of the instruction cycle.

### MICROPROCESSOR REGISTERS

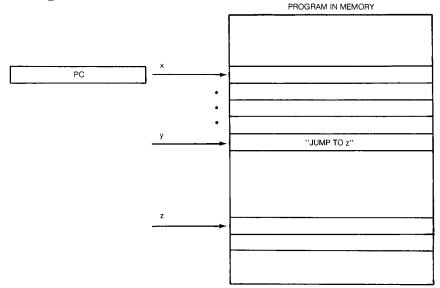

There are three registers on the 9900 chip which are the key architectural features of the microprocessor (*Figure 4-5*). They are the workspace pointer (WP), the program counter (PC), and the status register (ST).

## ARCHITECTURE

Hardware Design: Architecture and Interfacing Techniques

Workspace Pointer

The general purpose registers for the 9900 are implemented as blocks of memory called workspaces. A workspace consists of 16 contiguous words of memory, but are general registers to the user. The workspace pointer on the 9900 chip holds the address of the first word in the workspace. After initializing the content of the WP at the beginning of a program (or subprogram), the programmer may concentrate on writing a program using the registers to hold data words or to address data elsewhere in memory.

|   | WORKSPACE POINTER | ] |

|---|-------------------|---|

| - |                   | - |

|   | PROGRAM COUNTER   |   |

| _ |                   | - |

|   | STATUS REGISTER   |   |

|   |                   |   |

Figure 4-5. Three Important Registers

#### Program Counter

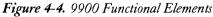

The program counter (PC) in the 9900 is used in the conventional way to locate the next instruction to be executed. As each instruction is executed, the program counter is incremented to the next consecutive word address. Because word addresses are even numbers in the 9900, the program counter is incremented by two in order to address sequential instructions. If the instruction to be executed occupies two or three memory words, the program counter will be incremented to generate sequential (even) addresses to access the required number of words. At the end of execution the PC is incremented to the next even address which is the location of the next instruction. If the instruction to be executed is a jump or branch instruction, the program counter is loaded with a new address and program execution continues starting with the instruction at that location in memory.

Figure 4-6 shows the program counter pointing to (addressing) instruction words in the program. Starting with location (x) the instructions are performed in sequence until a jump is encountered at (y). Processing resumes sequentially starting at location (z) which was the address specified by the jump instruction to be placed in the program counter.

Status Register

► The status register (ST) is the basis for decision making during program execution. Individual bits of the ST are set as flags as the result of instructions. They may thereafter be tested in the execution of conditional jump instructions. *Figure 4-7* shows the status register and its flag bits.

Figure 4-6. Program Counter Operation

ARCHITECTURE

Hardware Design: Architecture and Interfacing Techniques

| 0  | 1  | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9    | 10  | 11 | 12 | 13    | 14            | 15 |

|----|----|---|---|---|---|---|---|---|------|-----|----|----|-------|---------------|----|

| L> | A> | = | с | 0 | Ρ | х |   | F | ESER | VED |    | IN | TERRU | <br>РТ МА<br> | SK |

| Bit   | Function                       |

|-------|--------------------------------|

| 0     | Logical "Greater Than"         |

| 1     | Arithmetic "Greater Than"      |

| 2     | Equal                          |

| 3     | Carry                          |

| 4     | Overflow                       |

| 5     | Parity                         |

| 6     | XOP Instruction Being Executed |

| 12-15 | Interrupt Mask                 |

Figure 4-7. Status Register

The first three bits are set as a result of comparisons. Some instructions identify two operands (numbers) to be compared. If the first is greater than the second, the "greater than" bit should be set. In the 9900 there are two such conditions. First, the logical-greater-than bit considers 16-bit words as positive integers and the comparison is made accordingly. Second, the arithmetic-greater-than bit is set as the result of a comparison of two numbers which are considered in two's complement form. For example: consider the numbers A and B below as the numbers in the compare instruction C A, B:

A1000111011000101B0110101011001101

If they are 16-bit positive integers, it is clear from the most significant bits (MSB) that A is greater than B, and the logical-greater-than bit of the status register should be set to one. But as two's complement numbers, A is negative (MSB = 1) and B is positive. Therefore the arithmetic-greater-than bit must be made zero (A is not greater than B). Since the processor has no way of knowing how the designer has used the memory words for data (integers or two's complement), two status bits must be provided for decision making. The designer can select the appropriate conditional jump instruction (testing status bit 0 or 1) because he knows what the data format is.

Status bit 2, the equal bit, is set if the two words compared are equal.

In many instructions, only one number is involved or a new number is determined as the result of an arithmetic operation. For these instructions status bits 0, 1 and 2 are set as the result of comparisons against zero; that is, if the single number or answer obtained is greater than zero or equal to zero.

#### MEMORY-TO-MEMORY ARCHITECTURE

The 9900 family of processors employs memory-to-memory architecture in the execution of instructions. Memory-to-memory architecture is that computer organization and instruction set which enables direct modification of memory data via a single instruction. That is, a single instruction can fetch one or two operands from memory, perform an arithmetic or logical operation, and also store the result in memory. In doing so, some of the on-chip registers are used as temporary buffers in much the same manner as an accumulator is used in other systems. But instructions to load an accumulator and store the accumulator are rarely necessary in memory-to-memory architecture. A single 9900 instruction (arithmetic or logical) does the work of two or more instructions in other systems.

Figure 4-8 describes the technique used by the 9900 to locate words in memory as "registers" in the workspace. Additional information is included for reference purposes. Registers 1-15 may be used for indexing (see the description of this addressing mode in Chapter 5 and 6). Register 0 may be used for a shift count. Registers 11 and 13-15 are used for subroutine techniques. Register 12 is a base value for CRU instructions. These special uses of the workspace registers are stated here as an initial evaluation of the register set. Program control and CRU instructions make use of the contents of registers 11-15; therefore, programmers and systems designers must be aware that while use of these registers is not restricted to their special functions, they should be used with caution in performing other functions.

The use of these workspaces in an actual application is best described in the Software Design chapter. But the step-by-step execution of the instructions is of concern in hardware design because of the execution speed and the techniques for handling interrupts.

Instruction cycles in the 9900 require memory access not only for the instruction words but also for operand addresses and actual operands (or numbers to be operated upon.) A simple add instruction requires at least four memory cycles: one to fetch the instruction, two to access the two numbers to be added, and one to store the result. As will be explained in detail later in this chapter, the execution of an add instruction may require as many as eight memory cycles (because of the addressing mode.) The execution steps are not the same for all instructions. There is, in fact, substantial variation of execution steps within any one instruction due to addressing. Tables and charts are provided in this chapter to explain the execution time of each instruction.

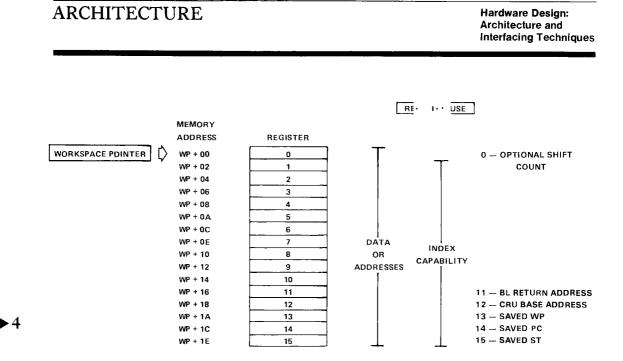

Figure 4-8. 9900 Workspace Registers

There is one additional concept regarding microprocessor and memory interfacing to be introduced at this time: it is the way in which data is stored in the memory. *Figure 4-9* shows the bit numbering for a general 16-bit data word or instruction. Instructions and 16-bit data words are always located at even addresses. Since the memory is byte addressable, even and odd bytes are the left and right half words in the 16-bit memory organization and have even or odd addresses respectively. Memories for the TMS9900 and SBP9900A contain 16 bits per word, while the other processors in the family use 8-bit memory structures. But all use the same addressing concept: a 16-bit address describing a 64k-byte address space.

Figure 4-9. Word and Byte Formats

#### CONTEXT SWITCHING

One of the more important advantages of the workspace architecture of the 9900 is the fact that "register save and restore" operations are greatly simplified. In any

interrupt processing system, provisions must be made to perform an orderly transition into a new program segment in response to an interrupt. In other microprocessor systems, the first few instructions of an interrupt service routine perform the steps of saving register contents in memory, and then loading new values into the registers.

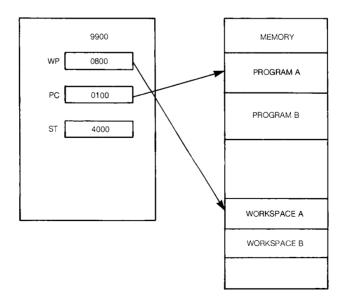

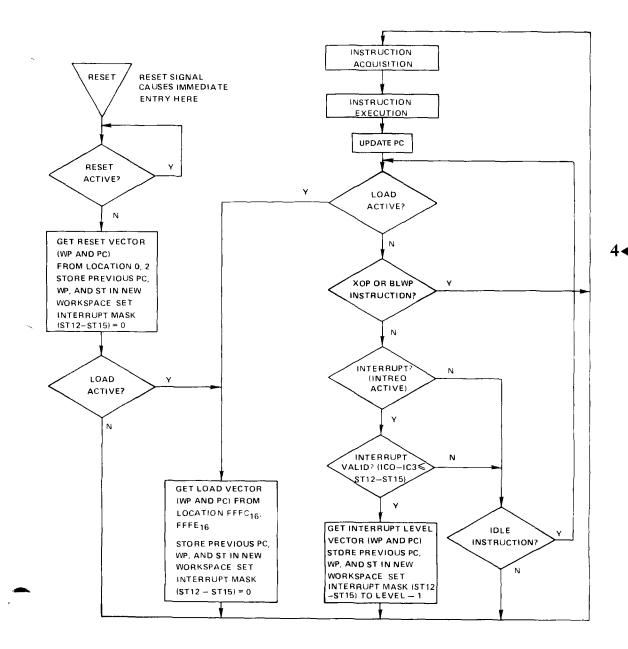

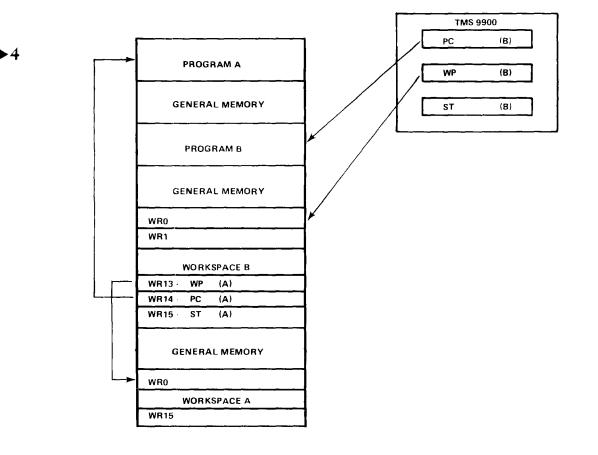

In the 9900, an interrupt cycle starts with a hardware operation to save the contents of the three key registers, the WP, PC and ST. In addition, the WP and PC must be loaded with new numbers. *Figures 4-10* and *4-11* show an example of the technique. Prior to the interrupt, the WP locates the workspace (pointing to 0800), the PC locates the current instruction (pointing to 0100), and the ST contains the status as a result of the execution of the current instruction (e.g., 4000). At the end of execution, the processor tests for an interrupt condition and finding it, performs a *context switch* as follows.

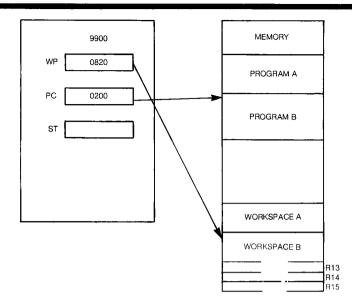

Step 1. The new WP value is fetched from the appropriate interrupt vector location in the first 32 words of memory. This identifies the location of the workspace assigned to the interrupt service routine.

Step 2. The current values of the WP, PC and ST registers are stored in the new workspace – ST in R15, PC in R14, WP in R13 in that order. After this, the new PC value is fetched from memory (the second location of the two-word interrupt vector) and loaded into the PC.

Figure 4-10. Before Context Switch

Figure 4-11. After Context Switch

*Step 3.* With the context switch completed, processing resumes with the first instruction in the interrupt service routine.

Processing continues in this mode until, at the end of the interrupt routine, an RTWP instruction is encountered. A "reverse" context switch now occurs to return to the previous program. Since R13, 14 and 15 contain the control register contents for the previous program, they are now transferred to the CPU which loads them into the WP, PC and ST. Processing resumes from the point at which the interrupt occurred.

The obvious advantage of context switching is the reduced register-save register-restore operations required by microprocessors in an interrupt environment. The context switch is also used as a subroutine technique. This is described in Chapters 5 and 6, but the important fact is that context switching is, to the designer, a single step, when in fact several steps are performed by the microprocessor.

#### MEMORY

The 9900 is easily interfaced to any of the standard types of semiconductor memory devices. Texas Instruments provides masked ROMs, field-programmable ROMs (PROMs), and erasable PROMs (EPROMs) for non-volatile program and data storage. RAMs are available in sizes from a 64 x 8 static RAM to the 64K dynamic RAMs for use as a temporary program and data storage. 9900-compatible memory devices are listed in Chapter 2.

#### MEMORY ORGANIZATION

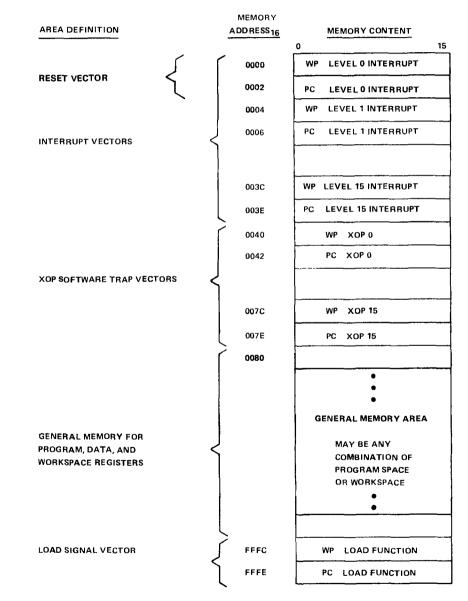

The 9900 instructions build a 16-bit address word which describes a  $64K \ge 8$  bit address space. A memory map for the 9900 is shown in *Figure 4-12*.

Figure 4-12. TMS 9900 Dedicated Memory Addresses

### RESET Vector

The first two memory words are reserved for storage of the RESET vector. The RESET vector is used to load the new WP and PC whenever the CPU RESET signal occurs. The first word contains the new WP, which is the starting address of the RESET workspace. The second word contains the new PC, which is the starting address of the RESET service routine.

### Interrupt Vectors

The next thirty memory words,  $0004_{16}$  through  $003E_{16}$  are reserved for storage of the interrupt transfer vectors for levels 1 through 15. Each interrupt level uses a word for the workspace pointer (WP) and a word for the starting address of the service routine (PC). If an interrupt level is not used within a system, then the corresponding two memory words can be used for program or data storage.

### Software Trap Vectors

The next thirty-two memory words, 0040<sub>16</sub> through 007E<sub>16</sub>, are used for extendedoperation software trap vectors. When the CPU executes one of the 16 extended operations (XOPs), the program traps through the corresponding vector. Two words are reserved for each trap vector, with one word for the WP and one word for the PC. If an XOP instruction is not used, the corresponding vector words can be used for program or data storage.

### LOAD Vector

The last two memory words  $FFFC_{16}$  and  $FFFE_{16}$  are reserved for the LOAD vector, with one word for the WP and one word for the PC. The LOAD vector is used whenever the CPU LOAD signal is active (low).

### Transfer Vector Storage

The transfer vectors can be stored either in ROM or RAM, but either the RESET or LOAD vector should be in non-volatile memory and should point to a program in non-volatile storage to ensure proper system start-up. The restart routine should initialize any vector which is in RAM. The program can then manipulate the RAM-based vectors to alter workspace assignments or service routine entry points, while ROM-based vectors are fixed and cannot be altered.

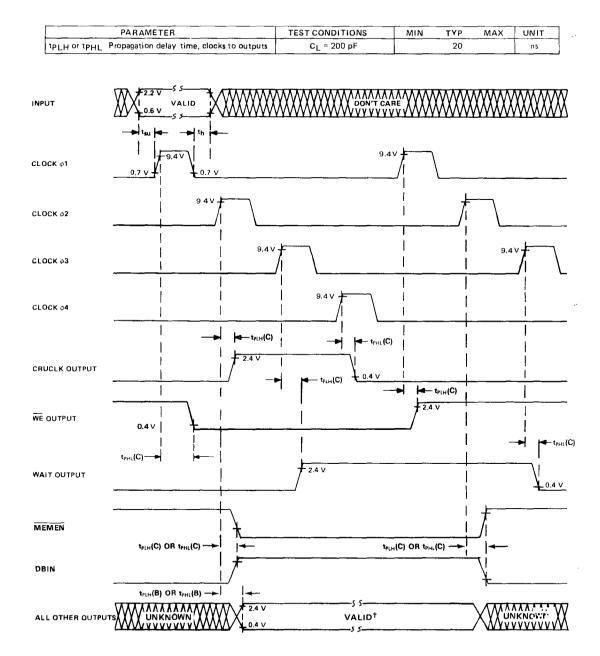

#### MEMORY CONTROL SIGNALS

The 9900 uses three signals to control the use of the data bus and address bus during memory read or write cycles. Memory enable  $\overline{(MEMEN)}$  is active low during all memory cycles.

Data bus in (DBIN) is active high during memory read cycles and indicates that the CPU has disabled the output data buffers.

Write enable  $\overline{(WE)}$  is active low during memory write cycles and has timing compatible with the read/write  $(R/\overline{W})$  control signal for many standard RAMs.

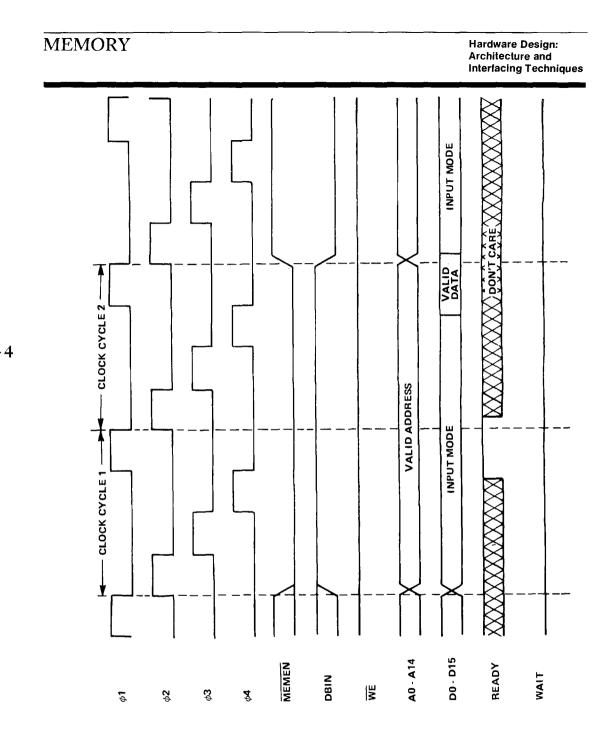

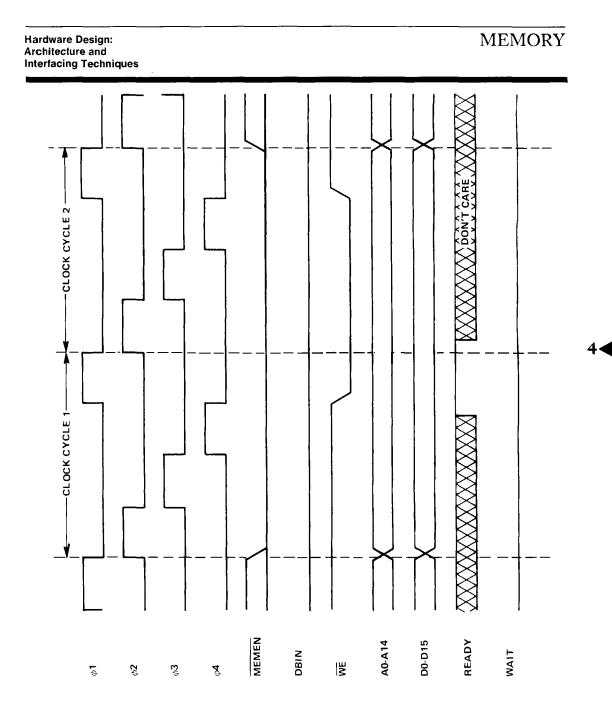

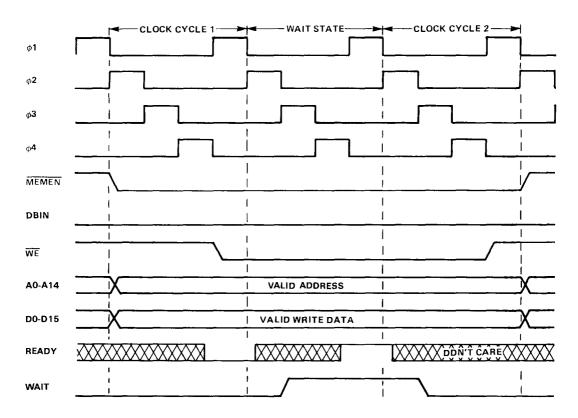

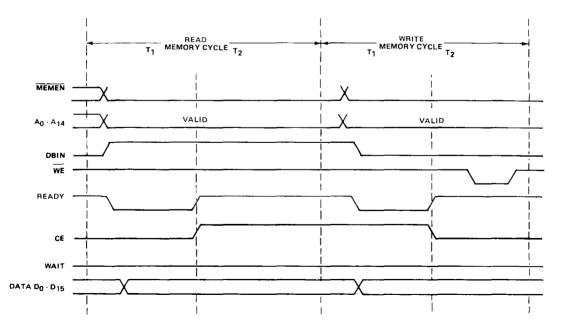

#### Memory Read Cycle

Figure 4-13 illustrates the timing for a memory read machine cycle with no wait states. At the beginning of the machine cycle,  $\overline{\text{MEMEN}}$  and DBIN become active and the valid address is output on A0-A14. D0-D15 output drivers are disabled to avoid conflicts with input data.  $\overline{\text{WE}}$  remains high for the entire machine cycle. The READY input is sampled on  $\phi 1$  of clock cycle 1, and must be high if no wait states are desired. Data is sampled on  $\phi 1$  of clock cycle 2, and set-up and hold timing requirements must be observed. A memory-read cycle is never followed by a memory-write cycle, and D0-D15 output drivers remain disabled for at least one additional clock cycle.

#### Memory Write Cycle

Figure 4-14 illustrates the timing for a memory write machine cycle with no wait states. <u>MEMEN</u> becomes active, and valid address and data are output at the beginning of the machine cycle. DBIN remains inactive for the complete cycle. WE goes low on  $\phi 1$  of clock cycle 1 and goes high on  $\phi 1$  of clock cycle 2, meeting the address and data set-up and hold timing requirements for the static RAMs listed in Chapter 2. For no wait states, READY must be high during  $\phi 1$  of clock cycle 1.

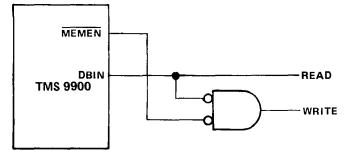

#### Read/Write Control with DBIN

In some memory systems, particularly with dynamic RAMs, it may be desirable to have READ and WRITE control signals active during the full memory cycle. *Figure 4-15* shows how the WRITE signal can be generated. Note that DBIN is high *only* for READ cycles; therefore, MEMEN can be NORed with DBIN to yield a WRITE signal which is high only during memory write operations. Slow Memory Control

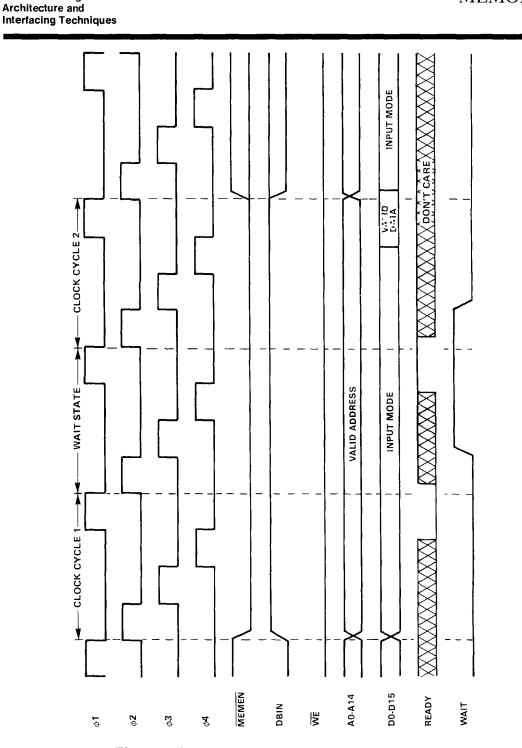

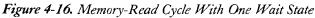

Although most memories operate with the 9900 at the full system speed, some memories cannot properly respond within the minimum access time determined by the system clock. The system clock could be slowed down in order to lengthen the access time but the system through-put would be adversely affected since non-memory and other memory reference cycles would be unnecessarily longer. The READY and WAIT signals are used instead to synchronize the CPU with slow memories. The timing for memory-read and memory-write cycles with wait states is shown in *Figures 4-16* and *4-17*.

Figure 4-13. Memory-Read Cycle Timing

Figure 4-14. Memory-Write Cycle Timing

Figure 4-15. Read / Write Control Using MEMEN and DBIN

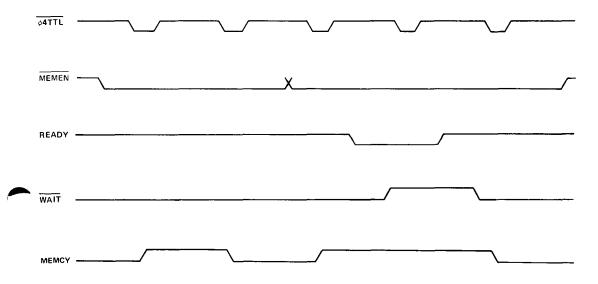

The READY input is tested on  $\phi 1$  of clock cycle 1 of memory-read and memory-write cycles. If READY = 1, no wait states are used and the data transfer is completed on the next clock cycle. If READY = 0, the processor enters the wait state on the next clock cycle and all memory control, address, and data signals maintain their current levels. The WAIT output goes high on  $\phi 3$  to indicate that a wait state has been entered. While in the wait state, the processor continues to sample READY on  $\phi 1$ , and remains in the wait state until READY = 1. When READY = 1 the processor progresses to clock cycle 2 and the data transfer is completed. WAIT goes low on  $\phi 3$ . It is important to note that READY is only tested during  $\phi 1$ , of clock cycle 1 of memory-read and memory-write cycles and wait states, and the specified set-up and hold timing requirements must be met; at any other time the READY input may assume any value. The effect of inserting wait states into memory access cycles is to extend the minimum allowable access time by one clock period for each wait state.

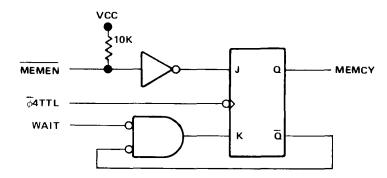

#### Wait State Control

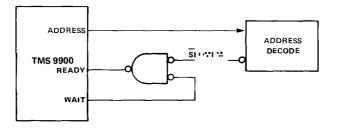

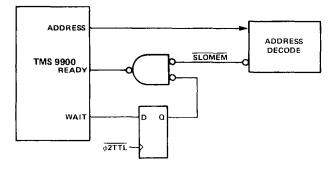

Figure 4-18 illustrates the connection of the WAIT output to the READY input to generate one wait state for a selected memory segment. The address decode circuity generates an active low signal  $\overline{(\text{SLOMEM} = 0)}$  whenever the slow memory is addressed. For example, if memory addresses  $8000_{16} - \text{FFFE}_{16}$  select slow memory,  $\overline{\text{SLOMEM}} = A0$ . If one wait state is required for all memory, WAIT may be connected directly to READY, causing one wait state to be generated on each memory-read or memory-write machine cycle. Referring again to Figures 4-16 and 4-17 note that the WAIT output satisfies all of the timing requirements for the READY input for a single wait state. The address decode signal is active only when a particular set of memory locations has been addressed. Figure 4-19 illustrates the generation of two wait states for selected memory by simply delaying propagation of the WAIT output to the READY input to the READY input one clock cycle with a D-type flip-flop. The rising edge of  $\phi 2$ TTL is assumed to be coincident with the falling edge of the  $\phi 2$  clock input to the TMS 9900.

Hardware Design:

4

MEMORY

## MEMORY

Figure 4-17. Memory-Write Cycle With One Wait State

Figure 4-18. Single Wait State for Slow Memory

Figure 4-19. Double Wait States for Slow Memory

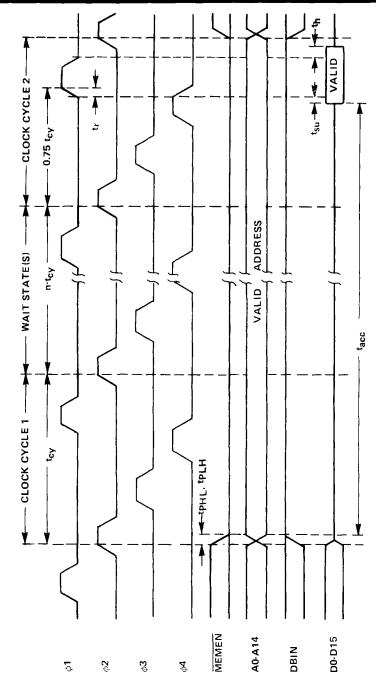

#### Memory Access Time Calculation

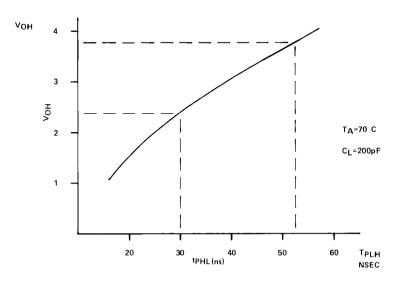

Maximum allowable memory access time for the TMS 9900 can be determined with the aid of *Figure 4-20*. Memory control and address signals are output on  $\phi 2$  of clock cycle 1, and are stable 20 ns (t<sub>PLH</sub>, t<sub>PHL</sub>) afterwards. Data from memory must be valid 40 ns (t<sub>su</sub>) before the leading edge of  $\phi 1$  during clock cycle 2. Therefore, memory access time may be expressed by the equation:

$$t_{acc} \le (1.75 + n) t_{cy} - t_{PLH} - t_r - t_{su}$$

where n equals the number of wait states in the memory-read cycle. Assigning worst-case specified values for  $t_{PLH}$  (20ns),  $t_r$  (12ns), and  $t_{su}$  (40 ns), and assuming 3 MHz operation:

$$t_{acc} \le \frac{(1.75 + n)}{0.003} - 72 \text{ ns}$$

Access time is further reduced by address decoding, control signal gating, and address and data bus buffering, when used. Thus, for a known access time for a given device, the number of required wait states can be determined.

For example, a TMS 4042-2 RAM has a 450 nanosecond access time and does not require any wait states. A TMS 4042 has a 1000 nanosecond access time and requires two wait states. Propagation delays caused by address or data buffers should be added to the nominal device access time in order to determine the effective access time.

## MEMORY

▶4

Figure 4-20. Memory Access Timing Calculation

#### STATIC MEMORY

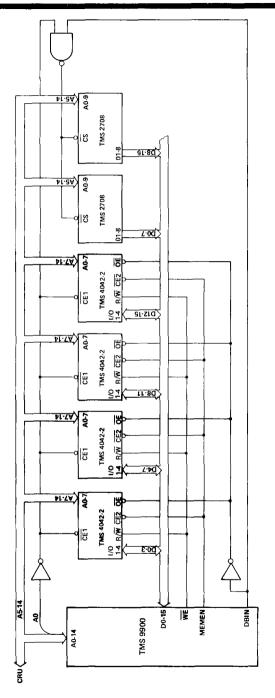

Static RAMs and PROMs are easily interfaced to the 9900. A 9900 memory system using the TMS 4042-2 256 X 4 static RAM and the TMS 2708 1K X 8 EPROM is shown in *Figure 4-21*.

#### Address

The most-significant address bit, A0, is used to select either the EPROMs or the RAMs during memory cycles. When A0 is low, the EPROMs are selected, and when A0 is high, the RAMs are selected. Address lines A1 through A4 are not used since the full address space of the TMS 9900 is not required in the example. The lower address bits select internal RAM or EPROM cells. Other memory systems can fully decode the address word for maximum memory expansion.

#### Control Signals

Since DBIN is also used to select the EPROMs during memory-write cycles, the EPROMs cannot inadvertently be selected and placed into output mode while the CPU is also in the output mode on the data bus.  $\overline{\text{MEMEN}}$  is used to select the RAMs during either read or write cycles, and  $\overline{\text{WE}}$  is used to select the read/write mode. DBIN is also used to control the RAM output bus drivers.

The 9900 outputs  $\overline{\text{WE}}$  three clock phases after the address, data, and  $\overline{\text{MEMEN}}$  are output. As a result, the address, data, and enable-hold times are easily met.  $\overline{\text{WE}}$  is enabled for one clock cycle and satisfies the minimum write pulse width requirement of 300 nanoseconds. Finally,  $\overline{\text{WE}}$  is disabled one clock phase before the address, data, and other control signals and meets the TMS 4042-2 50-nanosecond minimum data and address hold time.

#### Loading

The loads on the CPU and memory outputs are well below the maximum rated loads. As a result no buffering is required for the memory system in *Figure 4-21*. The TMS 4042-2 and the TMS 2708 access times are low enough to eliminate the need for wait states, and the CPU READY input is connected to  $V_{\rm cc}$ .

The minimum high-level input voltage of the TMS 2708 is 3 volts while the maximum high-output voltage for the TMS 9900 is 2.4 volts at the maximum specified loading. For the system in *Figure 4-21*, the loads on the CPU and memory outputs are well below the maximum rated load. At this loading, the TMS9900 output voltage exceeds 3 volts, so pull-up resisters are not needed.

There are many other Texas Instruments static memories compatible with the TMS 9900. Most memory devices do not require wait states when used with the TMS 9900 at 3 MHz.

### MEMORY

▶4

Figure 4-21. TMS 9900 Static Memory System

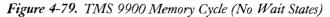

#### DYNAMIC MEMORY

Memory applications requiring large bit storage can use 4K, 16K or 64K dynamic memories for low cost, low power consumption, and high bit density. TMS 9900 systems requiring 4K words or more of RAM, can economically use the 4096-bit TMS 4051, the 16,384bit TMS 4116, or any of the other dynamic RAMs covered in Chapter 2.

#### Refresh

The dynamic RAMs must be refreshed periodically to avoid the loss of stored data. The RAM data cells are organized into a matrix of rows and columns with on-chip gating to select the addressed bit. Refresh of the 4K RAM cell matrix is accomplished by performing a memory cycle of each of the 64 row addresses every 2 milliseconds or less. The 16K RAM has 128 row addresses. Performing a memory cycle at any cell on a row refreshes all cells in the row, thus allowing the use of arbitrary column address during refresh.

#### Refresh Modes

There are several dynamic memory refresh techniques which can be used for a TMS 9900 system. If the system periodically accesses at least one cell of each row every 2 milliseconds, then no additional refresh circuitry is required. A CRT controller which periodically refreshes the display, illustrates this concept.

Refresh control logic is included wherever the system cannot otherwise ensure that all rows are refreshed every 2 milliseconds. The dynamic memory in such TMS 9900 systems can be refreshed in the block, cycle stealing, or transparent mode.

#### Block Refresh.

The block mode of refresh halts the CPU every 2 milliseconds and sequentially refreshes each of the rows. The block technique halts execution for a 128 (4K) or 256 (16K) clock cycle periods every 2 milliseconds. Some TMS 9900 systems cannot use this technique because of the possibility of slow response to priority interrupts or because of the effect of the delay during critical timing or I/O routines.

### Cycle Stealing.

The cycle stealing mode of refresh "steals" a cycle from the system periodically to refresh one row. The refresh interval is determined by the maximum refresh time and the number of rows to be refreshed. The 4K dynamic RAMs have 64 rows to be refreshed every 2 milliseconds and thus require a maximum cycle stealing interval of 31.2 microseconds.

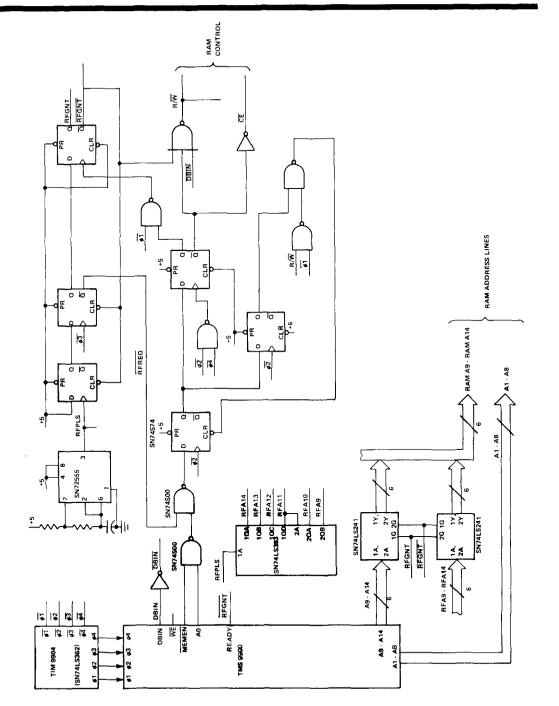

A cycle stealing refresh controller for the TMS 4051 4K dynamic RAM is shown in *Figure 4-22.* The refresh timer generates the refresh signal (RFPLS) every 30 microseconds. The refresh request signal (RFREQ) is true until the refresh cycle is completed. The refresh grant signal (RFGNT) goes high during the next CPU clock cycle in which the CPU is not accessing the dynamic memory. The refresh memory cycle takes two clock cycles to complete after RFGNT is true. During the second clock cycle, however, the CPU can attempt to access the dynamic memory since the CPU is not synchronized to the refresh controller. If the CPU does access memory during the last clock cycle of the refresh memory cycle, the refresh controller makes the memory not-ready for the remainder of the refresh memory row address during the refresh memory cycle is the output of a modulo-64 counter. The counter is incremented each refresh cycle in order to refresh the rows sequentially.

The dynamic memory timing controller generates the proper chip enable timing for both CPU and refresh initiated memory cycles. The timing controller can be easily modified to operate with other dynamic RAMs.

Since the TMS 9900 performs no more than three consecutive memory cycles, the refresh request will be granted in a maximum of three memory cycles. Some systems may have block DMA, which uses HOLD. RFREQ can be used in such systems to disable HOLDA temporarily in order to perform a refresh memory cycle if the DMA block transfer is relatively long (greater than 30 microseconds). The cycle stealing mode "steals" clock cycles only when the CPU attempts to access the dynamic memory during the last half of the refresh cycle. Even if this interference occurs during each refresh cycle, a maximum of 64 clock cycles are "stolen" for refresh every 2 milliseconds.

#### Transparent Refresh.

The transparent refresh mode eliminates this interference by synchronizing the refresh cycle to the CPU memory cycle. The rising edge of  $\overline{\text{MEMEN}}$  marks the end of a memory cycle immediately preceding a non-memory cycle. The  $\overline{\text{MEMEN}}$  rising edge can initiate a refresh cycle with no interference with memory cycles. The refresh requirement does not interfere with the system throughput since only non-memory cycles are used for the refresh cycles. The worst-case TMS 9900 instruction execution sequence (all divides) will guarantee the complete refresh of a 4K or 16K dynamic RAM within 2 milliseconds.

#### Hardware Design: Architecture and Interfacing Techniques

Figure 4-22. Cycle-Stealing Dynamic RAM Refresh for TMS 4051

While the transparent refresh mode eliminates refresh-related system performance degradation, the system power consumption can be higher since the RAMs are refreshed more often than required. As many as one-half of the CPU machine cycles can be refresh cycles, resulting in multiple refresh cycles for each row during the refresh interval. This situation can be corrected by adding a timer to determine the start of the refresh interval and an overflow detector for the refresh row counter. When every row has been refreshed during an interval, the refresh circuit is disabled until the beginning of the next interval. Since each row is refreshed only once, the system power consumption is reduced to a minimum.

Direct memory access using  $\overline{\text{HOLD}}$  should guarantee that sufficient non-memory cycles are available for refresh during large block transfers. An additional refresh timer can be used to block HOLDA in order to provide periodic refresh cycles.

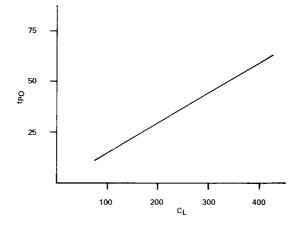

#### BUFFERED MEMORY

The TMS 9900 outputs can drive approximately two standard TTL inputs and 200 picofarads. Higher capacitive loads may be driven, but with increased rise and fall times. Many small memory systems can thus be directly connected to the CPU without buffer circuits. Larger memory systems, however, may require external bipolar buffers to drive the address or data buses because of increased loading. Texas Instruments manufactures a number of buffer circuits compatible with the TMS 9900. The SN74LS241 noninverting-octal buffer with three-state outputs is an example of a buffer circuit.

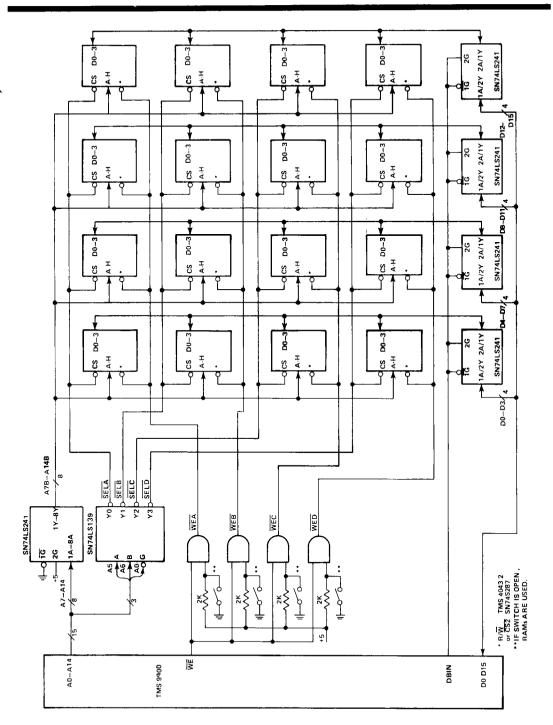

A TMS 9900 memory system with address and data bus buffering is shown in *Figure 4-23*. The system consists of sets of four 256 X 4 memory devices in parallel to provide the 16-bit data word. The four sets of four devices provide a total of 1024 words of memory. The memory devices can be the TMS 4042-2 NMOS static RAM.

The SN74S412 octal buffer/latch is designed to provide a minimum high-level output voltage of 3.65 V. Buffered TMS 9900 memory systems containing the TMS 4700 ROM or the TMS 2708 EPROM, for example, require input voltages in excess of the output voltages of many buffer circuits. The SN74S412 can be used to buffer the memories without the pull-up resistors needed for buffers.

#### MEMORY PARITY

Parity or other error detection/correction schemes are often used to minimize the effects of memory errors. Error detection schemes such as parity are used to indicate the presence of bad data, while error correction schemes correct single or multiple errors.

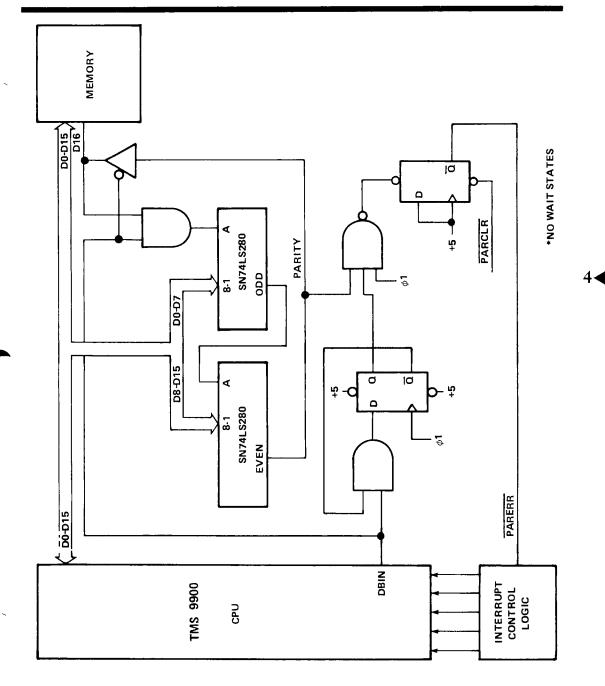

Figure 4-23. Buffered Memory with Mixed PROM/ROM

The SN74LS280 parity generator/checker can be used to implement memory parity in a TMS 9900 system. The system in *Figure 4-24* uses two SN74LS280 circuits to generate and to check the odd-memory parity. During memory write cycles, the generated parity bit is output to bit D16 of the memory. During memory read cycles, the parity is checked and an interrupt, PARERR, is generated if the parity is even.

It should be noted that the faulty memory word will have already been used by the CPU as an op code, address, or data before the interrupt is generated. This can cause trouble in determining the exact location of the error. For example, an error in bit 8 of the CLR op code will cause the CPU to branch unconditionally. When the interrupt is serviced, there would then be no linkage to the part of the program at which the error occurred. A diagnostic routine can often isolate such errors by scanning the memory and checking parity under program control. Such a parity error in the diagnostic itself can be extremely difficult to isolate.

An external address latch clocked at IAQ can be used to retain program linkage under the above circumstances. When the parity error is detected, the address latch is frozen, thus pointing to the address of the instruction during which the parity error occurred.

#### Memory Layout

It is generally advantageous to lay out memory devices as arrays in the system. The advantages are twofold. First, positioning the devices in an orderly fashion simplifies identification of a particular memory element when troubleshooting. Second, and most important, layout of memory arrays simplifies layout, shortens interconnections, and generally allows a more compact and efficient utilization of board space. Crosstalk between adjacent lines in memory arrays is minimized by running address and data lines parallel to each other, and by running chip enable signals perpendicular to the address lines.

Memory devices, particularly dynamic RAMs generally require substantially greater supply currents when addressed than otherwise. It is therefore important that all power and ground paths be as wide as possible to memory arrays. Furthermore, in order to avoid spikes in supply voltages, it is advisable to decouple supply voltages with capacitors as close as possible to the pins of the memory devices. As an example, a system containing a 4K x 16-bit array of TMS 4051s should contain one 15  $\mu$ F and one 0.05  $\mu$ F capacitor for each set of four memory devices; with the large capacitors decoupling V<sub>DD</sub>, and the small capacitors decoupling V<sub>BB</sub>.

Hardware Design: Architecture and Interfacing Techniques

Figure 4-24. Memory Parity Generator Checker

Execution time for an instruction is a function of the clock frequency, the number of clock cycles, the number of memory accesses and the number of wait states if required for slower memories. The following tables list the number of clock cycles required to execute each instruction if no wait states are required. The number of memory accesses is also given so that the extra clock cycles can be calculated for the number of wait states required. A wait state is entered when the ready signal from the memory does not go high within one clock period after initiation of a memory cycle. For example: The clock frequency for the TMS 9900 is 3 MHz. From the calculation of maximum access time for no wait states, the memory access time must be less than 512 ns. One wait state (of 333 ns duration) will be required for memories with access times between 512 ns and 845 ns, two wait states will be required if the access time is between 845 ns and 1.178  $\mu$  sec, and so on.

#### Timing

From *Figure 4-25*, the first execution time table, an add instruction (A) using direct register addressing for both operands requires 14 clock cycles if there are no wait states required. For other addressing modes, the number of clock cycles increases to a maximum of 30. If the memory requires one wait state per access, an additional four clock periods will be required since there are four memory cycles in the execution of an add instruction. For the TMS 9900 running at 3 MHz, 14 clock periods will take 4.667 microseconds; 30 clock periods will take 10.0 microseconds. The number of memory cycles is from 4 up to 8 depending upon addressing mode (3 to 7 for compare, C). Use the tables in the following manner. Assuming one wait state, a clock frequency of 3 MHz, and an instruction with complex addressing, the tables can be used to determine the execution time for the instruction

A \*R1, @ LIST

is 26 clock cycles for fetch and execution and 6 clock cycles for wait states, or 32 x .333 microseconds which is 10.667 microseconds.

Figures 4-26, 27 and 28 give the rest of the execution time data, always by number of clock cycles (assuming no wait states) and memory cycles. Execution times for instructions which do not use the five general addressing modes may be found in Chapter 8 in the *CPU* section.

|                                      | Destination                          |                            |                                  | Source Ac                  | ddress                     |                            |  |

|--------------------------------------|--------------------------------------|----------------------------|----------------------------------|----------------------------|----------------------------|----------------------------|--|

|                                      | Address                              | R                          | *R                               | *R +                       | @LIST                      | @TABLE (R)                 |  |

| Clock<br>Cycles                      | R<br>*R<br>@LIST<br>@TABLE(R)        | 14<br>18<br>22<br>22<br>22 | 18<br>22<br>26<br>26<br>26<br>26 | 22<br>26<br>30<br>30<br>30 | 22<br>26<br>30<br>30<br>30 | 22<br>26<br>30<br>30<br>30 |  |

| Memory<br>Cycles                     | R<br>*R<br>@LIST<br>@TABLE (R)       | 4<br>5<br>6<br>5<br>6      | 5<br>6<br>7<br>6<br>7            | 6<br>7<br>8<br>7<br>8      | 5<br>6<br>7<br>6<br>7      | 6<br>7<br>8<br>7<br>8      |  |

| †Memory<br>Cycles<br>for C<br>instr. | R<br>*R<br>*R+<br>@LIST<br>@TABLE(R) | 3<br>4<br>5<br>4<br>5      | 4<br>5<br>6<br>5<br>5            | 5<br>6<br>7<br>6<br>6      | 4<br>5<br>6<br>5<br>7      | 5<br>6<br>7<br>6<br>6      |  |

#### INSTRUCTIONS A, C<sup>†</sup>, S, SOC, SZC, MOV

#### Figure 4-25.

#### INSTRUCTIONS: AB, CB<sup>††</sup>, SB. SOCB, SZCB, MOVB

|                                        | Destination                    |                            |                                   | Source Ad                  | ddress                           |                                  |

|----------------------------------------|--------------------------------|----------------------------|-----------------------------------|----------------------------|----------------------------------|----------------------------------|

|                                        | Address                        | R                          | *R                                | *R+                        | @LIST                            | @TABLE (R)                       |

| Clock<br>Cycles                        | R<br>*R<br>@LIST<br>@TABLE (R) | 14<br>18<br>20<br>22<br>22 | 18<br>22<br>24<br>26<br><b>26</b> | 20<br>24<br>26<br>28<br>28 | 22<br>26<br>28<br>28<br>28<br>28 | 22<br>26<br>28<br>28<br>28<br>28 |

| Memory<br>Cycles                       | R<br>*R<br>@LIST<br>@TABLE (R) | 4<br>5<br>6<br>5<br>6      | 5<br>6<br>7<br>6<br>7             | 6<br>7<br>8<br>7<br>8      | 5<br>6<br>7<br>6<br><b>7</b>     | 6<br>7<br>8<br>7<br>8            |

| ††Memory<br>Cycles<br>for CB<br>instr. | R<br>*R<br>@LIST<br>@TABLE (R) | 3<br>4<br>5<br>4<br>5      | 4<br>5<br>6<br>5<br>6             | 5<br>6<br>7<br>6<br>7      | 4<br>5<br>6<br>5<br>6            | 5<br>6<br>7<br>6<br>7            |

#### Hardware Design: Architecture and Interfacing Techniques

| INSTRUCTIONS | LDCR, STCR |

|--------------|------------|

|--------------|------------|

| LDCR             | Addressing                     | Bit Count, C   |                                                       |                |                |                |                |                |                            |                |                |                |                |                |                |                |                |  |

|------------------|--------------------------------|----------------|-------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

|                  | Mode                           | 1              | 2                                                     | 3              | 4              | 5              | 6              | 7              | 8                          | 9              | 10             | 11             | 12             | 13             | 14             | 15             | 0              |  |

| Clock<br>Cycles  | R<br>*R<br>@LIST<br>@TABLE (R) | 26<br>28<br>30 | 28<br>30<br>32                                        | 30<br>32<br>34 | 32<br>34<br>36 | 34<br>36<br>38 | 36<br>38<br>40 | 38<br>40<br>42 | 36<br>40<br>42<br>44<br>44 | 42<br>46<br>46 | 44<br>48<br>48 | 46<br>50<br>50 | 48<br>52<br>52 | 50<br>54<br>54 | 52<br>56<br>56 | 54<br>58<br>58 | 56<br>60<br>60 |  |

| Memory<br>Cycles | R<br>*R<br>@LIST<br>@TABLE (R) |                | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |                |                |                |                |                |                            |                |                |                |                |                |                |                |                |  |

| STCR             | Addressing                     | Bit Count, C   |                |                |                            |                |                |                |                            |                |                |                |                |                |                |                |                |

|------------------|--------------------------------|----------------|----------------|----------------|----------------------------|----------------|----------------|----------------|----------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                  | Mode                           | 1              | 2              | 3              | 4                          | 5              | 6              | 7              | 8                          | 9              | 10             | 11             | 12             | 13             | 14             | 15             | 0              |

| Clock<br>Cycles  | R<br>*R<br>@LIST<br>@TABLE (R) | 46<br>48<br>50 | 46<br>48<br>50 | 46<br>48<br>50 | 46<br>48<br>50             | 46<br>48<br>50 | 46<br>48<br>50 | 46<br>48<br>50 | 44<br>48<br>50<br>52<br>52 | 62<br>66<br>66 | 64<br>68<br>68 |

| Memory<br>Cycles |                                |                |                | Ę              | 4<br>5<br>5<br>5<br>5<br>5 |                |                |                |                            |                |                | Į              | 4 5 6 5 6      |                |                |                |                |

Figure 4-27.

-4

#### Hardware Design: Architecture and Interfacing Techniques

## INSTRUCTION EXECUTION

|             |    |    | CI   | Memory Cycles |            |   |    |     |       |            |  |  |

|-------------|----|----|------|---------------|------------|---|----|-----|-------|------------|--|--|

| Instruction | R  | *R | *R + | @LIST,        | @TABLE (R) | R | *R | *R+ | @LIST | @TABLE (R) |  |  |

| ABS MSB = 0 | 12 | 16 | 20   | 20            | 20         | 2 | 3  | 4   | 3     | 4          |  |  |

| MSB = 1     | 14 | 18 | 22   | 22            | 22         | 3 | 4  | 5   | 4     | 5          |  |  |

| В           | 8  | 12 | 16   | 16            | 16         | 2 | 3  | 4   | 3     | 4          |  |  |

| BL          | 12 | 16 | 20   | 20            | 20         | 3 | 4  | 5   | 4     | 5          |  |  |

| BLWP        | 26 | 30 | 34   | 34            | 34         | 6 | 7  | 8   | 7     | 8          |  |  |

| CLR         | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| DEC         | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| DECT        | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| INC         | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| INCT        | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| INV         | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| NEG         | 12 | 16 | 20   | 20            | 20         | 3 | 4  | 5   | 4     | 5          |  |  |

| SETO        | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| SWPB        | 10 | 14 | 18   | 18            | 18         | 3 | 4  | 5   | 4     | 5          |  |  |

| XOP         | 36 | 40 | 44   | 44            | 44         | 8 | 9  | 8   | 9     | 8          |  |  |

| XOR         | 14 | 18 | 22   | 22            | 22         | 4 | 5  | 6   | 5     | 6          |  |  |

#### Figure 4-28.

#### Cyclic Operation

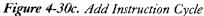

An example of a machine cycle sequence is illustrated in *Figure 4-29*. For an add instruction the machine cycles alternate between memory cycles and ALU cycles. The first cycle is always a memory read cycle to fetch the instruction and the second is always an ALU cycle to decode the instruction. Each machine cycle requires two clock cycles, thus the 7 machine cycles shown for the add instruction require 14 clock cycles.

#### A R1, R2

| 1 | Memory Read  | Instruction Fetch       |

|---|--------------|-------------------------|

| 2 | ALU          | Decode Opcode           |

| 3 | Memory Read  | Fetch (WR1)             |

| 4 | ALU          | Set Up                  |

| 5 | Memory Read  | Fetch (WR2)             |

| 6 | ALU          | Addition                |

| 7 | Memory Write | Store Result in WR2 and |

|   |              | Increment PC            |

#### Figure 4-29. Machine Cycles for an Add Instruction

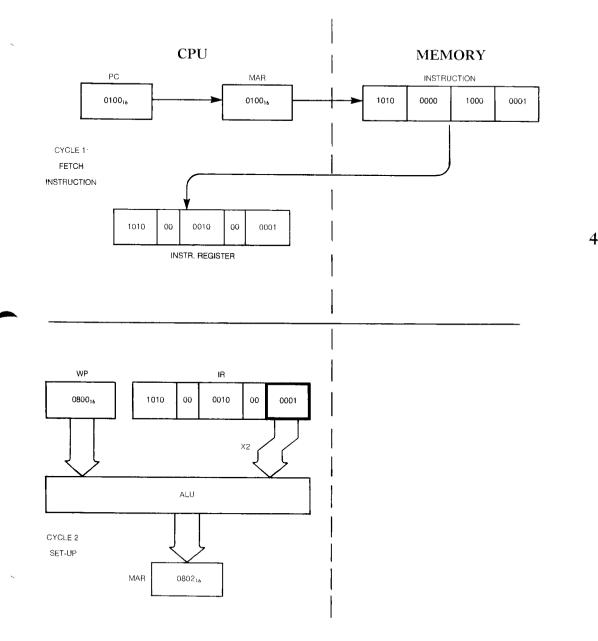

The 9900 performs its functions under control of a 4-phase clock and, fundamentally, performs instruction fetch and execution cycles. *Figure 4-30* illustrates the step-by-step procedure the 9900 uses to execute an add instruction. From previous cycles, the workspace pointer has been loaded with the number 0800, and the program counter contains the number 0100.

Step 1. The first step in any instruction cycle is to fetch the instruction. This is accomplished by gating the content of the program counter into the memory address register. The output of the memory address register is the address bus which is connected to the memory. In this case, word number 0100 is read from the memory and placed in the instruction register on the 9900 chip. From this point, the ones and zeros of the instruction register control the sequence of microcode stored in the microcontrol read only memory on the 9900 chip. These microsteps become the execution phase of the instruction.

Step 2. At this point, the microcontrol shifts to the execution of an add instruction; the first operand must be obtained from memory. In order to do this, the workspace pointer and a portion of the instruction word (the source operand register number) are added together via the ALU and placed in the memory address register.

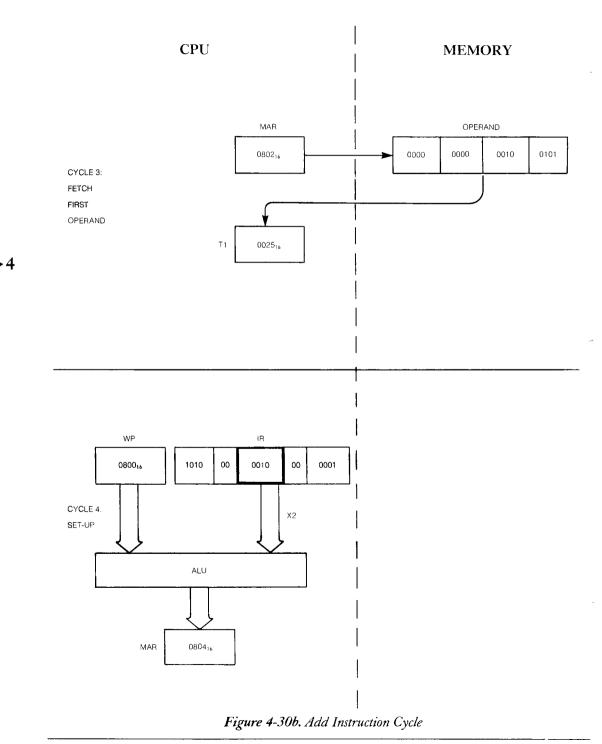

Step 3. The address 0802 is the result (in this example), and being supplied to the memory produces on the data bus the content of memory word 0802 which is the binary equivalent of 25. This number must be stored in a temporary register on the 9900 chip, in this case the T1 register.

Step 4. Now a second operand must be fetched. Again the workspace pointer is added to the content of that portion of the instruction word which is the destination register identifier. The sum of these two is 0804 for register two, and this number is placed in memory address register and goes out on the address bus.

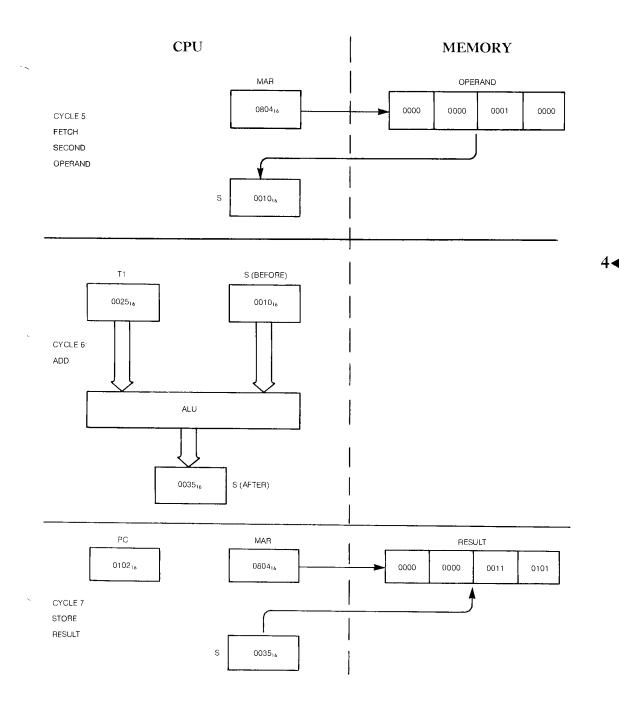

Step 5. Memory word 0804 is read and the number 10 is brought into the 9900 chip. The register which stores the second operand is called the source data register or S register.

Step 6. At this point the two operands have been loaded into registers on the 9900 chip and may be added by the ALU to produce the result. Register T1 containing 25 is added to the register S which contains 10 and the sum, 35, replaces the 10 in the S register and is placed on the data bus via the S register.

Step 7. The address bus still contains the number 0804 which was the address of the second operand and is the location in memory where the result is to be stored. So at this point in the cycle, a memory write cycle is initiated and the binary equivalent of 35 is stored in memory location 0804. At the conclusion of this memory cycle the program counter is incremented by two to point to the next sequential memory word, which is the instruction to be executed next.

Figure 4-30a. Add Instruction Cycle

# INSTRUCTION EXECUTION

Hardware Design: Architecture and Interfacing Techniques

# INSTRUCTION EXECUTION

After all steps have been done, the processor checks to see if there is any pending interrupt operations to be performed and, if not, fetches the next instruction and the cycle continues. In the event that an interrupt signal were present, the processor would proceed to the appropriate interrupt service routine and continue execution from that point. Interrupts are described in detail in a special section of this chapter.

Each operation performed by the 9900 consists of a sequence of machine cycles. In each machine cycle the processor performs a data transfer with memory or with CRU and/or an arithmetic or logical operation internally with the ALU. A detailed discussion of the machine cycles for each instruction is included at the end of the chapter.

Each ALU machine cycle is two clock cycles long. In an ALU cycle no external data transfer occurs, but the ALU performs an arithmetic or logical operation on two operands contained internally. The function of the memory read cycle is to transfer a word of data contained in the memory to the processor. An ALU operation may be performed during the memory read cycle. Memory read cycles are a minimum of two clock cycles long. The memory write cycle is identical to the memory read cycle except that data is written rather than read from memory.

Each CRU output machine cycle is two clock cycles long. In addition to outputting a bit of CRU data, an ALU operation may also be performed internally. The CRU input cycle is identical to the CRU output cycle except that one bit of data is input rather than output.

## Machine Cycle Limits

Table 4-1 lists information which will be useful for system design. The maximum number of consecutive memory-read cycles is used to calculate the maximum latency for the TMS 9900 to enter the hold state since the hold state is only entered from ALU, CRU input, or CRU output machine cycles. The minimum frequency of consecutive memory/ non-memory cycle sequences occurs when the DIV instruction is executed. This number is used to ensure that the refresh rate meets specifications when the transparent-refresh mode described in the memory section is used since memory is refreshed in this mode each time an ALU or CRU cycle follows a memory cycle. *Figure 4-31* shows the logic to generate a pulse for each memory access cycle. Consecutive cycle timing is shown in *Figure 4-32*.

# INSTRUCTION EXECUTION

# Table 4-1. Machine Cycle Limits

|                                 | MINIMUM       | MAXIMUM |

|---------------------------------|---------------|---------|

| Consecutive Memory Read Cycles  | 1             | 3       |

| Consecutive Memory Write Cycles | 1             | 1       |

| Consecutive ALU Cycles          | 1             | 51      |

| Consecutive CRU Cycles          | 1             | 16      |

| Frequency of Consecutive        | 5 pairs       |         |

| memory/non-memory cycle         | (64 machine   |         |

| pairs (used for transparent     | cycles during |         |

| refresh)                        | DIV.)         |         |

Figure 4-31. Memory Cycle Pulse Generation

Figure 4-32. Memory Cycle Pulse Timing

# INPUT/OUTPUT

The 9900 has three I/O modes: direct memory access (DMA), memory mapped, and communications register unit (CRU). This multi-mode capability enables the designer to optimize a 9900 I/O system to match a specific application. One or all modes can be used, as shown in *Figure 4-33*.

DIRECT MEMORY ACCESS - DMA

Figure 4-33. 9900 I/O Capability

### DIRECT MEMORY ACCESS

DMA is used for high-speed block data transfer when CPU interaction is undesirable or not required. The DMA control circuitry can be relatively complex and expensive when compared to other I/O methods. However, a special interface device, the TMS 9911, is available for DMA control. This device is described in Chapter 8.

The 9900 controls CRU-based I/O transfers between the memory and peripheral devices. Data must pass through the CPU during these program-driven I/O transfers, and the CPU may need to be synchronized with the I/O device by interrupts or statusbit polling.

Some I/O devices, such as disk units, transfer large amounts of data to or from memory. Program driven I/O can require relatively large response times, high program overhead, or complex programming techniques. Consequently, direct memory access (DMA) is used to permit the I/O device to transfer data to or from memory without CPU intervention. DMA can result in a high I/O response time and system throughput, especially for block data transfers. The DMA control circuitry is somewhat more expensive and complex than the economical CRU I/O circuitry and should therefore be used only when required. The 9900-based DMA can occur in the same modes as dynamic memory refresh: block, cycle stealing, or transparent. The transparent DMA mode is implemented similar to the refresh mode and must be synchronized with memory refresh cycles if dynamic memory is used. The block and cycle stealing modes, however, use the CPU HOLD capability and are more commonly used. The I/O device holds HOLD active (low) when a DMA transfer needs to occur. At the beginning of the next available non-memory cycle, the CPU enters the hold state and raises HOLDA to acknowledge the HOLD request. The maximum latency time between the hold request and the hold acknowledge is equal to three clock cycles plus three memory cycles. The minimum latency time is equal to one clock cycle. A 3-megahertz system with no wait cycles has a maximum hold latency of nine clock cycles or 3 microseconds and a minimum hold latency of one clock cycle or 0.3 microseconds.

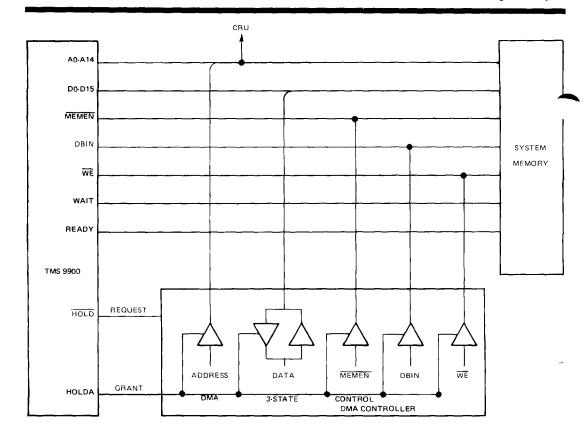

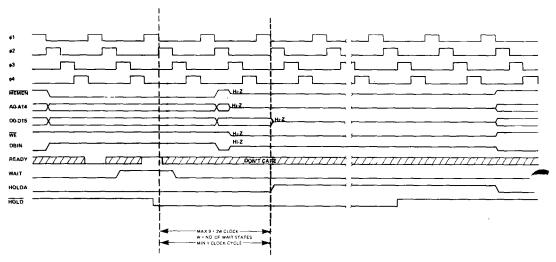

When HOLDA goes high, the CPU address bus, data bus, DBIN, MEMEN, and WE are in the high-impedance state to allow the I/O device to use the memory bus. The I/O device must then generate the proper address, data, and control signals and timing to transfer data to or from the memory as shown in *Figure 4-34*. Thus the DMA device has control of the memory bus when the TMS 9900 enters the hold state (HOLDA = 1), and may perform memory accesses without intervention by the microprocessor. Since DMA operations, in effect remove the 9900 from control while memory accesses are being performed, no further discussion is provided in this manual. Because the lines shown in *Figure 4-34* go into high impedance when HOLDA = 1, the DMA controller must force these signals to the proper levels. The I/O device can use the memory bus for one transfer (cycle-stealing mode) or for multiple transfers (block mode). At the end of the DMA transfer, the I/O device releases HOLD and normal CPU operation proceeds. The 9900 HOLD and HOLDA timing are shown in *Figure 4-35*.

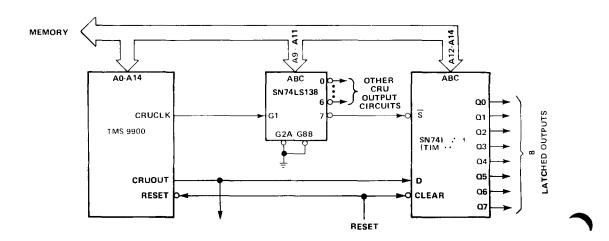

### MEMORY MAPPED I/O

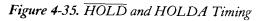

Memory mapped I/O permits I/O data to be addressed as memory with parallel data transfer through the system data bus. Memory mapped I/O requires a memory bus compatible interface; that is, the device is addressed in the same manner as a memory, thus the interface is identical to that of memory. *Figure 4-36* shows a memory mapped I/O interface with eight latched outputs and eight buffered inputs. In using memory mapped I/O for output only, care must be taken in developing the output device strobe to ensure it is not enabled during the initial read of the memory address, since the 9900 family of processors first reads, then writes data to a memory location in write operations. This can be effectively accomplished by using the processor write control signal WE in decoding the output address.

# INPUT/OUTPUT

Hardware Design: Architecture and Interfacing Techniques

Figure 4-34. DMA Bus Control

▶4

Figure 4-36. 8-Bit Memory Mapped I/O Interface

# Communication Register Unit (CRU)

CRU I/O uses a dedicated bit addressable interface for I/O. The CRU instructions permit transfer of one to sixteen bits. The CRU interface requires fewer interface signals than the memory interface and can be expanded without affecting the memory system. In the majority of applications, CRU I/O is superior to memory mapped I/O as a result of the powerful bit manipulation capability, flexible field lengths, and simple bus structure.

The CRU bit manipulation instructions eliminate the masking instructions required to isolate a bit in memory mapped I/O. The CRU multiple-bit instructions allow the use of I/O fields not identical to the memory word size, thus permitting optimal use of the I/O interface. Therefore, the CRU minimizes the size and complexity of the I/O control programs, while increasing system throughput.

The CRU does not utilize the memory data bus. This can reduce the complexity of printed circuit board layouts for most systems. The standard 16-pin CRU I/O devices are less expensive and easier to insert than larger, specially designed, memory mapped I/O devices. The smaller I/O devices are possible as a result of the bit addressable CRU bus which eliminates the need for multiple pins dedicated to a parallel-data bus with multiple control lines. System costs are lower because of simplified circuit layouts, increased density, and lower component costs.

# CRU Interface

The interface between the 9900 and CRU devices consists of address bus lines A0-A14, and the three control lines, CRUIN, CRUOUT, and CRUCLK as shown in *Figure 4-33*. A0-A2 indicate whether data is to be transferred and A3-A14 contain the address of the selected bit for data transfers; therefore, up to 2<sup>12</sup> or 4,096 bits of input and 4,096 bits of output may be individually addressed. CRU operations and memory-data transfers both use A0-A14; however, these operations are performed independently, thus no conflict arises. The MEMEN line may be used to distinguish between CRU and memory cycles.

# CRU Interface Logic

CRU based I/O interfaces are easily implemented using either CRU peripheral devices such as the TMS 9901 or the TMS 9902, or TTL multiplexers and addressable latches, such as the TIM 9905 (SN74LS251) and the TIM 9906 (SN74LS259). These I/O circuits can be easily cascaded with the addition of simple address decoding logic.

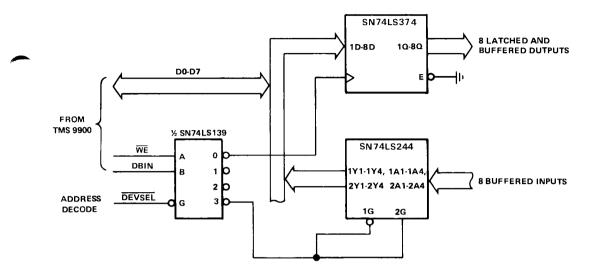

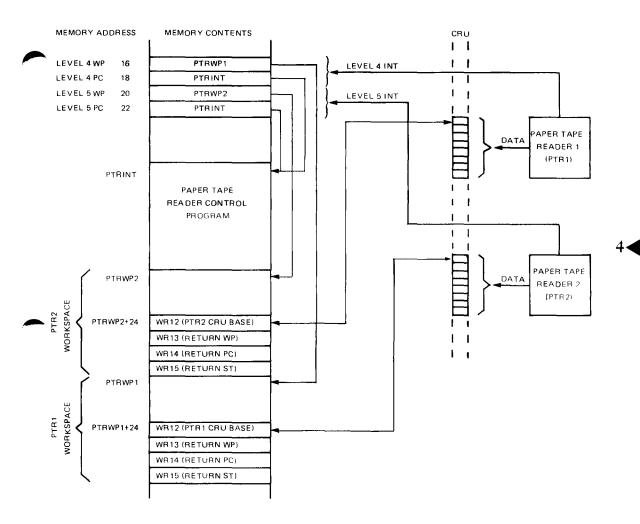

TTL Outputs. The TIM 9906 (SN74LS259) octal-addressable latch can be used for CRU outputs. The latch outputs are stable and are altered only when the CRUCLK is pulsed during a CRU output transfer. Each addressable latch is enabled only when addressed as determined by the upper address bits. The least-significant address bits (A12-A14) determine which of the eight outputs of the selected latch is to be set equal to CRUOUT during CRUCLK, and shown in Figure 4-37.

Figure 4-37. Latched CRU Interface

Figure 4-38. Multiplexer CRU Interface

TTL Inputs. The SN74LS151 and TIM 9905 (SN74LS251) octal multiplexers are used for CRU inputs as shown in *Figure 4-38*. The multiplexers are continuously enabled with

CRUIN equal to the addressed input. The TIM 9905 should be used for larger systems since its three-state outputs permit simple "wire-ORing" of parallel-input multiplexers.

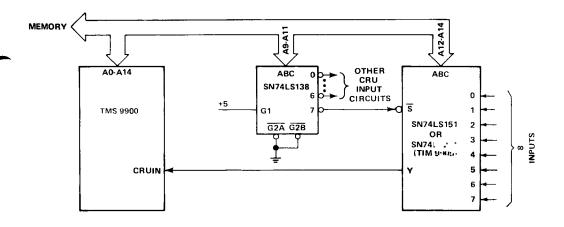

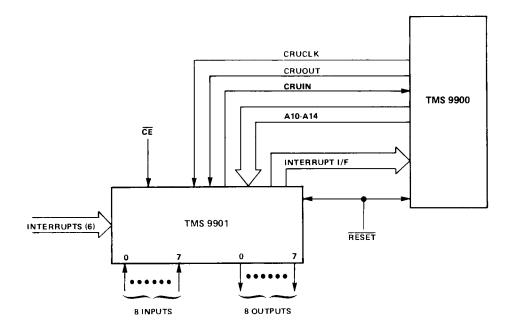

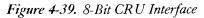

## Expanding CRU I/O

A CRU interface with eight inputs and eight outputs is shown in *Figure 4-39* using the TMS 9901. An expanded interface with 16 inputs and 16 outputs is shown in *Figure 4-40* using TTL devices. The CRU inputs and outputs can be expanded up to 4096 inputs and 4096 outputs by decoding the complete CRU address. Larger I/O requirements can be satisfied by using memory mapped I/O or by using a CRU bank switch, which is set and reset under program control. When reset, the lower CRU I/O bank is selected, and when set, the upper CRU I/O bank is selected. In actual system applications, however, only the exact number of interface bits required need to be implemented. It is not necessary to have a 16-bit CRU output register to interface a 10-bit device.

## CRU Machine Cycles

Each CRU operation consists of one or more CRU output or CRU input machine cycles, each of which is two clock cycles long. As shown in *Table 4-2*, five instructions (LDCR, STCR, SBO, SBZ, TB) transfer data to or from the 9900 with CRU machine cycles, and five external control instructions (IDLE, RSET, CKOF, CKON, LREX) generate control signals with CRU output machine cycles.

# INPUT/OUTPUT

Figure 4-40. 16-Bit CRU Interface

| INSTRUCTION | NUMBER OF<br>CRU CYCLES | TYPE OF<br>CRU CYCLES | A0-A2       | DATA<br>TRANSFER |

|-------------|-------------------------|-----------------------|-------------|------------------|

| LDCR        | 1-16                    | Output                | 000         | Yes              |

| STCR        | 1-16                    | Input                 | 0 0 0       | Yes              |

| SBO         | 1                       | Output                | 0.0.0       | Yes              |

| SBZ         | 1                       | Output                | 000         | Yes              |

| ТВ          | 1                       | Input                 | 0.0.0       | Yes              |

| IDLE        | 1                       | Output                | $0\ 1\ 0$   | No               |

| RSET        | 1                       | Output                | $0\ 1\ 1$   | No               |

| CKOF        | 1                       | Output                | $1 \ 0 \ 1$ | No               |

| CKON        | 1                       | Output                | 110         | No               |

| LREX        | 1                       | Ouput                 | 111         | No               |

| Table 4-2. Instructions Generating CRU | Cycles |

|----------------------------------------|--------|

|----------------------------------------|--------|

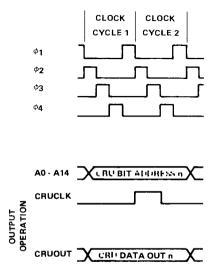

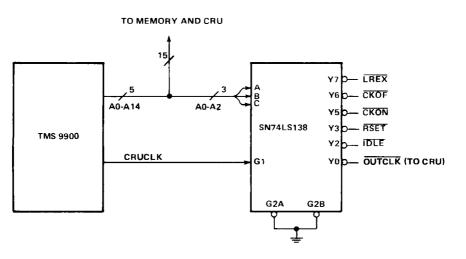

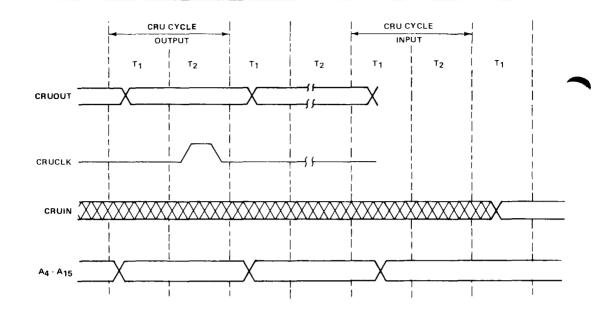

Figure 4-41 shows the timing for CRU output machine cycles. Address (A0-A14) and data (CRUOUT) are output on  $\phi 2$  of clock cycle 1. One clock cycle later, the 9900 outputs a pulse on CRUCLK for  $\frac{1}{2}$  clock cycle. Thus, CRUCLK can be used as a strobe, since address and data are stable during the pulse. Referring again to Table 4-2, it is important to note that output data is transferred only when A0-A2 = 000. Otherwise, no data transfer should occur, and A0-A2 should be decoded to determine which external

control instruction is being executed. These external control instructions may be used to perform simple control operations. The generation of control strobes for external instructions and a data transfer strobe (OUTCLK) is illustrated in *Figure 4-42*. If none of the external control instructions is used, A0-A2 need not be decoded for data transfer since they will always equal 000.

Figure 4-41. CRU Output Machine Cycle Timing

Figure 4-42. CRU Control Strobe Generation

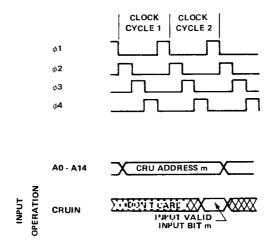

The timing for CRU *input* machine cycles is shown in *Figure 4-43*. The address is output at the beginning of the first clock cycle. The CRUIN data input is sampled on  $\phi 1$  of clock cycle 2. Thus, CRU input is accomplished by simply multiplexing the addressed bit onto the CRUIN input. A0-A2 will always be 000, and may be ignored. CRU input machine cycles cannot be differentiated from ALU cycles by external logic, thus no operations (such as clearing interrupts) other than CRU input should be performed during CRU input machine cycles.

Figure 4-43. CRU Input Machine Cycle Timing

# CRU Data Transfer

In order to transfer data from a memory location to an external latch in the Communications Register Unit, or to transfer data from a CRU multiplexer to memory, special instructions must be used. The CRU instructions are:

| SBO  | Set bit to one (output)         |

|------|---------------------------------|

| SBZ  | Set bit to zero (output)        |

| ТВ   | Test bit (input)                |

| LDCR | Load n bits to CRU (output)     |

| STCR | Receive n bits from CRU (input) |

|      |                                 |

These instructions always use the address bus to identify the bit or bits to be transferred, but they make the actual transfer of data over the dedicated CRU lines, CRUIN and CRUOUT. Addressing of the CRU bits is accomplished by adding a portion of the instruction word to a CRU base address register. The use of such a base address technique allows one program segment to service any number of identical I/O devices. For example: five TMS 9902's each with its own assigned base address can be operated from a single program, provided the base address register is properly set at the beginning. In the 9900, workspace register 12 is the CRU software base address register. All CRU instructions use the contents of this register in addressing individual CRU bits.

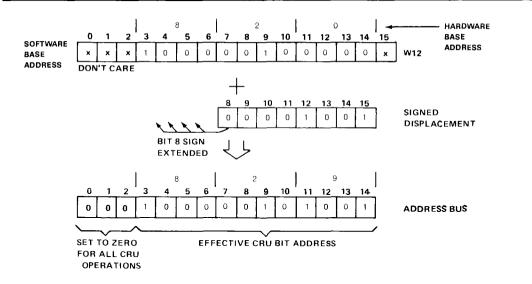

The CRU hardware base address is defined by bits 3-14 of the current WR12 when CRU data transfer is performed. Bits 0-2 and bit 15 of WR12 are ignored for CRU address determination.

For single-bit CRU instructions (SBO, SBZ, TB), the address of the CRU bit to or from which data is transferred is determined as shown in *Figure 4-44*. Bits 8-15 of the machine code instruction contain a signed displacement. This signed displacement is added to the CRU hardware base address (bits 3-14 of WR12). The result of this addition is output on A3-A14 during the CRU output or the CRU input machine cycle.

For example, assume the instruction "SBO 9" is executed when WR12 contains a value of  $1040_{16}$ . The machine code for "SBO 9" is  $1D09_{16}$  and the signed displacement is  $0009_{16}$ . The CRU hardware base address is  $0820_{16}$  (bits 0-2 and bit 15 are ignored). Thus, the effective CRU bit address is  $0820_{16} + 0009_{16} = 0829_{16}$ , and this value is output on A0-A14 during the CRU output machine cycle.

As a second example, assume that the instruction TB -32 is executed when WR12=100<sub>16</sub>. The effective CRU address is 80<sub>16</sub>. (CRU hardware base) + FFEO<sub>16</sub> (signed displacement) = 60<sub>16</sub>. Thus, the TB -32 instruction in this example causes the value of the CRU input bit at address 60<sub>16</sub> to be transferred to bit 2 of the status register. This bit is tested in the execution of the JEQ or JNE instructions; if it is a one, the PC will be loaded with a new value (JEQ instruction).

# INPUT/OUTPUT

Hardware Design: Architecture and Interfacing Techniques

Figure 4-44. TMS 9900 Single-Bit CRU Address Development

# LDCR Instruction

The LDCR may transfer from 1 to 16 fits of output data with each instruction. Output of each bit is performed by a CRU output machine cycle; thus, the number of CRU output machine cycles performed by an LDCR instruction is equal to the number of bits to be transferred.

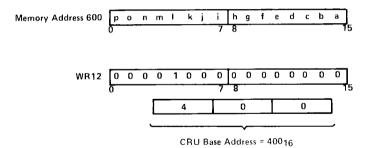

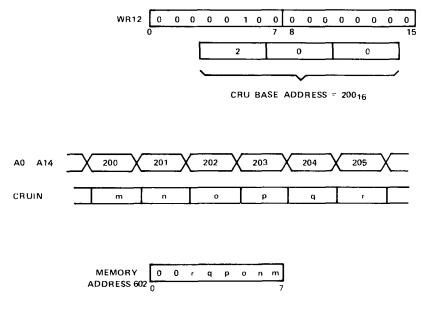

As an example, assume that the instruction "LDCR (a)600,10" is executed, and that  $WR12 = 800_{16}$  and the memory word at address 600 contains the bit pattern shown in *Figure 4-45*. In the first CRU output machine cycle the least significant bit of the operand (a) is output on CRUOUT. In each successive machine cycle the address is incremented by one and the next least-significant bit of the operand is output on CRUOUT, until 10 bits have been output. It is important to note that the CRU base address is unaltered by the LDCR instruction, even though the address is incremented as each successive bit is output.

# STCR Instruction

The STCR instruction causes from 1 to 16 bits of CRU data to be transferred into memory. Each bit is input by a CRU input machine cycle.

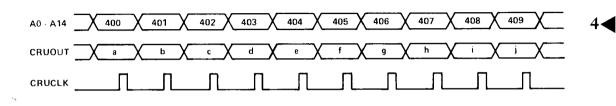

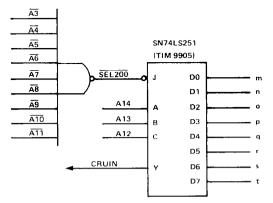

Consider the circuit shown in *Figure 4-46*. The CRU interface logic multiplexes input signals m-t onto the CRUIN line for addresses  $200_{16}$ - $207_{16}$ . If WR12 =  $400_{16}$  when the instruction "STCR (a) 602,6" is executed, the operation is performed as shown in *Figure 4-47*. At the end of the instruction, the six LSBs of memory byte 602 are loaded with m-r. The upper bits of the operand are forced to zero.

Figure 4-45. Multiple-Bit CRU Output

Figure 4-46. Example CRU Input Circuit

# INPUT/OUTPUT

Figure 4-47. Multiple-Bit CRU Input

# CRU Paper Tape Reader Interface

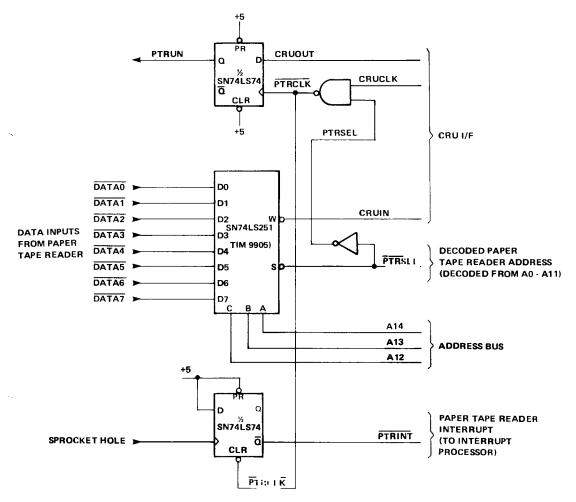

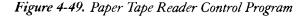

CRU interface circuits are used to interface data and control lines from external devices to the 9900. This section describes an example interface from a paper tape reader. The paper tape reader is assumed to have the following characteristics:

- 1. It generates a TTL-level active-high signal (SPROCKET HOLE) on detection of a sprocket hole on the paper tape.

- 2. It generates an 8-bit TTL active-low data which stays valid during SPROCKET HOLE = 1.

- 3. It responds to a TTL-level active-high command (Paper Tape RUN) signal by turning on when PTRUN = 1 and turning off when PTRUN = 0.

#### Hardware Design: Architecture and Interfacing Techniques

Figure 4-48 illustrates the circuitry to interface the reader to the CRU. The interface is selected when  $\overline{\text{PTRSEL}} = 0$ ;  $\overline{\text{PTRSEL}}$  is decoded from the A0-A11 address outputs from the 9900. Thus, the output of the SN74LS251 is active only when  $\overline{\text{PTRSEL}} = 0$ ; otherwise, the output is in high impedance and other devices may drive CRUIN. The data inputs are selected by A12-A14 and inverted, resulting in active high data input on CRUIN. The positive transition of SPROCKET HOLE causes  $\overline{\text{PTRINT}}$  to go low.  $\overline{\text{PTRINT}}$  is the active low interrupt from the interface.  $\overline{\text{PTRINT}}$  is set high, clearing the interrupt, whenever a CRU output machine cycle is executed and the address causes  $\overline{\text{PTR}} \cdot I \ \overline{L}$  to be active. When a one is output,  $\overline{\text{PTRUN}}$  is set, enabling the reader, and the reader is disabled when a zero is output to the device. Thus, any time  $\overline{\text{PTRUN}}$  is set or reset, the interrupt is automatically cleared.

Figure 4-48. Paper Tape Reader Interface

# INPUT/OUTPUT