with the exception of the enable preci the WD1773 is identical to the WD17 is fully software compatible with the WD1770-00 and WD1773-00 are comp FD179X stepping rates, while the WI stepping rates of 2, 3, 6, and 12 mse The WD177X-00 devices all contain a data separator which virtually elimina components and adjustments associ

|   | 2.0 |      | M N  |

|---|-----|------|------|

|   | 21  | WG   | WF   |

|   | 22  | WD   | WF   |

|   | 23  | TROO | TR.  |

|   | 24  | ĪP   | באַנ |

|   | 25  | WPRT | WF   |

| 1 |     |      |      |

#### ARCHITECTURE

The primary sections of the Floppy the Parallel Processor Interface a Interface.

Data Shift Register - This 8-bit serial data from the Read Data Read operations and transfers ser Data output during Write operat Data Register - This 8-bit register i register during Disk Read and V disk Read operations, the asser transferred in parallel to the Data Data Shift Register. In Disk Writ mation is transferred in paral Register to the Data Shift Regis When executing the Seek Co Register holds the address of the Timing and Control - All computer interface controls are generated to the internal device timing is generated and crystal clock. The WD177X-00 modes of operation according DDEN.

When DDEN = 0, double density When DDEN = 1, single density AM Detector - The address mark dedata and index address marks during the single density data and index address marks during the single density den

operations.

Data Separator – A digital data sep of a ring shift register and data valogic provides read data and a reci-AM detector. density is selected. In either cas at 8 MHz.

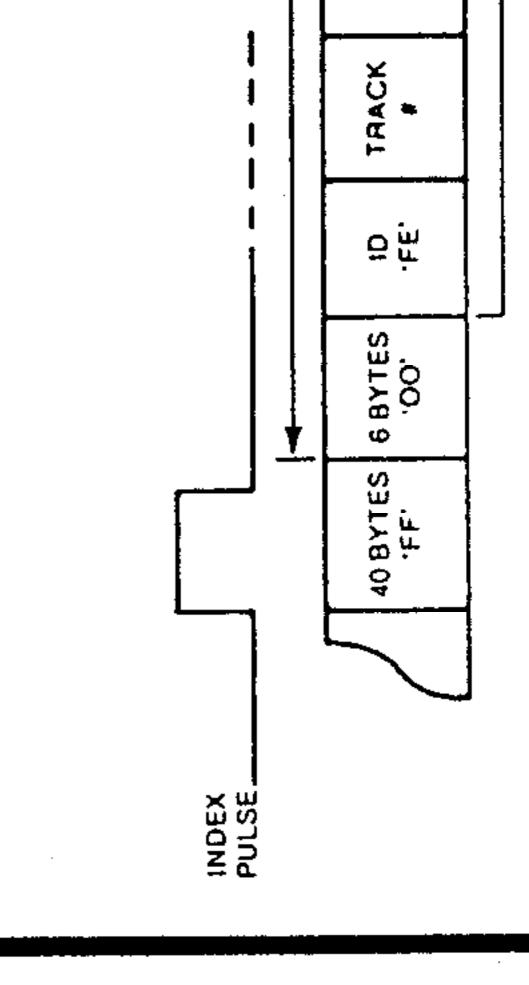

GENERAL DISK READ OPERATION

Sector lengths of 128, 256, 512 or in either FM or MFM formats is placed to logical 1. For MFM placed to a logical 0. Sector length at format time by the fourth by

| SECTOR        | SECTOR LENGTH |  |

|---------------|---------------|--|

| SECTOR LENGTH | NUI           |  |

| FIELD (HEX)   | IN SI         |  |

| 00            |               |  |

| 01            |               |  |

| 02            |               |  |

| 03            |               |  |

m = Multiple Sector Flag (Bit 4) m = 0, Single Sector m = 1, Multiple Sector H = Motor on Flag (Bit 3) (1770) H = 0, Enable Spin-up Sequence = 1, Disable Spin-up Sequen = Side Compare Flag (Bit 3) (1 = 0. Compare for side 0 S = 1, Compare ;for side 1 For all Type III commands bit 3 = Data Address Mark (Bit 0) ( = 0, Write Normal Data Mark ao = 1, Write Deleted Data Mark

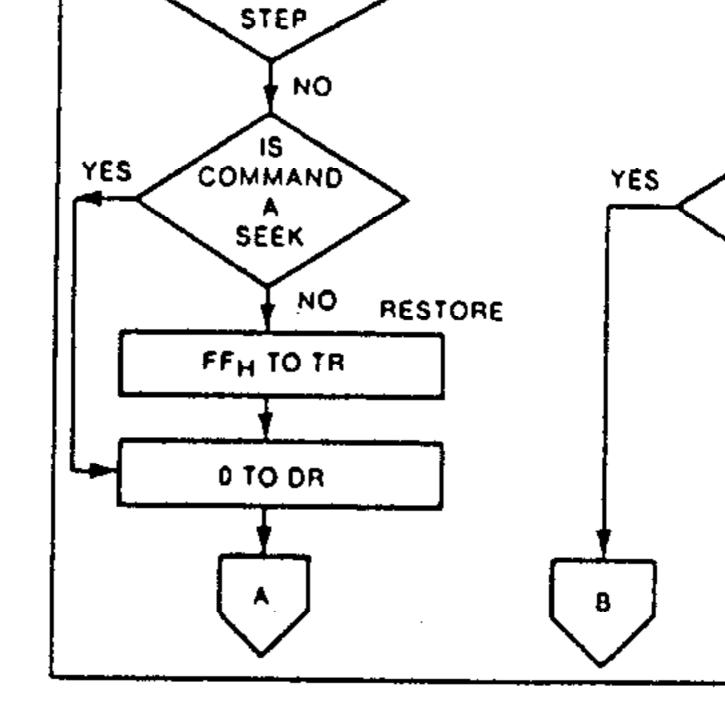

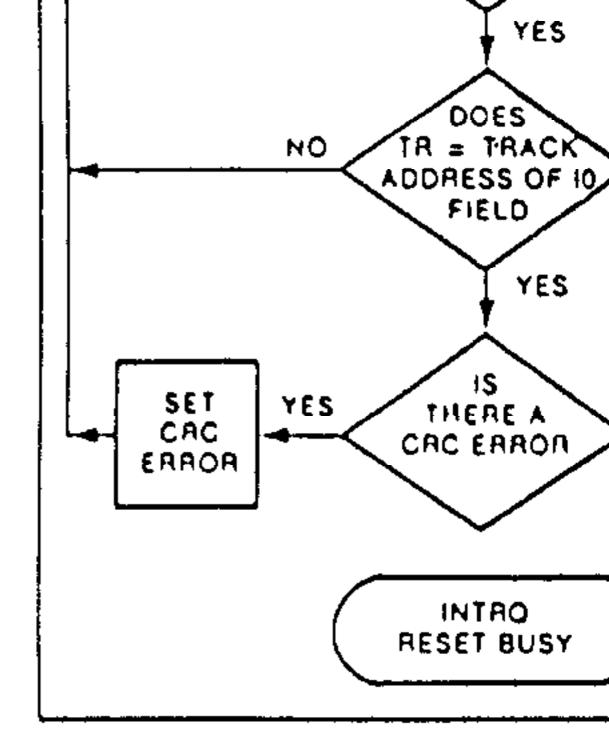

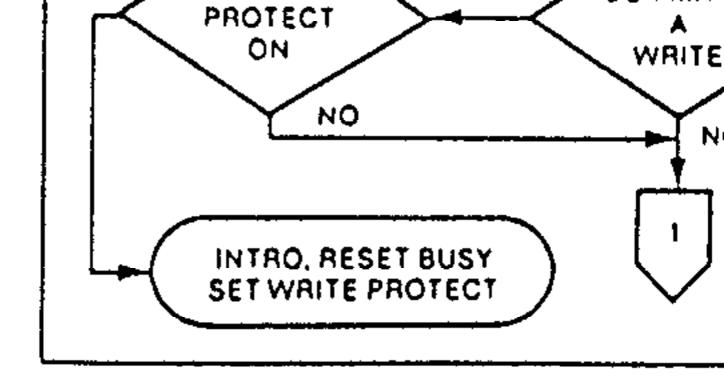

TYPE I COMMAND FLOW

TYPE I COMMAND F

### TYPE II COMMAND

Sector Register. If there is no Sector material and ID field is read off the disparisons again made. If the ID field CF the data field is located and is either waread from, depending upon the con WD177X-00 finds an ID field with a Track tor number, and CRC within four revolutisk, or, the Record Not Found Status bit Bit 4) and the command is terminated with the command is t

output is made active if the DRC DR is loaded by the computer). If the command is terminated and Bit is set. If the DRQ is service active and six bytes of zeroes in 12 bytes in double density are written and Address Mark is then writt termined by the a<sub>0</sub> field of the computer).

no CRC checking is performed;

| DATA PATTERN<br>IN DR (HEX) | IN FM (DD |

|-----------------------------|-----------|

| 00 thru F4                  | Write 00  |

| F5                          | Not Allow |

| F6                          | Not Allow |

| F7                          | Generate  |

| F8 thru FB                  | Write F8  |

| FC                          | Write FC  |

| FD                          | Write FD  |

| FE                          | Write FE, |

| FF                          | Write FF  |

<sup>\*</sup>Missing clock transition between

<sup>\*\*</sup>Missing clock transition between

## Status Register

Upon receipt of any command, ex rupt Command, the Busy Status E of the status bits are updated or command. If the Force Interrupt C when there is a current comman the Busy Status Bit is reset, and t bits are unchanged. If the Force is received when there is not a under execution, the Busy Status rest of the status bits are update case, Status reflects the Type I The user has the option of reading through program control or using DMA or interrupt methods. When is read the DRQ bit in the Statu

DRQ line are automatically reset

Register also causes both DRQ

Floppy Disk Controller Devices

| FOUND (RNF)              | bit is re                               |

|--------------------------|-----------------------------------------|

| <br>S3 CRC ERROR         | If S4 is<br>error da                    |

| S2 LOST DATA/<br>BYTE    | When s<br>This bit<br>status            |

| S1 DATA REQUEST<br>INDEX | This bit<br>Read O<br>when u<br>signal. |

| S0 BUSY                  | When s                                  |

| S6 WRITE PROTECT             | On Read<br>Write Pro               |

|------------------------------|------------------------------------|

| S5 RECORD TYPE               | On Read<br>1 = Del                 |

| S4 RECORD NOT<br>FOUND (RNF) | When se is reset                   |

| S3 CRC ERROR                 | If S4 is s<br>in data f            |

| S2 LOST DATA                 | When se                            |

| S1 DATA REQUEST              | This bit i<br>Operatio<br>updated. |

| S0 BUSY                      | When se                            |

READ ENABLE TIMING - RE suc

| SYMBOL                                                            | CHARACT                                                                                   |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| t <sub>RE</sub> t <sub>DRR</sub> t <sub>DV</sub> t <sub>DOH</sub> | RE Pulse Width<br>DRQ Reset from<br>Data Valid from<br>Data Hold from<br>INTRO Reset from |

Note: DRQ and INTRQ reset are (leading) of WE. Worst ca

| t <sub>WE</sub><br>t <sub>DRW</sub> | DRQ Reset from Data Setup to W    |

|-------------------------------------|-----------------------------------|

| t <sub>DH</sub>                     | Data Hold from<br>INTRQ Reset fro |

# **READ DATA TIMING:**

|          | CHARACTERISTIC |

|----------|----------------|

| Raw Read | Pulse Width    |

| Raw Read | Cycle Time     |

### **MISCELLANEOUS TIMING:**

| SYMBOL           | CHARACTER          |

|------------------|--------------------|

| t <sub>CD1</sub> | Clock Duty (low)   |

| t <sub>CD2</sub> | CLock Duty (high)  |

| t <sub>STP</sub> | Step Pulse Output  |

| tDIR             | Dir Setup to Step  |

| t <sub>MA</sub>  | Master Reset Pulse |

| t <sub>IP</sub>  | Index Pulse Width  |