/BEGIN /S 10 /C(IBC-1)/S. 2 /C(INTELLIGENT BUS CONTROLLER) 15.2 ÷., /C (DATA MANUAL) /S 12 /BEGIN INSERT Texas Instruments Consumer Products Group 5/10/82 **7END INSERT** /DOCUMENT(IBC-I Data Manual) **ZPRELIMINARY** /PB /PI(INTRODUCTION). /P2(DESCRIPTION) /P The IBC-I (Intelligent Bus Controller) is a interface device which provides capability for interfacing target system or microprocessor to the ALC peripheral bus. It will provide cost/performance advantages over discrete implementation and relieve software from numerous tasks which are necessary to supervise the bus. /P2(KEY FEATURES) /\* 4 BIT INSTRUCTION/DATA WORD /\* FULLY COMPATIBLE WITH TMS-7000, 8085 AND 6502 MPU families /\* EASY INTERFACE TO MOST 4 BIT MICROCONTROLLERS /\* 5 MODES OF OPERATION /\* CAPABILITY TO LATCH CS AND RS SIGNALS **7\* PROGRAMMABLE INTERRUPT WITH OPEN DRAIN OUPUT** /\* ITL/CMOS COMPATIBLE PINS /\* LOW POWER CMOS, 3 - 7 VOLT POWER SUPPLY /\* 22+PIN, 400-MIL, DUAL-IN-LINE PLASTIC PACKAGE /PB /P1(ARCHITECTURE) /P2(BLOCK DIAGRAM) /P /BEGIN INSERT 1<---- MS 1<---- RES-IOBC 1<---- E-1<---- RS CONTROL :<---- CS-LOGIC 1<-\*-->RD/WR-(03)ļ ł IALC I Data 1 loutout -\*->00-02 \* F 1 1 {register: 10-D3<-->!I/O 1 <u> > !</u> ļ 10 <u>> </u> RO |<ţ lbuffer ł ١ 4 1 £ ł ł lbus 1 1 ! ; ţ ! 1 1 4 ľ ь ŗ ł U 1 7 ALC 1 1 1 1 Control : Status , *X* ¢ bus 4 10045 1 51 E ł 4

| 1 | ł   | ŧ | ł                                |           |

|---|-----|---|----------------------------------|-----------|

| ł | E E | f | ۰                                | HSK/RESET |

| 1 | Į   | ۰ |                                  | BAV       |

| ł |     |   |                                  | INHIBIT   |

| ۱ |     |   | ی مناله دارده سراه برری مربقه می | DISABLE   |

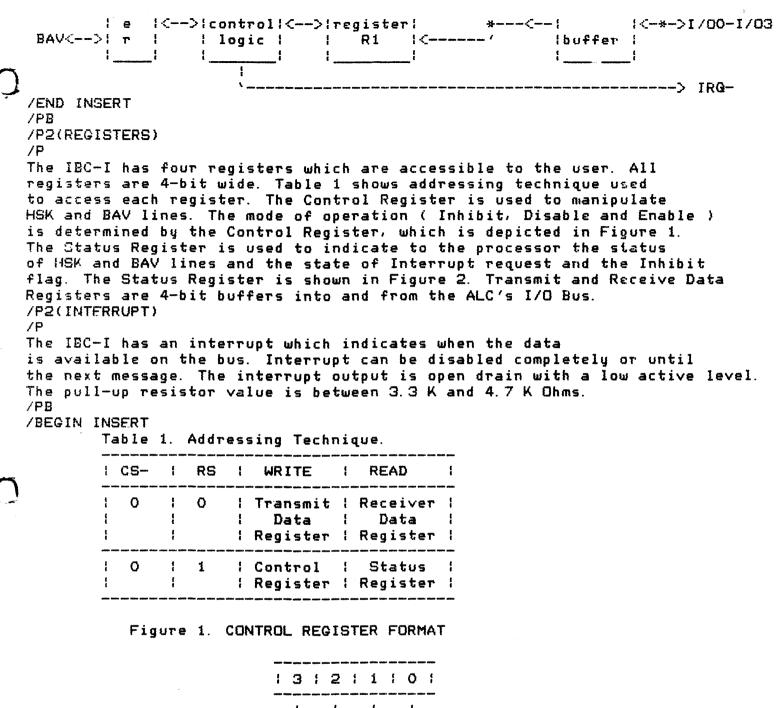

## Figure 2. Status Register Format

4

Ĩ

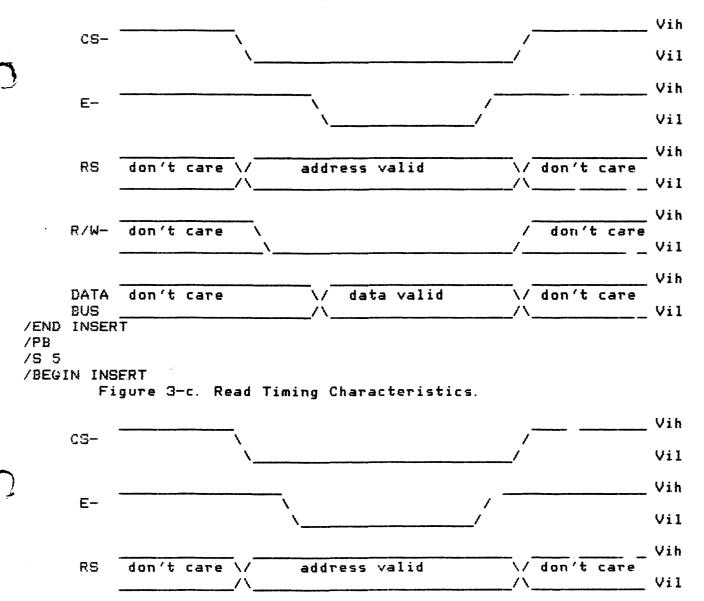

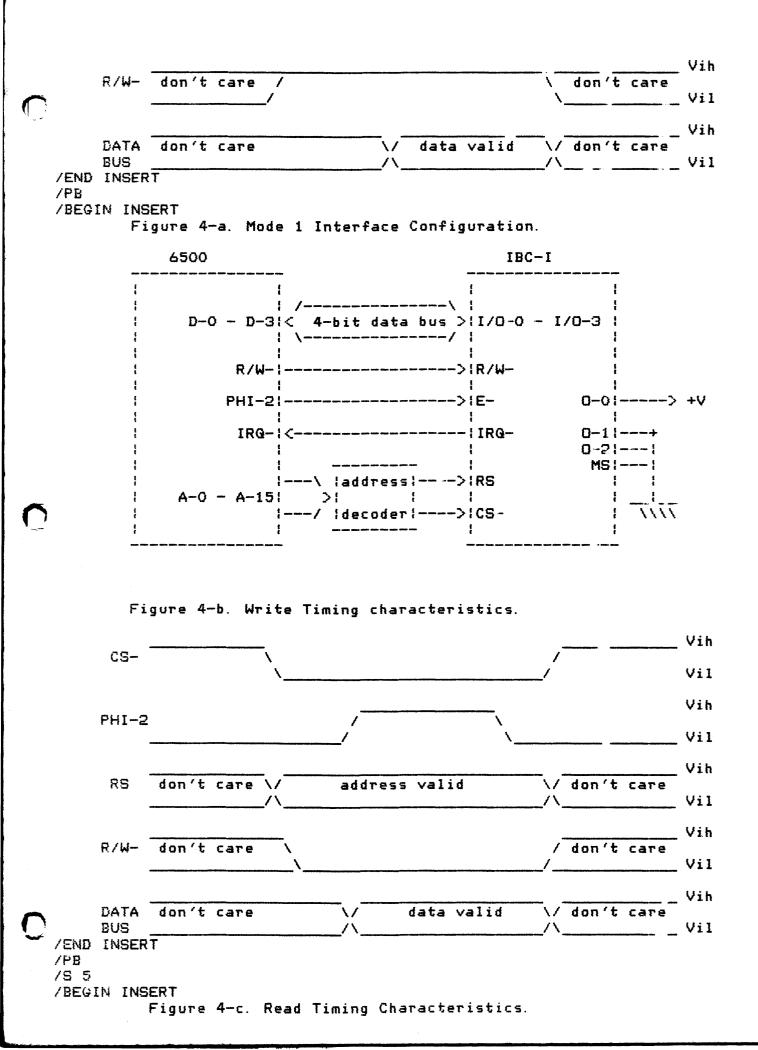

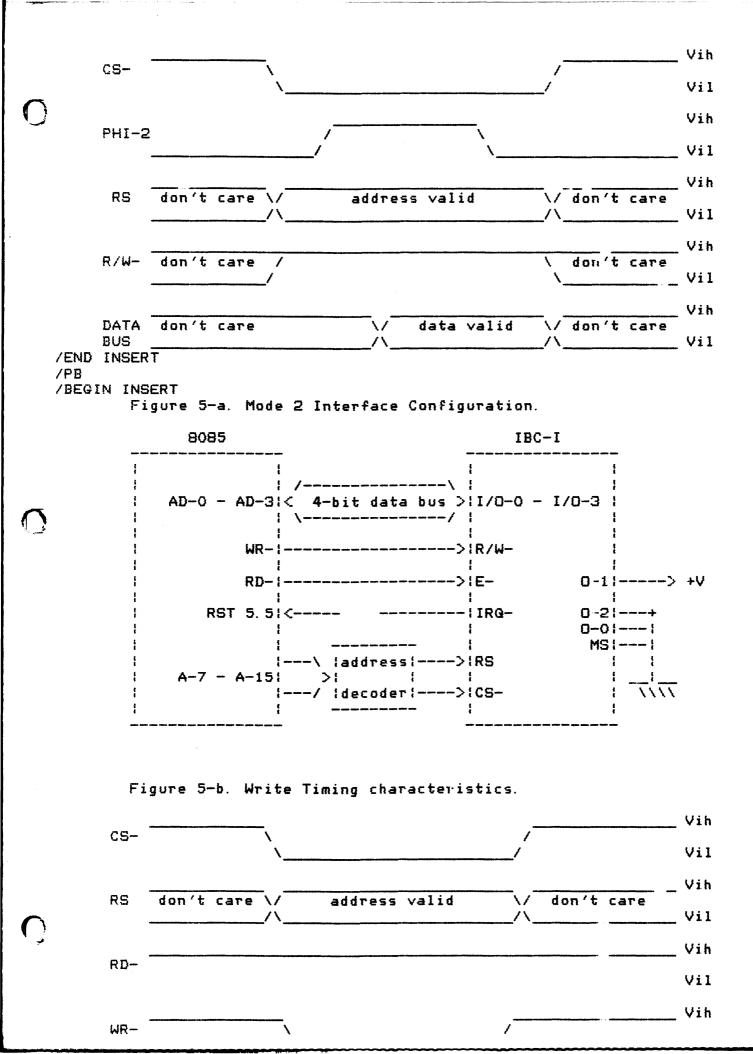

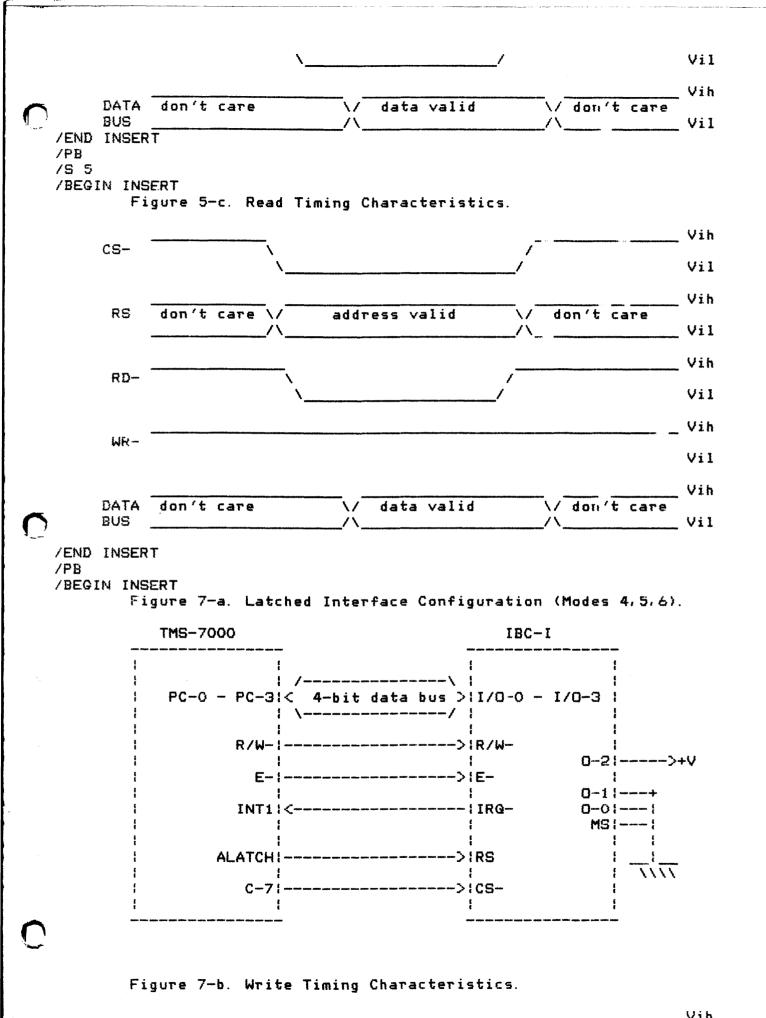

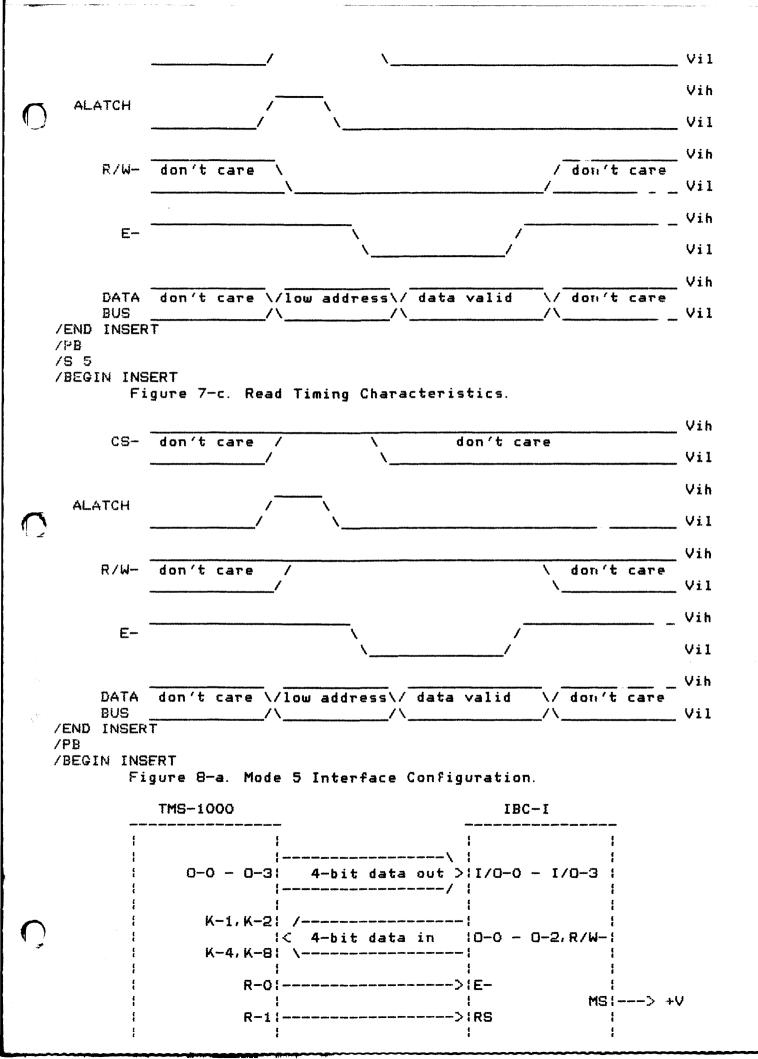

/END INSERT /PB /BEGIN INSERT Figure 3-a. Mode O Interface Configuration.

Figure 3-b. Write Timing Characteristics.

|     |       |      |   |              | <br>V 1 11 |

|-----|-------|------|---|--------------|------------|

| CS- | don't | care | 1 | \ don't care |            |

|     |       |      |   |              |            |

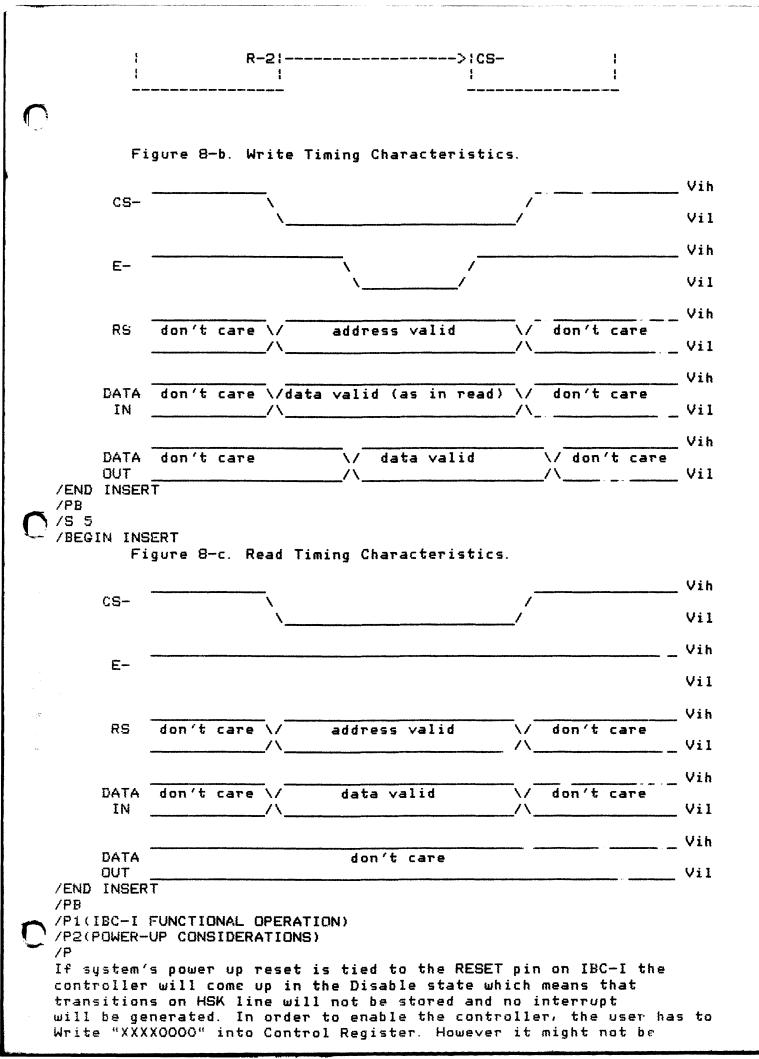

desirable to enable the controller in the middle of the message therefore user may perform Enable with "Inhibit Until New Message" by Writing "XXXX0100" into Control Register. This will keep the controller in disable state until a new message starts. /P2(SLAVE MODE) /P In listen mode user has to read the first two nibbles on the bus, determine if he was selected, and if he was, user can start communication with the master. If he was not selected user should perform "Inhibit Until New Message" by Writing "XXXX0100" into the Control Register. /P The capability exists for the user to monitor the communication even if he was not selected, however, this is not recommended since it may slow down the bus operation. This allows monitoring and recording of all bus communications. 7p In transmit mode, the user has to send the data utilizing the Write Sequence, monitor the HSK line and when the HSK line goes into an inactive state the user may transmit the next data. 18 When the user has a need to request service from the master and has permission to do so, the user may execute Request Service which is described in a later section. /P All receive data and transmit data can be handled by executing the Read and Write Sequences respectively. These sequences are described below. /PB /P2(READ SEQUENCE) /P The Read Sequence allows the user to obtain the data transmitted on the bus and prepares IBC-I to receive the next transmission. The Read Sequence has to be used whenever the user is in the listen mode and receives an interrupt from IBC-I. /BEGIN INSERT a - Reset Interrupt - Write "XXXX0001" into Control Register - Read Receiver Data Register b - Obtain Data c - Reset HSK Latch - Write "XXXX0000" into Control Register Figure 9. Read Sequence. /END INSERT /P2(WRITE SEQUENCE) /P The Write Sequence allows the user to place the data on the bus and to signal the other devices that the data is available. The Write Sequence has to be used whenever the user is in transmit mode and ready to send the data. /BEGIN INSERT - Write Data into Transmit Data Register a - Prepare Data - Write "XXXX0001" into Control Register b - Set HSK Signal c - Reset HSK Signal - Write "XXXX0000" into Control Register Figure 10. Write Sequence. /END INSERT /P2(REQUEST SERVICE SEQUENCE) /P The Request Service Sequence allows the user to signal the master by putting the BAV line into the low state until the first HSK transition. The Request Service Sequence may be used whenever the user has permission from the master to request the service. /BEGIN INSERT

----

## /END INSERT /PB /S 5 /BEGIN INSERT

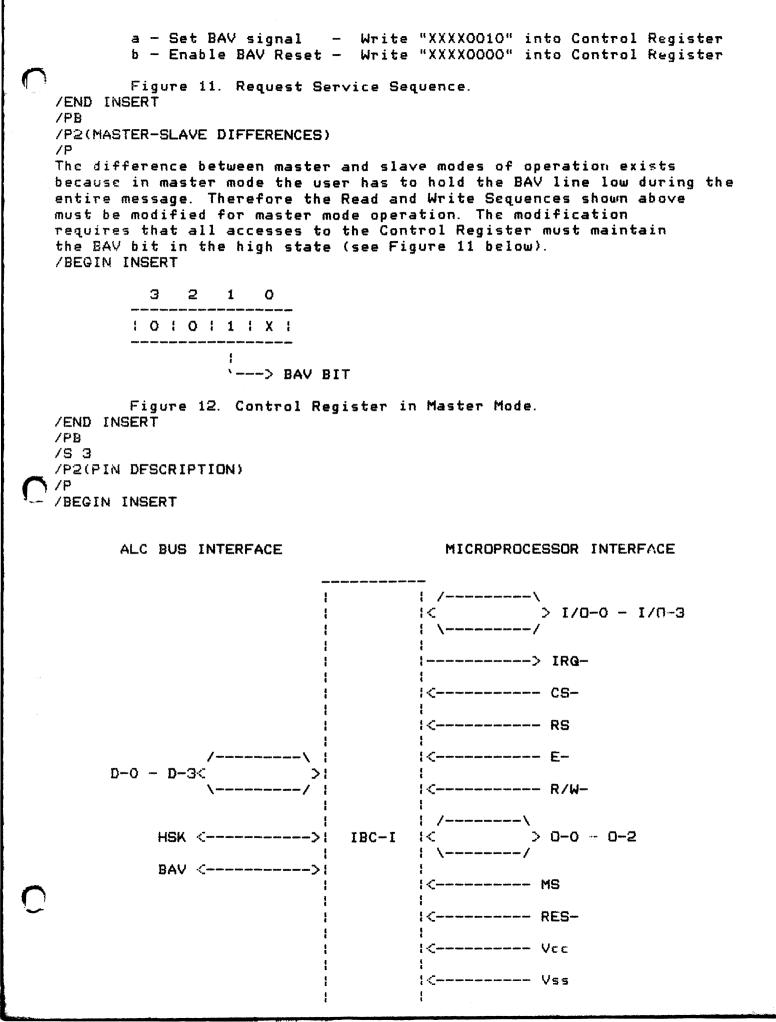

| :                | Name            | I/(             | ) (PIN #: | Description                                                                                                                                                                                                                       |

|------------------|-----------------|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| : D-             | 0 – D–          | 3: I/(<br> <br> |           | Data I/O lines that allow data transfer<br>between IBC-I and the ALC I/O bus.                                                                                                                                                     |

| * * *            | HSK             |                 | 1 1       | HANDSHAKE LINE: set low by source device to<br>indicate to listeners that there is valid<br>data on the ALC I/O bus and held low by the<br>listeners until they accept the data.                                                  |

|                  | BAV             |                 |           | BUS AVAILABLE LINE: set low by source<br>device in the beginning of the message and<br>held low until the end of the message.<br>The new source can originate a new message<br>or "Request Service" only if this line is<br>high. |

|                  | /0-0 -<br>I/0-3 |                 |           | Data I/O lines that allow data transfer<br>between IBC-I and the microprocessor.<br>If MS=1 act as inputs only.                                                                                                                   |

|                  | IRQ-            |                 | 7         | INTERRUPT OUTPUT (open drain): indicates to<br>to the microprocessor the occurence of the<br>next data nibble on the ALC I/O bus.                                                                                                 |

| ;<br>;<br>;      | CS-             | I               | 12        | CHIP SELECT INPUT: selects and enables the IBC-I for microprocessor data transfer.                                                                                                                                                |

| :<br>:<br>:<br>: | RS              | - ;<br>! I<br>! | ŧ 1       | REGISTER SELECT INPUT: address line through<br>which the IBC-I registers can be accessed<br>by the microprocessor.                                                                                                                |

$\bigcirc$

C

/BEGIN INSERT

|        | Name     | ł   | I/O   | PIN    | #1 | Description                                                                                                                                                                                                                 |

|--------|----------|-----|-------|--------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | E-       |     | <br>I | : 8    |    | ENABLE INPUT: if MS=0 there are several                                                                                                                                                                                     |

|        |          | ł   |       | 1      | 1  | options in combination with a pin R/W- for                                                                                                                                                                                  |

|        |          | i   |       | ł      | ł  | controlling data transfer between IBC-I and                                                                                                                                                                                 |

| ł      |          | ł   |       | ţ      | 1  | the microprocessor.                                                                                                                                                                                                         |

|        |          | i   |       | e<br>e | 1  | If MS=1, E- is used as active low strobe                                                                                                                                                                                    |

|        |          | f   |       | {      | 1  | for writing data into IBC-I.                                                                                                                                                                                                |

|        |          | 1   |       | 1      | ł  | For details see text.                                                                                                                                                                                                       |

|        | R/W-     |     | I/O   |        |    | READ-WRITE CONTROL: if MS=0 there are seve-<br>ral options in combination with a pin E-<br>for controlling direction of data transfer<br>between IBC-I and the microprocessor.<br>If MS=1, R/W- is used as most significant |

| i      |          | i   |       | i<br>t |    | bit of data outputs.<br>For details see text.                                                                                                                                                                               |

| -      |          | -1- |       | - {    |    |                                                                                                                                                                                                                             |

| $\cap$ | -n - n - | 21  | T /O  | 1 20   | ŧ  | OUTPUT DATA LINES: if MS=1 these lines are                                                                                                                                                                                  |

|  | 4<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | : 22<br> | <pre>! used as three least significant bits of<br/>! data outputs.<br/>! If MS=0 these lines are used for selecting<br/>! the options for pins R/W-, E- and IRQ</pre> |

|--|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | : MS                                                                                             | I                                                                                           | 18       | MODE SELECT: input which selects the mode of operation.                                                                                                               |

|  | ;<br>; RES-<br>;                                                                                 | 1                                                                                           | ŧ        | RESET INPUT: low level on this input will<br>put IBC-I into reset state.                                                                                              |

|  | •                                                                                                | i I                                                                                         | 19       | Positive supply (4.5 - 9.5 Vdc).                                                                                                                                      |

|  | •                                                                                                | •                                                                                           | •        | ;                                                                                                                                                                     |

/END INSERT /END

C

0