LSCU 1

PRELIMINARY SPECIFICATIONS

FOR VENDOR QUOTES

Texas Instruments Consumer Products Group

10/12/81

#### General Information

# 1.1 Quote Breakdown

Quotes are requested for Gate Array / Semi-Custom CMOS implementation of the losic provided. Expected volume requirements are indicated below. Fackage information is given in Section 2. Quotes are requested for the preferred package and invited for any alternate packages. The logic provided should be referred to as LSCU 1. A quote is also requested for a modification of this logic, referred to as LSCU 1-A. This modification reduces pin out requirements by eliminating latches and outputs associated with PC2, PC3, & PC4, and eliminating the use of A9, and A10 everywhere they appear in the logic (all other logic remains as shown in the diagrams).

### 1.2 Volume

- \* Packaged prototype units required by April 1, 1982

- \* First production 2H82: 10,000 20,000 units

- \* Production: 1083 20,000 units 2083 - 30,000 units 3083 - 50,000 units 4083 - 20,000 units

# 1.3 For Additional Information

For clarification or additional information contact

Chuck Branson

Design Engineer, Consumer Products Group

Texas Instruments, Inc.

P.O. Box 10508, M/S 5889

Lubbock, TX 79408

(806) 741-3020

O.F.

Randy Ahlfinser

Program Manager, Consumer Products Group

Texas Instruments, Inc.

P.O. Box 10508, M/S 5889

Lubbock, TX 79408

(804) 741-3215

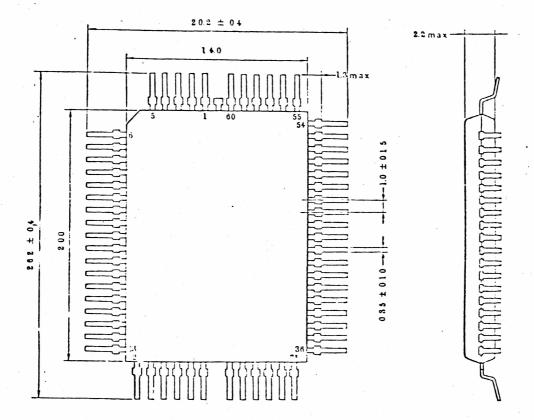

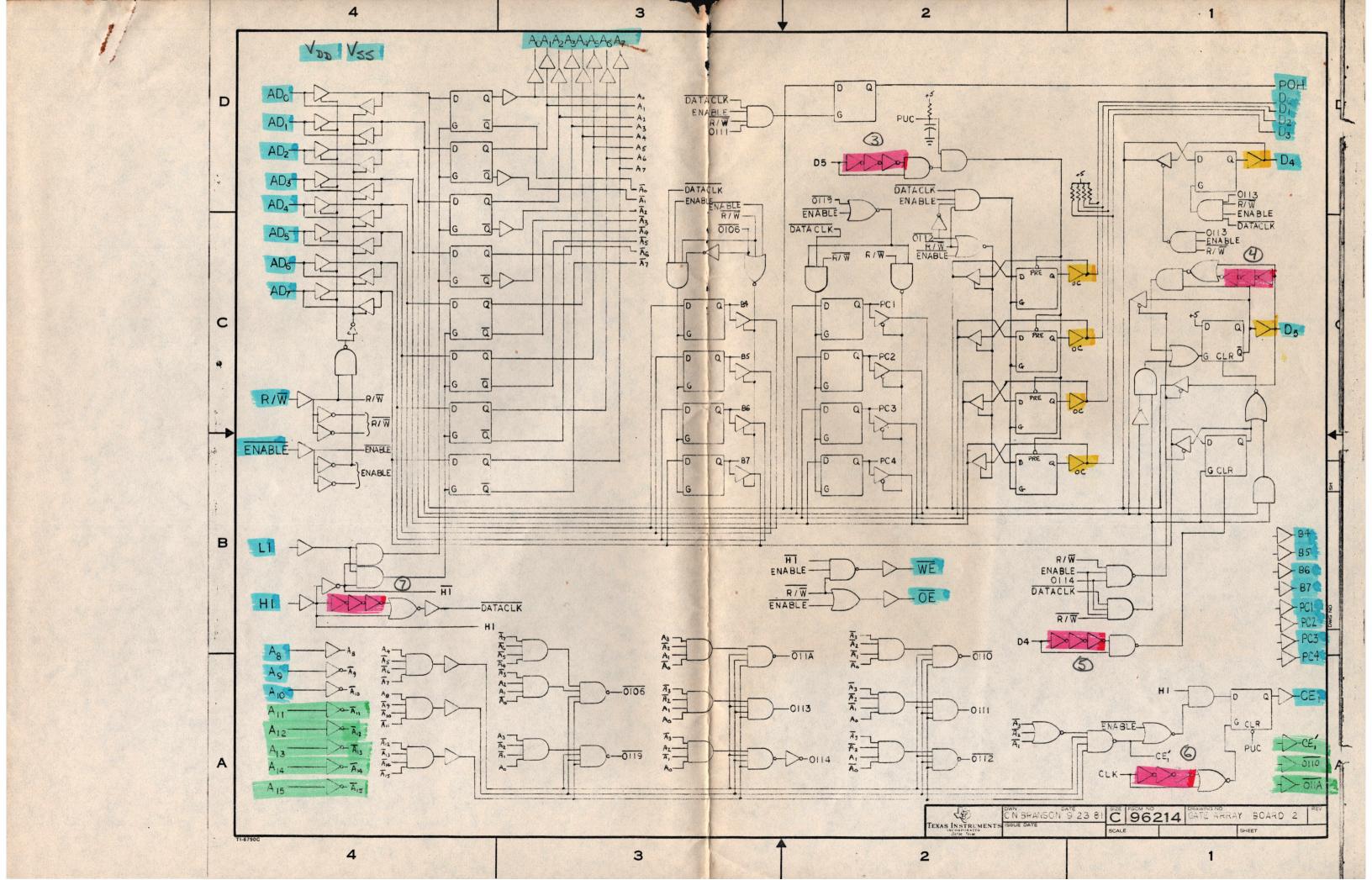

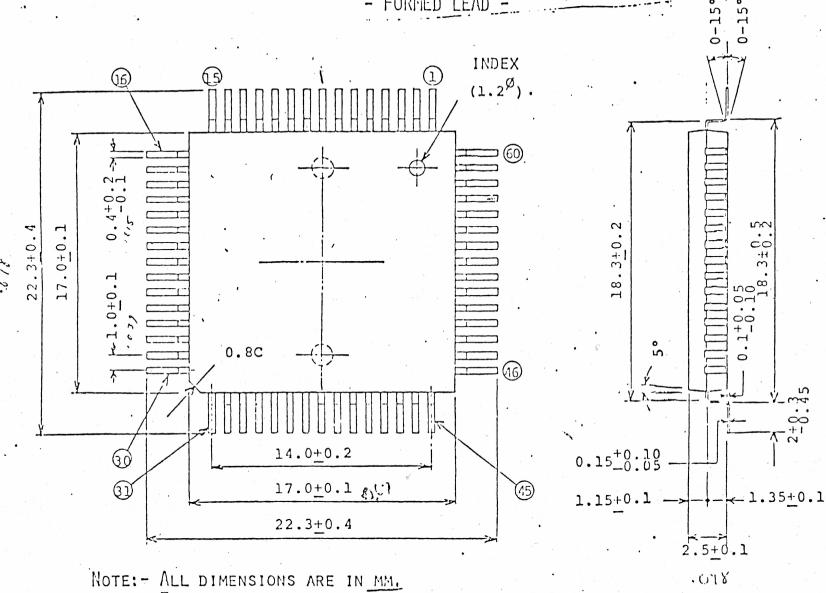

### PACKAGES

# 2.1 Preferred Package

- \* Form Quad Flat Pack

- \* Plastic

- \* Minimum Pin Count 60

- \* Maximum Overall Size 30 x 30 x 3 mm

- \* Leads Solderable

- \* Leads flush with bottom surface

- \* For example of package refer to the attached sheets

# 2.2 Other Packages (In order of acceptability)

- \* Pin Grid Array, RIT, Square pack

- \* LCC

- \* DIF

## Electrical Characteristics

- 1. Technology CMOS

- 2. Operating Temperature Range 0 C 470 C

4.3 - 5.8

- 3. Vdd Min: Vss + 4.5, MAx: Vss + 5.5

- 4. Inputs Typical CMOS compatibility

- 5. Outputs Typical CMOS compatibility except open drain outputs

- 6. Open drain outputs capable of sinking 10 mA (prelim)

- 7. Power less than 1 mW (dynamic, open drain outputs high)

- 8. Typical internal sate delay 25 ns @ 5 V (see note)

### NOTE

Critical paths are indicated on the logic diagrams and explained in Section 4

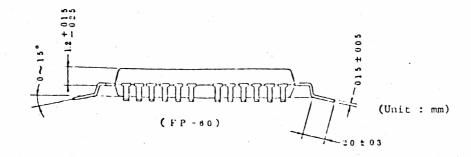

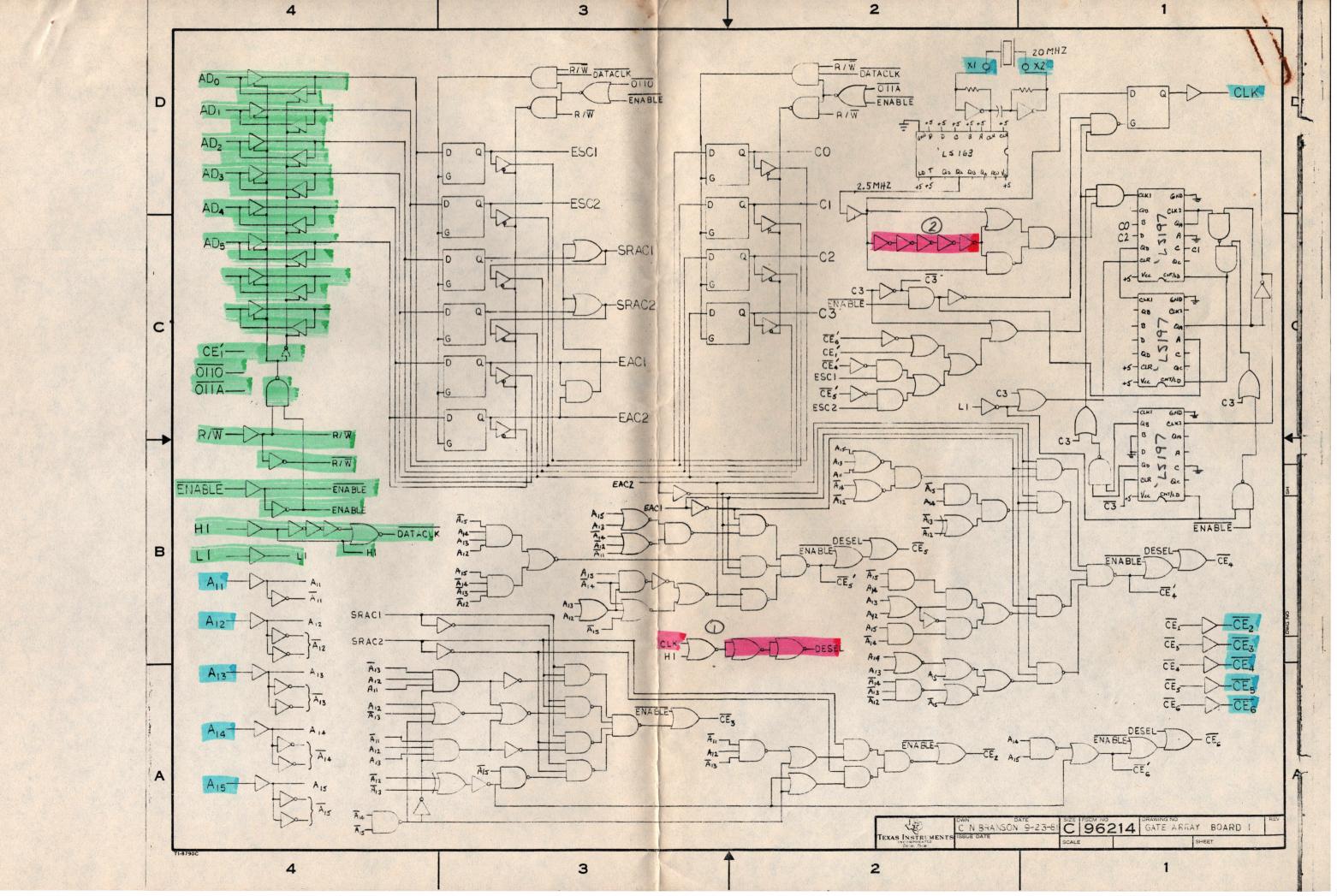

## Key to Color Coding on Logic Diagrams

- Green The diagrams were drawn for a two board, breadboard system. Some of the logic highlighted in green is duplicated due to the use of two boards and should only be built once. Three of the buffers highlighted in green are only for passing between the two boards and are not required at all in the final part.

- Blue Signals highlighted in blue indicate connections to I/O pads.

### NOTE

If power-up-clear circuitry cannot be implemented on the chip then an additional pad will be required for this.

Yellow - Buffers highlighted in Yellow are open-drain buffers.

- Pink Areas highlighted in pink indicate the paths which have been identified at this point as having critical timing requirements. The requirements are listed below.

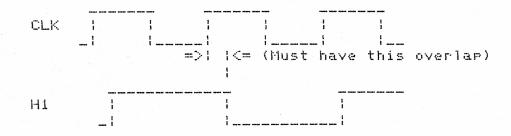

- 1. DESEL is derived from CLK and H1. H1 is externally derived from CLK. There will be some small delay between CLK edges and H1 edges. The path between the CLK circuitry and the NOR gate input should be as short as possible to ensure that no glitch will will occur when CLK goes high and H1 goes low (see timing below).

1.

In addition the delay between the NOR sate output and the sisnal indicated as DESEL should be approximately 100 ns.

- Delay in this double edge detector should be approximately 50 ns.

- 3. Delay should be sufficient to preset the latches.

- Delay should provide pulse capable of setting the latch.

- 5. Delay should provide sufficiently wide pulse to clear the latch.

- Delay should be sufficient to provide for opening the latch to the D input.

- Delay should be enough to provide pulse capable of operating the latch gates.

- EACH PIN CENTERLINE IS LOCATED WITHIN 0.2 OF ITS TRUE LONGITUDINAL POSITION

LEAD THICKNESS IS AFTER TIN PLATING

(4) Diagram of Package Dimentional Outline

(60-pin Plastic Flat Package)