LASS E D FI С T and a second C of Texas Instruments ONLY Property

ADD #2

# SR-70 HARDWARE FUNCTIONAL SPECIFICATIONS

DOD Memo 12 19940 Stat MB-141000 Proto BB-141000 Proto BB-51 51 84 VV KS235 84 VV KS235 84 VV KS235 0 TPD RURSTARS TO TADS 1000

| PREPARED BY | DATE |        | (ji) | TEXAS INSTRUMENTS<br>INCORPORATED |       |

|-------------|------|--------|------|-----------------------------------|-------|

| CHECKED BY  | DATE | TITLE: |      | • ·                               |       |

| ENGINEER    | DATE | -      |      |                                   | · .   |

| APPROVED BY | DATE |        | 01 1 |                                   | SHEET |

| RELEASED BY | DATE | 01295  | A    |                                   | 1     |

# MEMORANDUM

22 May 1978

TO:

Johnny Acker Mike Anderson David Brown Mike Bunyard Byron Crowe Mike Fulghum Bill Ham Roy Smith Roger Tilbury

Dick Houghton Steve Indvik Gary LaGrange Jerry Maxwell Jerry Ogarek Stav Prodromou Gary Slagel Jerry Wardrum

COPY TO: Rex Naden Deene Ogden Ron Webb

FROM: Don Mills

SUBJECT:

SR-70 HARDWARE FUNCTIONAL SPECIFICATION REVIEW

A review of the SR-70 Functional Specification was held in Lubbock on May 16, 1978. The specification was thoroughly overviewed, and was received without major comment. Two areas were indicated as requiring redefinition:

- O The disk controller and drives must be redefined for the ADD drive. At present, the double density, single sided mini floppy controller and drive are specified.

- O The power supply specification will be rewritten in light of the current power supply purchase part specification.

The enclosures detail all major and minor exceptions to the specification and the action items required to obtain closure on the specification signoff. An ACTION ITEM REPORT summarized needed activity.

Due to the extent of the updates required, due to the inclusion of the ADD controller specification, the formal signoff must be slipped to 6/30. All other updates will be required to be included by 5/30.

Donald V Mill

Don Mills

de Attachment

# STRICTLY PRIVATE

RECEIVED MAY 2 <u>4</u> 1978 GARY SLAGEL

#### DESIGN REVIEW

#### FUNCTIONAL DESCRIPTION

The "SR-70 Functional Specifications" is a hardware design specification and is not a concise functional description of the system. A user oriented functional description of approximately 10 pages is required which outlines the hardware and software features of the SR-70.

# KEYBOARD - Section 3.7

- Exact operation of the repeat key must be added as paragraph 3.7.3.2.

- A technique for ease of service of the keyboard should be discovered and implemented and described.

- Inputs on key definitions from Jerry Wardrum are to be added to Table 3.7.2.5.

- The requirement for a keyboard lockout feature is to be added as paragraph 3.7.4. This feature inhibits the keyboard interrupt.

- The definition of n-key rollover for the SR-70 keyboard must be added to paragraph 3.7.2.4.

- The possibility of a color coded SYSTEM CLEAR key must be investigated to determine the impact on styling and human factors.

- The current plan of forcing the user to identify special function keys on a card which rests in front of the keyboard was identified as a potential problem area. Special "clear key" sets, color coded keys, or an overlay approach were suggested as alternatives.

- Paragraph 3.7.5 must be added to the specification which describes a general procedure for implementing non-US keyboards for the SR-70.

Each keyboard will, in all probability, require a separate keyboard encoder to take care of the differing key positions found on non-US keyboards.

#### MONITOR - Section 3.13

- Discussion indicated the necessity of specifying the level of adjustment and repair which will be made on monitors in incoming inspection. DSG, Austin, will be consulted. This information is to be added to the monitor purchase part specification, A 1018487.

- Roger Tilbury agreed to investigate the tradeoffs associated with selling the SR-70 into European markets with the monitor packaged/sold separately versus the monitor packged/sold integrally with the mainframe.

### MONITOR - Section 3.13 (cont.)

• Stav Prodromou suggested that Steve Indvik investigate the commonality between the DSG 770 monitor and the SR-70 monitor in an effort to determine if the same monitor can be utilized.

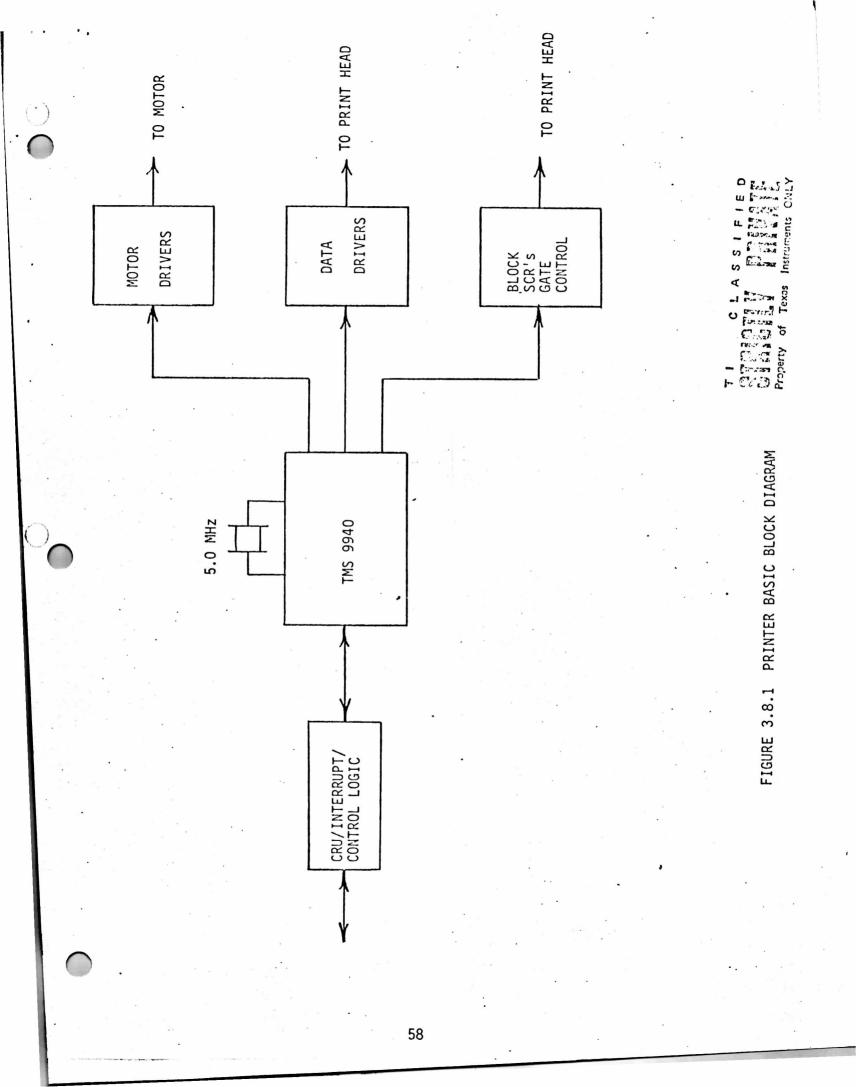

## PRINTER - Section 3.8

- Marketing requirement for the printer rate is 2.5 lines per second. This requirement must be weighted against its impact on both the controller and the power supply.

- The description of the EPN3116S printhead must be added to Section 3.8 and the specification added as Appendix M.

- Print quality requirements are to be obtained from Gary LaGrange and added to paragraph 6.6 as a part of the printer test plan.

- C.B. Wilson suggested that a programmable character genertor be added to the printer controller. This will be investigated when the controller is designed and hardware impact determined.

## MLB3 - Section 3.6.3

- The specification is to be expanded to include the number of screen updates/second.

- Discussion indicated that a DSR for the 733ASR terminal should be included in the DSR library.

### MLB4 - Section 3.6.4

• The specification will be expanded to include a checksum feature to be added to each program in BROM (TMC 0350) as well as an overall checksum for each TMC0350 device. This will facilitiate error detection during system startup as well as during operation. Overall checksum will also be added to each ROM (TMS 4732).

#### TESTABILITY - Section 6.0

- Time required for final burn-in of the SR-70 system is to be added to paragraph 6.9.

- General test requirements for each subsystem within the SR-70 are to be added to the applicable sections within Section 6.0.

#### POWER SUPPLY - Section 3.10

• This specification is currently being revised by Mike Anderson and Jerry Ogarek. This section will be updated per this revision.

# MLSB2 - Section 3.6.2

- The SR-70 will be featured with ADD instead of double density floppy disk drives. As a result, the disk drive must be rewritten to reflect the ADD controller.

- A meeting between the SR-70 design crew and the ADD personnel to identify and resolve system conflicts. These include environmental requirements, a motor speed lock control signal, and the power quality signal.

DISK DRIVES - Section 6.4

- Respecify in terms of the ADD drive. This section currently specifies the double density, single sided mini-floppy drive.

- Include in this section the specification of the ADD sector format.

CRU PORT - Paragraph 3.12.2

• A paragraph will be added to this section discussing the general characteristics of CRU based controllers which will be implemented on this port. This will serve as a general guideline for future development of external CRU controllers for the SR-70. A separate, detailed design guideline will be written by Mike Bunyard.

#### GENERAL MECHANICAL

- The environmental specification in Section 7.0 must be studied and enhanced. The stated specifications are currently in conflict with ADD and other subsystem environmental requirements. These conflicts must be resolved.

- Packaging and shipping requirements must be added to Section 7.0.

- It was indicated that the outboard (CRU, RS232C, monitor) connector schemes should be restudied in light of cable capturing techniques. The identified solutions must encompass provisions for the following:

- Stress relief on connectors at the PCB's and case.

- Cable restraints which allow forcible removal of the mating connector without damage to the PCB, case, or connector.

- Steve Indvik identified that MCB3 has a potential heat dissipation problem due to connector blockage of airflow out of the rear of the case. This must be identified in terms of the SR-70 airflow model to access the magnitude of the problem.

| N        |

|----------|

| · 6      |

|          |

| ្តីខ្មាះ |

| E        |

| HOZZERAM REDORT | PAGE ONE | TE        |

|-----------------|----------|-----------|

|                 | _        | STATUS DA |

|                 |          |           |

|                 |          |           |

|                 |          | MANAGER   |

|                 |          | PROGRAI   |

| 2<br>0<br>1     |          |           |

| 0               | Z        |           |

|                 | 0        |           |

| Q               | Р<br>О   | RAM       |

| PROGRAM                                      |                                                 |            |                      |

|----------------------------------------------|-------------------------------------------------|------------|----------------------|

| STAMP CLASSIFICATION AS REQUIRED             | FUNCTIONAL SPECIFICATION DONALD MILLS           | 5/18/78    |                      |

| PROBLEM                                      | ACTION                                          | ASSIGNMENT | COMPLETION<br>TARGET |

| AN SR-70 FUNCTIONAL DESCRIPTION IS REQUIRED. | AUTHOR THE SPECIFICATION                        | BUNYARD    | 6/30                 |

| KEYBOARD SPECIFICATION DEFICIENCIES          | DEFINE THE REPEAT KEY OPERATION                 | BUNYARD    | 5/30                 |

|                                              | STUDY THE SERVICEABILITY REQUIREMENTS           | FULGHUM    | 5/26                 |

|                                              | DEFINE THE SHALL BUSINESS SYSTEM SPECIAL KEYS   | WARDRUM    | 5/26                 |

|                                              | DEFINE KEYBOARD LOCKOUT                         | BUNYARD    | 5/30                 |

|                                              | COLOR CODED SYSTEM CLEAR KEY IMPACT             | BROWN      | 5/26                 |

|                                              | INVESTIGATE ALTERNATIVES TO THE CURRENTLY DE-   |            |                      |

|                                              | FINED SPECIAL FUNCTION CARD                     | BROWN      | 6/30                 |

|                                              | DEFINE THE IMPLEMENTATION SCHEME FOR NON-US     |            |                      |

|                                              | KEYBOARDS                                       | BUNYARD    | 5/30                 |

|                                              |                                                 |            | :                    |

| MONITOR SPECIFICATION DEFICIENCIES           | SPECIFY INCOMING INSPECTION REPAIR/ADJUSTMENT   | INDVIK/    | 6/30                 |

|                                              | IN PURCHASE SPEC                                | INCOMING   |                      |

| 1                                            | TRADE OFF STUDY ON SEPARATELY PACKAGED MONITOR/ |            |                      |

|                                              | MAINFRAME IN EUROPE                             | TILBURY    | 8/30                 |

|                                              | INVESTIGATE 770/SR-70 MONITOR COMPATIBILITY     | INDVIK     | 5/30                 |

|                                              |                                                 | •          | •                    |

| PRINTER DESCRIPTION DEFICIENCIES             | INVESTIGATE H/W IMPACT OF 2.5 LINE/SEC PRINTER  | OGAREK/    | 5/30                 |

|                                              |                                                 | ANDERSON/  |                      |

|                                              |                                                 | BUNYARD    |                      |

|                                              | ADD EPN3116S DESCRIPTION TO SPEC.               | BUNYARD    | 5/30                 |

|                                              | ADD PRINT QUALITY REQUIREMENTS                  | BUNYARD/   | 5/30                 |

|                                              |                                                 | LAGRANGE   |                      |

|                                              | INVESTIGATE PROGRAMMABLE CHARACTER GENERATOR    |            |                      |

|                                              | FOR PRINTER                                     | BUNYARD    | 6/30                 |

| TI-21362                                     |                                                 |            |                      |

| PROGR                                   |                                                                                                                              |       | STATUS DATE                   | •                    |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|----------------------|

| STAMP CLASSIFICATION AS REQUIRED        | 70 FUNCTIONAL SPECIFICATION DONALD MILLS                                                                                     | S     | 5/18/78                       | •.                   |

| PROBLEM                                 | ACTION                                                                                                                       |       | ASSIGNMENT                    | COMPLETION<br>TARGET |

| MLB3 DESCRIPTION DEFICIENCIES           | SPECIFY SCREEN UPDATES/SEC<br>INCLUDE 733ASR DSR IN S/W                                                                      | AC BL | BUNYARD<br>ACKER              | 5/30<br>3078         |

| MLB4 DESCRIPTION DEFICIENCIES           | ADD CHECKSUM FEATURE TO SPECIFICATION FOR<br>ROM (TMS 4732), BROM(TMC 0350)                                                  |       | BUNYARD/<br>ACKER/<br>WARDRUM | 5/30                 |

| TESTABILITY DESCRIPTION DEFICIENCIES    | ADD SYSTEM BURN-IN TIME TO SPEC.<br>INCLUDE GENERAL TEST REQUIREMENTS FOR EACH                                               |       | BUNYARD                       | 5/30                 |

|                                         | EACH SUBSYSTEM REQUIREMENT IS DETERMINED)                                                                                    |       | STAFF                         | 8/30                 |

| POWER SUPPLY SPECIFICATION DEFICIENCIES | UPDATE SPEC                                                                                                                  | A     | ANDERSON/                     | 5/30                 |

| MLB2 SPECIFICATION DEFICIENCIES         | ELIMINATE THE FLOPPY DISK DRIVE CONTROLLER<br>DESCRIPTION AND REPLACE THE DESCRIPTION WITH<br>THE ADD CONTROLLER DESCRIPTION |       | BUNYARD/<br>FULGHUM           | 6/30                 |

| DISK DRIVE SPECIFICATION DEFICIENCIES   | REPLACE THE FLOPPY DRIVE SPECIFICATION WITH<br>THE ADD DRIVE SPECIFICATION                                                   |       | BUNYARD                       | 5/30                 |

| CRU PORT SPECIFICATION DEFICIENCIES     | ADD GUIDELINE FOR EXTERNAL CRU MODULE DESIGN<br>TO SPEC                                                                      |       | BUNYARD                       | 5/30                 |

|                                         |                                                                                                                              |       |                               |                      |

| PRIVATE  | , |

|----------|---|

| STRICTLY |   |

.....

| THREE       |           |

|-------------|-----------|

| PAGE 1      |           |

|             | ATUS DATE |

|             | N T C     |

|             | 15        |

| 0           |           |

| R E P O R T |           |

|             |           |

| œ           | AGER      |

|             | AMA       |

| W           | OGRAM MI  |

| LAA         | đ         |

|             |           |

|             |           |

|             |           |

|             |           |

| 0           |           |

|             |           |

| C<br>T<br>T |           |

| U           | X         |

3 S. W.

| TAUDE CLASEFICATION AS REQUERS     SR-70 FUNCTIONAL SPECIFICATION     DONALD MILLS     5/18/78       RPOOLEN     RPADLEN     ASTOCATION     ASTOCATION     ASTOCATION       GEMERAL MECHANICAL SPECIFICATION DEFICIENCIES     ENHANCE EWIRONHENTAL SPEC     LAGRANGE       ADD PACKGEING/SHIPPING     REQUIRENENTS     LAGRANGE       STUDY OUTBOARD CONNECTOR SCHEHE IN TEMIS OF     BROAN       STUDY OUTBOARD CONNECTOR CAPTURE     BROAN |                                  |                                                      |                                   |            | •                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------|-----------------------------------|------------|----------------------|

| PROBLEM     ACTION       MECHANICAL SPECIFICATION DEFICIENCIES     ENHANCE ENVIRONMENTAL SPEC       ADD PACKAGING/SHIPPING REQUIREMENTS     LL       STUDY OUTBOARD CONNECTOR SCHEME IN TERMS OF     BI       REVIEM MLB3 HEAT DISSIPATION     BI                                                                                                                                                                                            | STAMP CLASSIFICATION AS REQUIRED | FUNCTIONAL                                           | DONALD MILLS                      | 5/18/78    |                      |

| MECHANICAL SPECIFICATION DEFICIENCIES ENHANCE ENVIRONMENTAL SPEC<br>ADD PACKAGING/SHIPPING REQUIREMENTS<br>STUDY OUTBOARD CONNECTOR CAPTURE<br>STRESS RELIEF AND CONNECTOR CAPTURE<br>REVIEW MLB3 HEAT DISSIPATION                                                                                                                                                                                                                           | PROBLEM                          | ACTIO                                                | N                                 | ASSIGNMENT | COMPLETION<br>TARGET |

| ADD PACKAGING/SHIPPING REQUIREMENTS<br>STUDY OUTBOARD CONNECTOR SCHEME IN TERMS OF<br>STRESS RELIEF AND CONNECTOR CAPTURE<br>REVIEM MLB3 HEAT DISSIPATION                                                                                                                                                                                                                                                                                    | MECHANICAL SPECIFICATION         | ENHANCE                                              | EC                                | LAGRANGE   | 5/30                 |

| EME IN TERMS OF<br>CAPTURE                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  | ADD PACKAGING/SHIPPING R                             | EQUIREMENTS                       | LAGRANGE   | 5/30                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  | STUDY OUTBOARD CONNECTOR<br>STRESS RELIEF AND CONNEC | SCHEME IN TERMS OF<br>TOR CAPTURE | BROWN      | 6/30                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  | REVIEW MLB3 HEAT DISSIPA                             | TION                              | BROWN      | 6/30                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   | •          |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            | ,                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            | •                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   | 4          |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            | -                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                                      |                                   |            |                      |

TABLE OF CONTENTS

| -         |                                  |    |

|-----------|----------------------------------|----|

| 1.0       | Introduction .                   | 12 |

| 2.0       | Applicable Documents             | 12 |

| 2.1       | Symbol Definition                | 12 |

| 3.0       | Hardware Description             | 13 |

| 3.1       | SR-70 Memory Map                 | 13 |

| 3.1.1     | Detailed SR-70 Memory Map        | 15 |

| 3.2       | SR-70 System CRU Map             | 15 |

| 3.2.1     | Detailed SR-70 CRU Map           | 16 |

| 3.3       | Interrupt Definition             | 22 |

| 3.4       | System Characteristics           | 22 |

| 3.4.1     | System Clock                     | 22 |

| 3.4.2     | Power Up/Reset Sequence          | 23 |

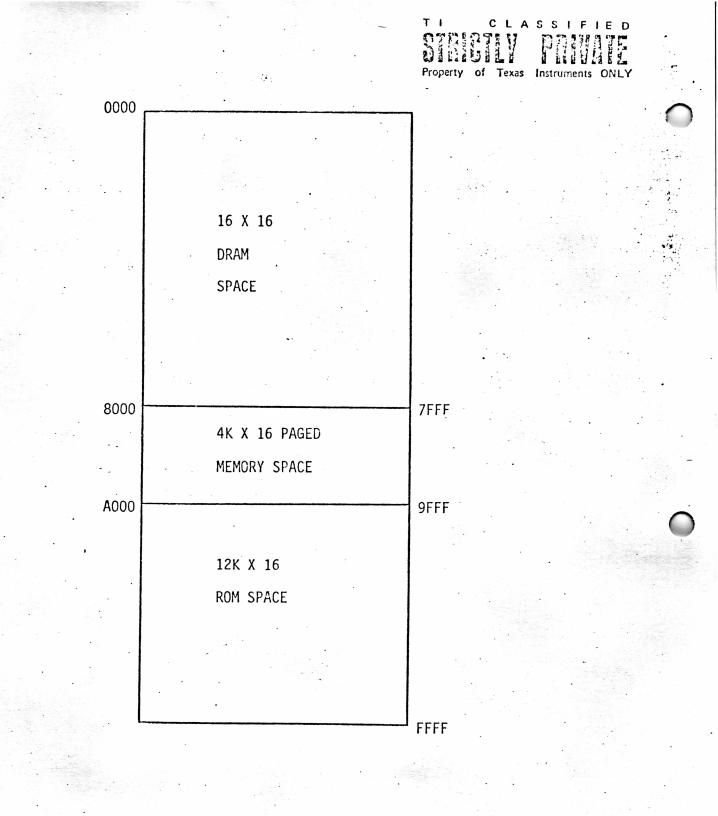

| 3.5       | System Block Diagram             | 23 |

| 3.6       | Mainframe                        | 26 |

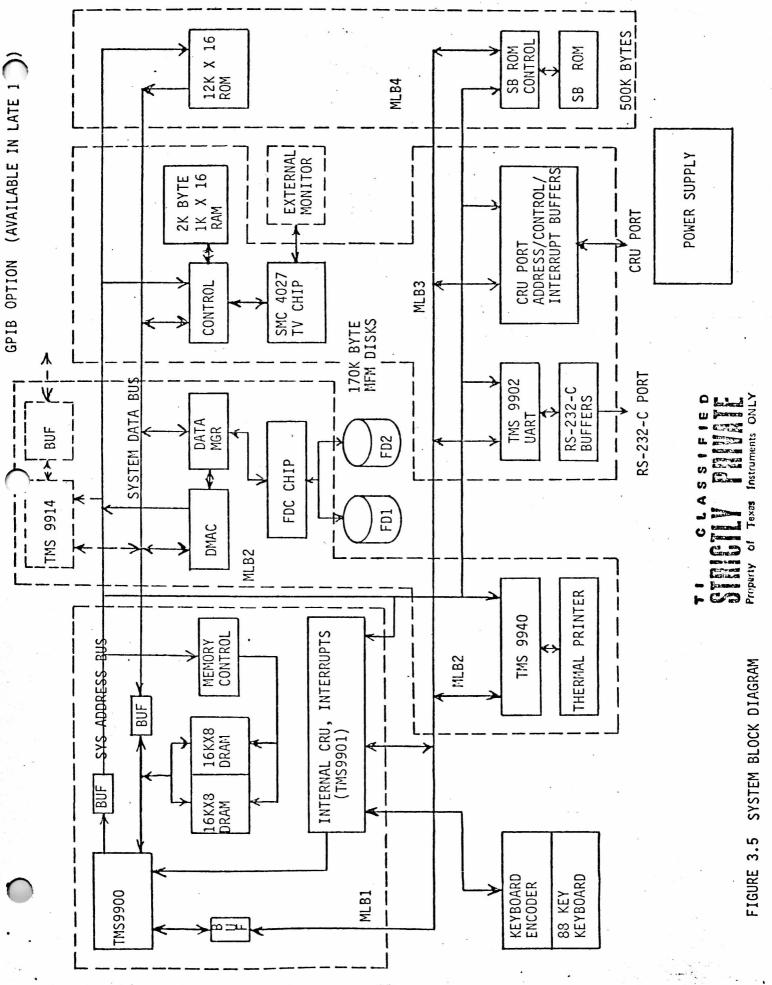

| 3.6.1     | MLB1                             | 26 |

| 3.6.1.1   | MLB1 Basic Block Diagram         | 26 |

| 3.6.1.2   | ML.B1 Functional Characteristics | 26 |

| 3.6.2     | MLB2                             | 30 |

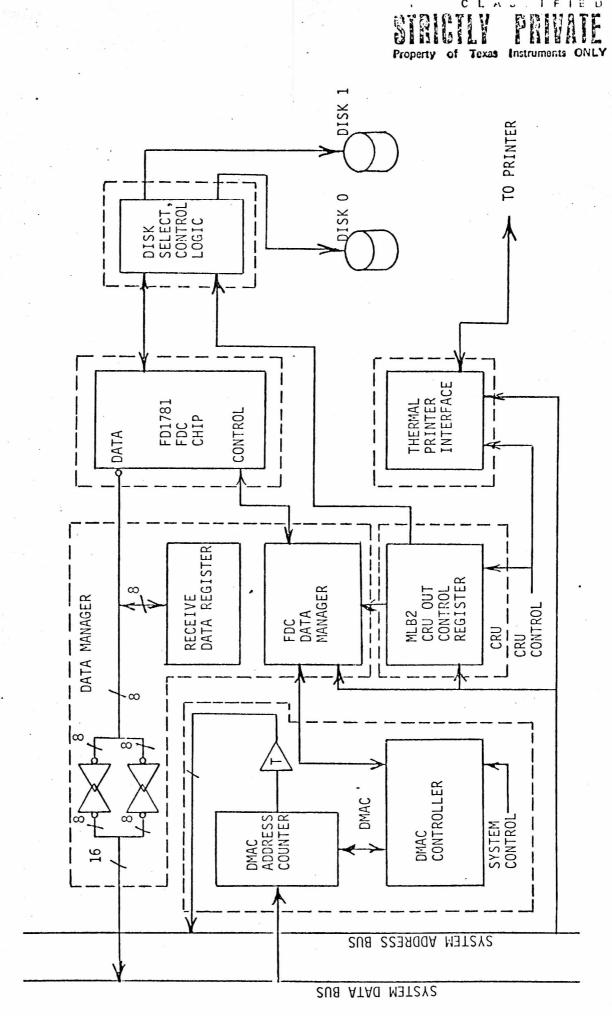

| 3.6.2.1   | MLB2 Basic Block Diagram         | 30 |

| 3.6.2.2   | MLB2 Functional Characteristics  | 30 |

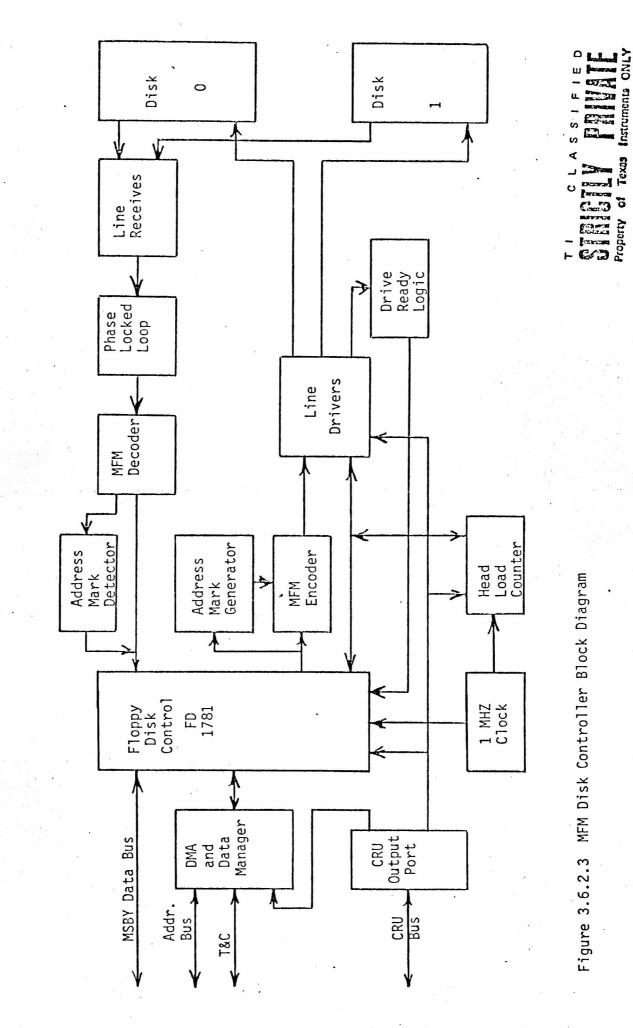

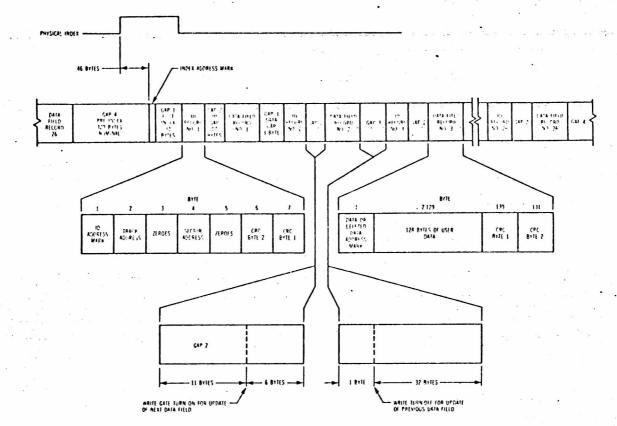

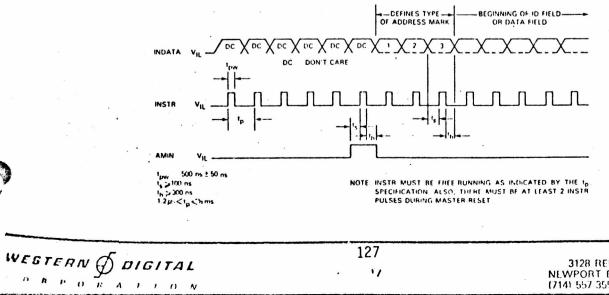

| 3.6.2.3   | Disk Hardware Description        | 34 |

| 3.6.2.3.1 | Controller Clocks                | 34 |

| 3.6.2.3.2 | Line Receivers                   | 34 |

| 3.6.2.3.3 | Line Drivers                     | 34 |

|            | 26224   | TABLE OF CONTENTS - CONT         |          |

|------------|---------|----------------------------------|----------|

| , <b>4</b> | -       | Write Channel<br>Read Channel    | 34<br>36 |

|            |         | Printer Interface Description    | 37       |

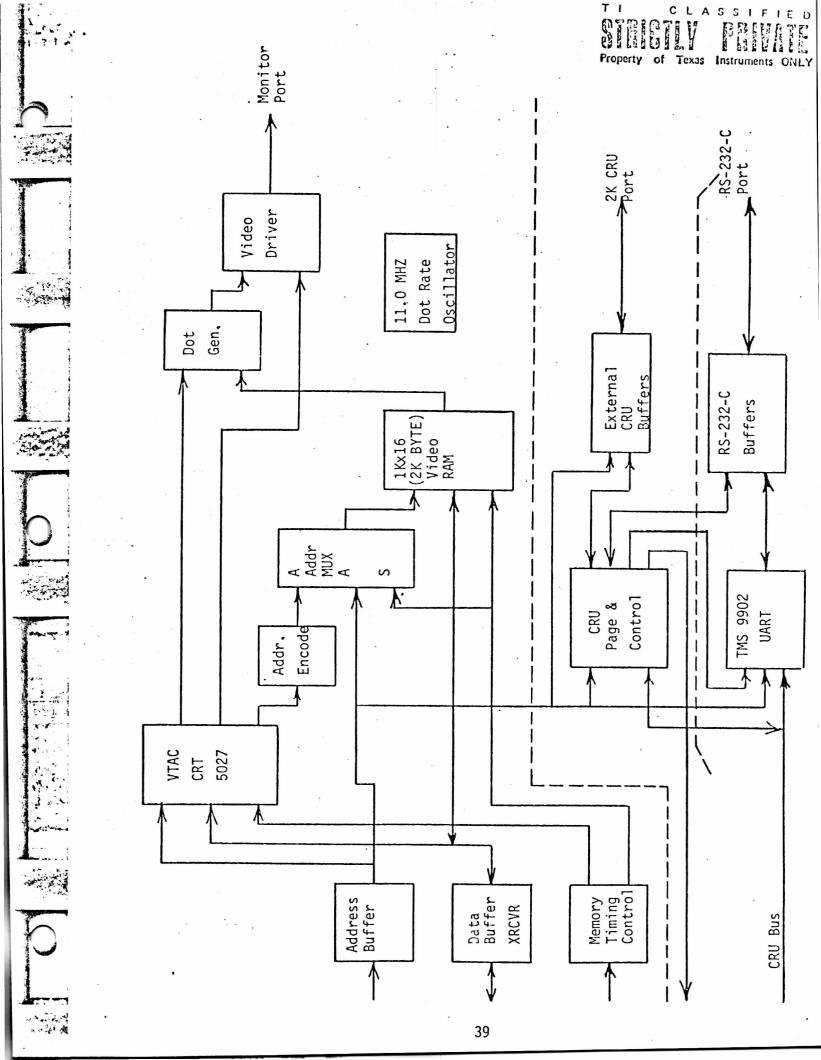

| Ô          | 3.6.3   | MLB3                             | 38       |

|            |         | MLB3 Basic Block Diagram         | 38       |

|            |         | MLB3 Functional Characteristics  | 38       |

|            |         | Video Characteristics            | 38       |

|            | 3.6.3.3 | CRU Characteristics              | 42       |

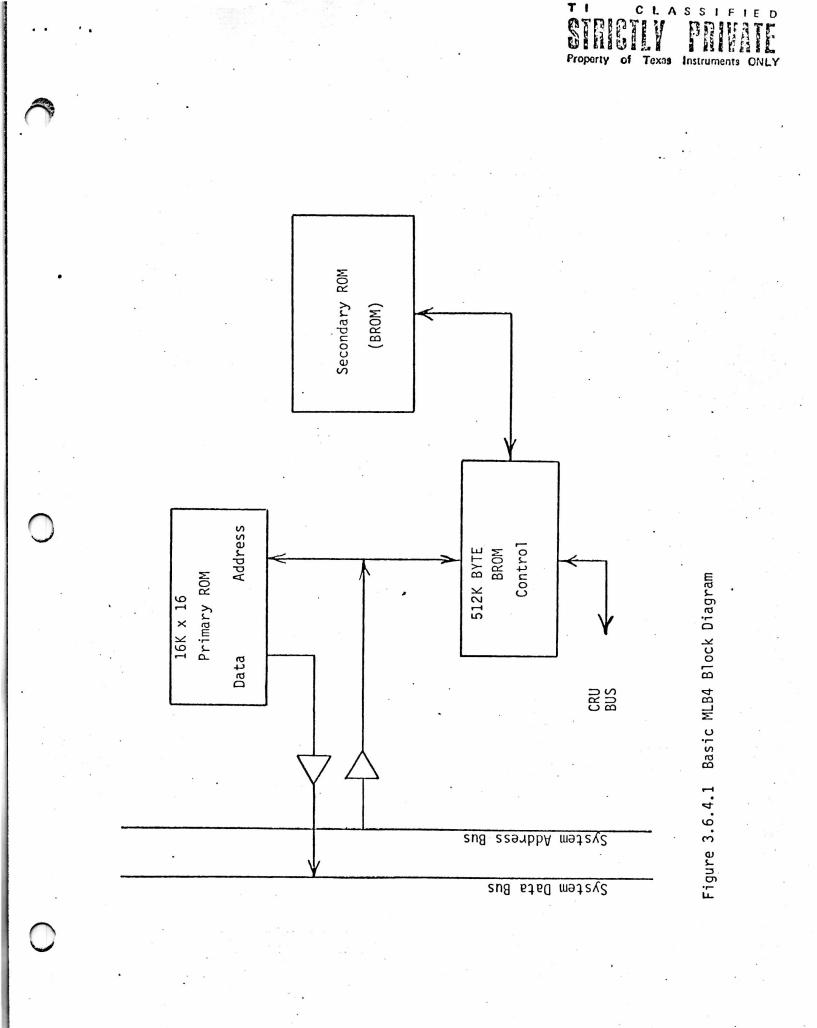

|            | 3.6.4   | MLB4                             | 44       |

|            | 3.6.4.1 | Basic MLB4 Block Diagram         | 44       |

|            | 3.6.4.2 | Primary ROM                      | 44       |

|            | 3.6.4.3 | Secondary ROM                    | 44       |

|            | 3.6.5   | Mainframe Interconnect           | 48       |

|            | 3.6.5.1 | System Interconnect PWB          | 48       |

|            | 3.6.5.2 | I/O Interconnect PWB             | 48       |

|            | 3.7     | Keyboard                         | 49       |

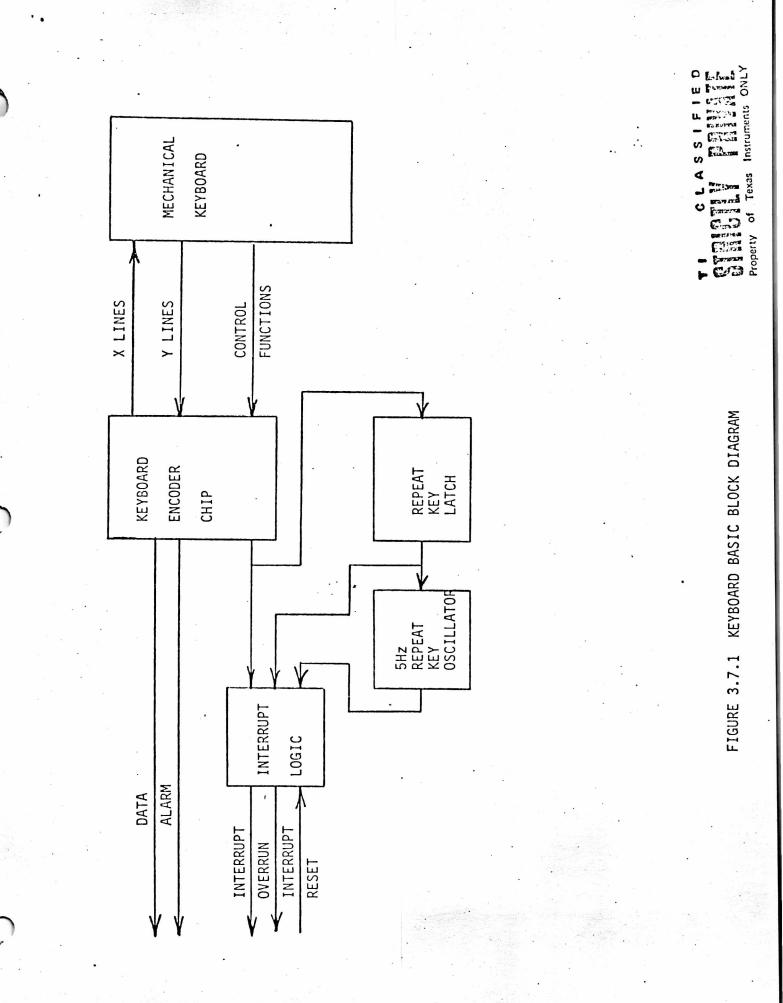

|            | 3.7.1   | Keyboard Basic Block Diagram     | 49       |

|            | 3.7.2   | Keyboard Encoder Characteristics | 49       |

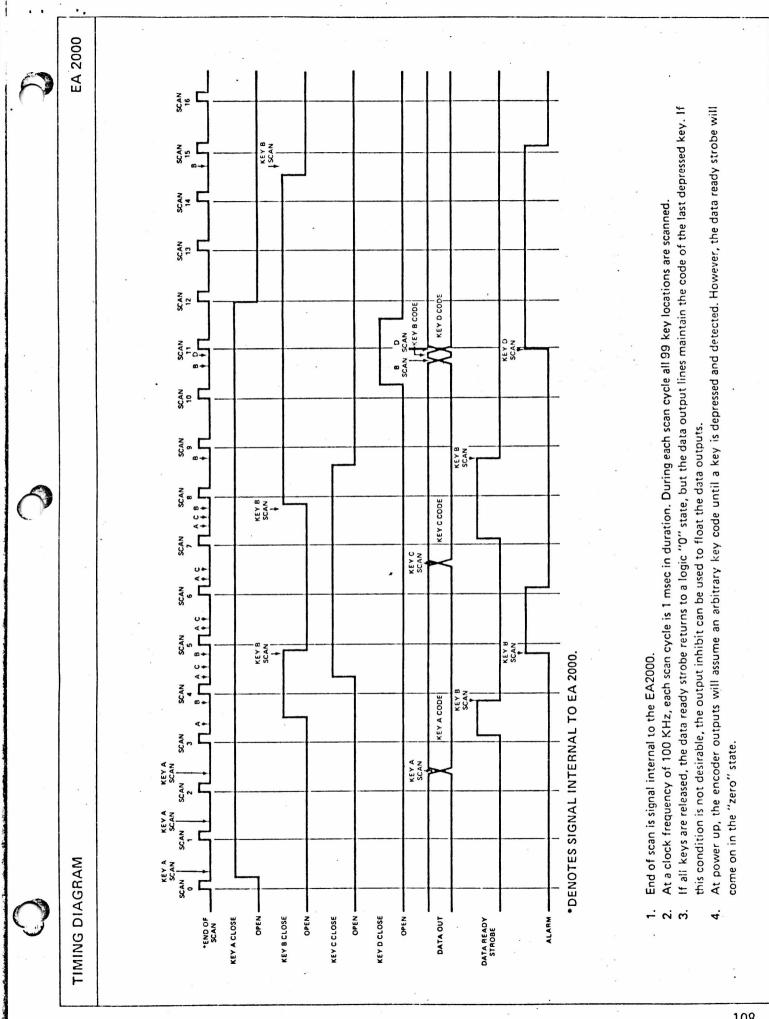

|            | 3.7.2.1 | Encoder X-Y Scan                 | 49       |

|            | 3.7.2.2 | Encoder Debounce                 | 49       |

|            | 3.7.2.3 | X-Y Phantom Key Detection        | 49       |

|            | 3.7.2.4 | Rollover                         | 49       |

|            | 3.7.2.5 | Encoding ROM                     | 49       |

|            | 3.7.2.6 | Output Data Latch                | 49       |

# TABLE OF CONTENTS - CONTINUED

| 3.7.3   | Repeat Key Characteristics         |      | 54 |

|---------|------------------------------------|------|----|

| 3.7.3.1 | Repeat Frequency                   | •    | 54 |

| 3.7.3.2 | Repeat Oscillator                  |      | 55 |

| 3.7.3.3 | Repeat Key Latch                   |      | 55 |

| 3.7.3.4 | Repeat Key Operation               |      | 55 |

| 3.7.4   | Data Overrun                       |      | 55 |

| 3.7.5   | Keyboard DSR Characteristics       |      | 55 |

| 3.8     | Thermal Printer                    |      | 57 |

| 3.8.1   | Printer Basic Block Diagram        |      | 57 |

| 3.8.2   | Printer Functional Characteristics | 3    | 57 |

| 3.8.3   | Printer Module TMS 9940 Diagnostic | S    | 60 |

| 3.8.4   | Thermal Printer Paper              |      | 60 |

| 3.8.5   | Print Head                         |      | 60 |

| 3.8.6   | Font                               |      | 60 |

| 3.9     | Disk Drive Characteristics         |      | 60 |

| 3.9.1   | Basic Mini Floppy Disk Characteris | tics | 60 |

| 3.9.1.1 | Number of Tracks                   |      | 60 |

| 3.9.1.2 | Sector Type                        |      | 60 |

| 3.9.1.3 | Sector Size                        |      | 60 |

| 3.9.1.4 | Transfer Rate                      |      | 60 |

| 3.9.1.5 | Average Access Time                |      | 60 |

| 3.9.1.6 | Track Life                         |      | 60 |

| 3.9.1.7 | Disk Spin Speed                    |      | 60 |

| 3.9.1.8 | Diskette Cartridge Size            |      | 60 |

4

T CLASSIFIED Property of Texas Instruments ONLY TABLE OF CONTENTS - CONTINUED

| 0           | 3.9.1.9   | Power Requirements                  | 61              |

|-------------|-----------|-------------------------------------|-----------------|

|             | 3.9.2     | Omitted                             |                 |

| •<br>•<br>• | 3.9.3     | Omitted                             |                 |

|             | 3.9.4     | Disk DSR Characteristics            | 62              |

|             | 3.9.5     | Floppy Disk Format                  | 74              |

|             | 3.10      | Power Supply                        | 75              |

|             | 3.10.1    | Input                               | 75              |

|             | 3.10.1.1  | United States (Model 1)             | <sup>-</sup> 75 |

|             | 3.10.1.2  | Foreign, Model 2                    | 75              |

|             | 3.10.1.3  | Foreign, Model 3                    | 75              |

|             | 3.10.2    | Output                              | 75              |

|             | 3.10.3    | Ripple and Spikes                   | 75              |

| ~           | 3.10.4    | Load Regulation                     | 76              |

| Q           | 3.10.5    | Temperature Rating                  | 76              |

|             | 3.10.6    | Storage Temperature                 | 76              |

|             | 3.10.7    | Temperature Coefficients of Outputs | 76              |

|             | 3.10.8    | Humidity                            | 76              |

|             | 3.10.9    | Altitude                            | 76              |

|             | 3.10.10   | AC Inrush Current                   | 76              |

|             | 3.10.11   | Efficiency                          | 76              |

|             | 3.10.12   | Switching Frequency                 | 76              |

|             | 3.10.13   | Hold-up                             | 76              |

|             | 3.10.14   | Power Sequencing                    | 78              |

|             | 3.10.15   | Protection                          | 78              |

|             | 3.10.15.1 | Over-voltage Protection             | 78              |

| $\cap$      | 3.10.16   | EMI-RFI                             | 78              |

| U           |           |                                     |                 |

ΤI

ei C

CLASSIFI

VP

1 Property of Texas Instruments ONLY

3

ΕD

|            | 3.10.17   | Isolation                                   | 78         |

|------------|-----------|---------------------------------------------|------------|

| 8          | 3.10.17.1 | United States (Model 1)                     | 78         |

| $\bigcirc$ | 3.10.17.2 | Foreign, Model 2                            | 78         |

|            | 3.10.17.3 | Foreign, Model 3                            | 78         |

|            | 3.10.18   | Testability                                 | 78         |

|            | 3.10.19   | Power Stable Output                         | 78         |

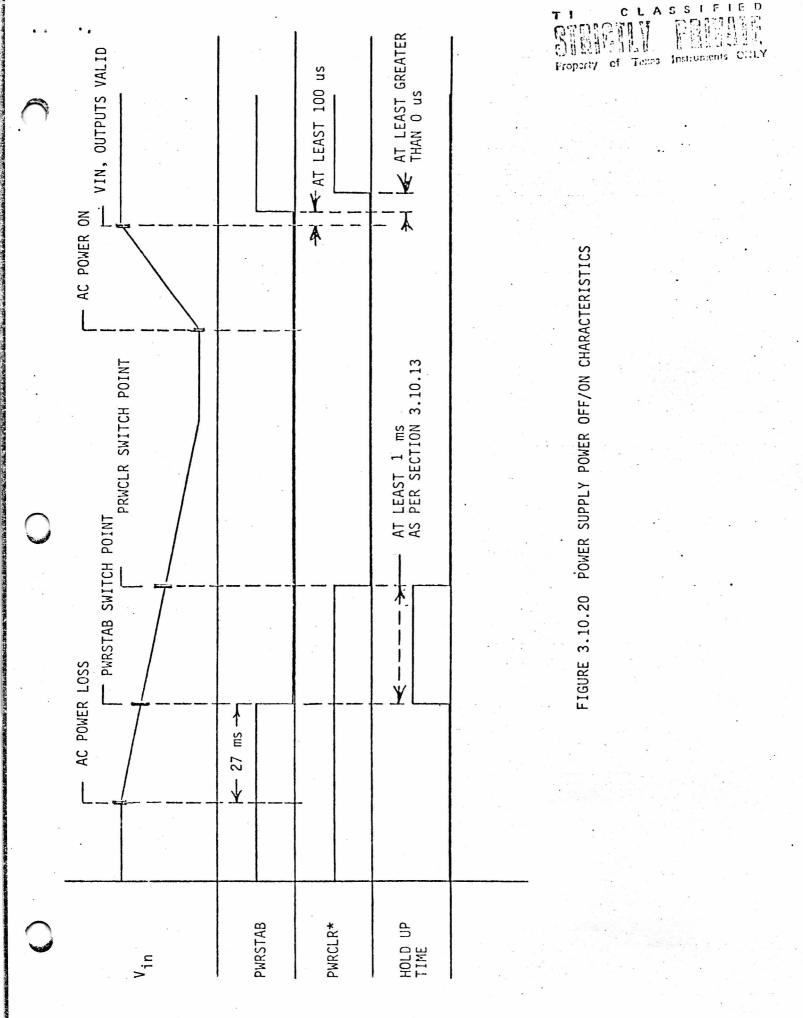

|            | 3.10.20   | Power On Clear                              | 79         |

|            | 3.10.21   | Mean Time Between Failure                   | 79         |

|            | 3.10.22   | PWB Marking                                 | 79         |

| . '        | 3.10.23   | Weight                                      | 79         |

| • '.       | 3.10.24   | Construction                                | <u>7</u> 9 |

|            | 3.10.25   | Certification as Office Equipment           | 79         |

|            | 3.10.25.1 | United States (Model 1)                     | 79         |

|            | 3.10.25.2 | Foreign, Model 2                            | 79         |

| $\cap$     | 3.10.25.3 | Foreign, Model 3                            | 79         |

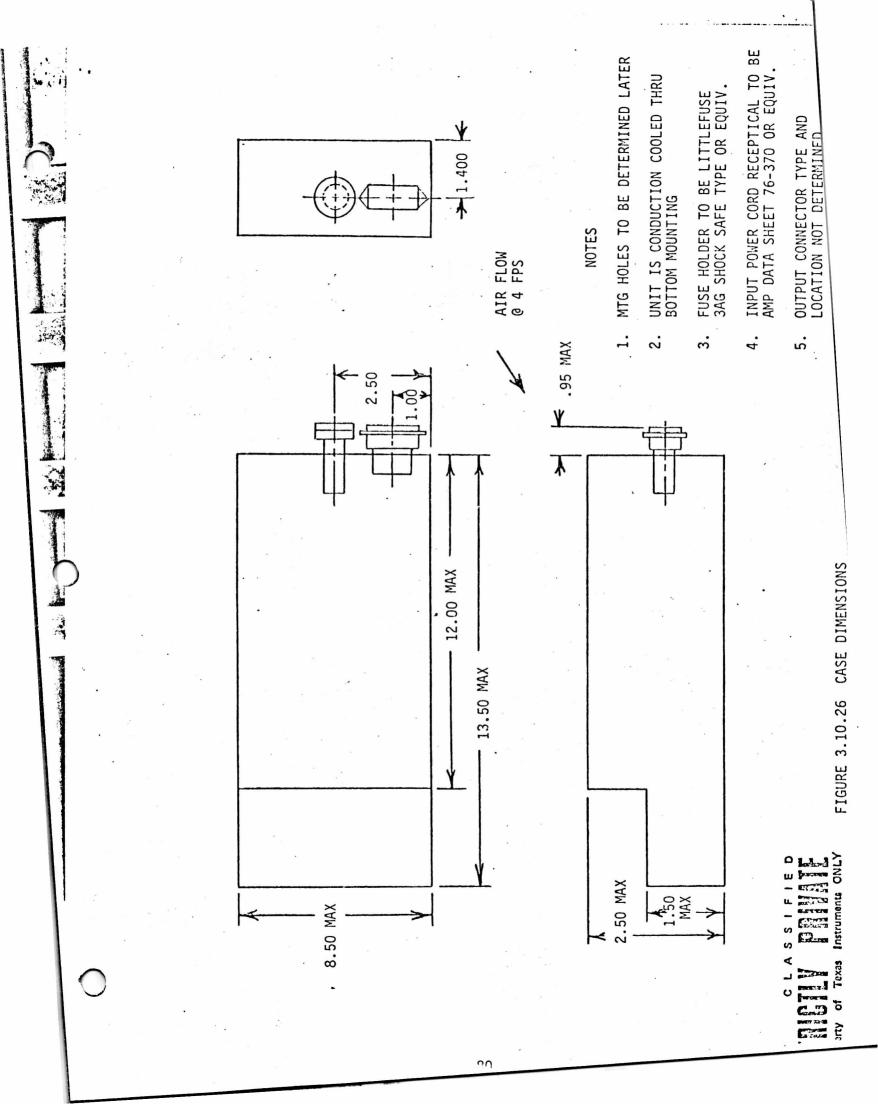

| $\cup$     | 3.10.26   | Dimensions                                  | 79         |

|            | 3.10.27   | Environmental Testing                       | 79         |

|            | 3.10.27.1 | Vibration in Shipping Container             | 81         |

|            | 3.10.27.2 | Bounce, Loose Cargo - In Shipping Container | 81         |

|            | 3.10.27.3 | Transient Drop Test - In Shipping Container | 81         |

|            | 3.10.27.4 | Mechanical Shock - Bench Handling           | 81         |

|            | 3.11      | Internal Connection Plan                    | 82         |

|            | 3.11.1    | Mechanical Concept                          | 82         |

|            | 3.11.2    | Connector Pin Definitions                   | 82         |

|            | 3.11.2.1  | Keyboard                                    | 82         |

|            | 3.11.2.2  | Thermal Printer                             | 82         |

C

6.

CL

TRICTLY

Α S S

WENE OF Texas Instruments ONLY

FIED

1

Т

# TABLE OF CONTENTS - CONTINUED

| $\bigcirc$    | 3.11.2.3 | Power Supply                       | 82   |

|---------------|----------|------------------------------------|------|

|               | 3.11.2.4 | Mini Floppy Disks                  | 82   |

|               | 3.11.3   | Power Distribution                 | 82   |

|               | 3.12     | Outside World Interface            | 83   |

|               | 3.12.1   | RS-232-C Port Definition           | 83   |

| . '           | 3.12.2   | CRU Port Definition                | 83   |

|               | 3.12.3   | Monitor Port Definition            | 83   |

|               | 3.12.4   | GPIB Interface Option              | 87   |

|               | 3.12.5   | AC Power                           | 87   |

|               | 3.13     | Monitor Characteristics            | 88   |

|               | 4.0      | System Level Diagnostics           | 89   |

| • •<br>•<br>• | 4.1      | User Oriented Diagnostics          | 89   |

| -             | 4.2      | Power-Up Diagnostics               | 89   |

| O             | 4.3      | Maintenance Diagnostics            | . 90 |

|               | 4.4      | Diagnostic Functional Requirements | 90   |

|               | 4.4.1    | Level 1 Diagnostics                | 90   |

|               | 4.4.2    | Level 2 Diagnostics                | 90   |

|               | 4.4.3    | Level 3 Diagnostics                | 90   |

|               | 4.4.3.1  | All Subsystems                     | 90   |

|               | 4.4.3.2  | CPU                                | 90   |

|               | 4.4.3.3  | Memory                             | 90   |

|               | 4.4.3.4  | Thermal Printer                    | 90   |

|               | 4.4.3.5  | Monitor                            | 91   |

|               | 4.4.3.6  | Keyboard                           | 92   |

TI CLASSIFIED Property of Texas Instruments ONLY

# TABLE OF CONTENTS - CONTINUED

| 4.4.3.7  | RS-232-C Port                        | 91 |

|----------|--------------------------------------|----|

| 4.4.3.8  | CRU Port                             | 91 |

| 4.4.3.9  | Outboard Devices                     | 91 |

| 4.4.3.10 | Disks                                | 91 |

| 5.0      | Software Characteristics             | 92 |

| 6.0      | Electrical Test Plan                 | 93 |

| 6.1      | Component Level Testing              | 93 |

| 6.2      | PWB Testing                          | 93 |

| 6.3      | Power Supply                         | 93 |

| 6.4      | Disk Drives                          | 93 |

| 6.5      | Keyboard                             | 93 |

| 6.6      | Thermal Printer                      | 93 |

| 6.7      | Internal Peripheral/Mainframe Cables | 93 |

| 6.8      | Monitor                              | 95 |

| 6.9      | System Level (Burn In Also)          | 96 |

| 7.0      | Environmental                        | 97 |

| 7.1      | Temperature                          | 97 |

| 7.2      | Humidity                             | 97 |

| 7.3      | Shock                                | 97 |

| 7.4      | Vibration                            | 97 |

| 7.5      | Safety                               | 97 |

| 7.6      | Noise                                | 97 |

| 8.0      | Reliability                          | 98 |

| 9.0      | Maintainability                      | 98 |

|          |                                      |    |

TI CLASSIFIED STRICTLY PRIMARY Property of Texas Instruments ONLY

Property of Texas Instruments ONLY

CLASS

D

ΤI

6

# TABLE OF CONTENTS - CONTINUED

| Appendix A | TMS 9900 Data Book               | Omitted |

|------------|----------------------------------|---------|

| Appendix B | TMS 9901 Data Book               | Omitted |

| Appendix C | TMS 9902 Data Book               | Omitted |

| Appendix D | System Backplane Pin Definition  | 99      |

| Appendix E | I/O Backplane Pin Definition     | 101     |

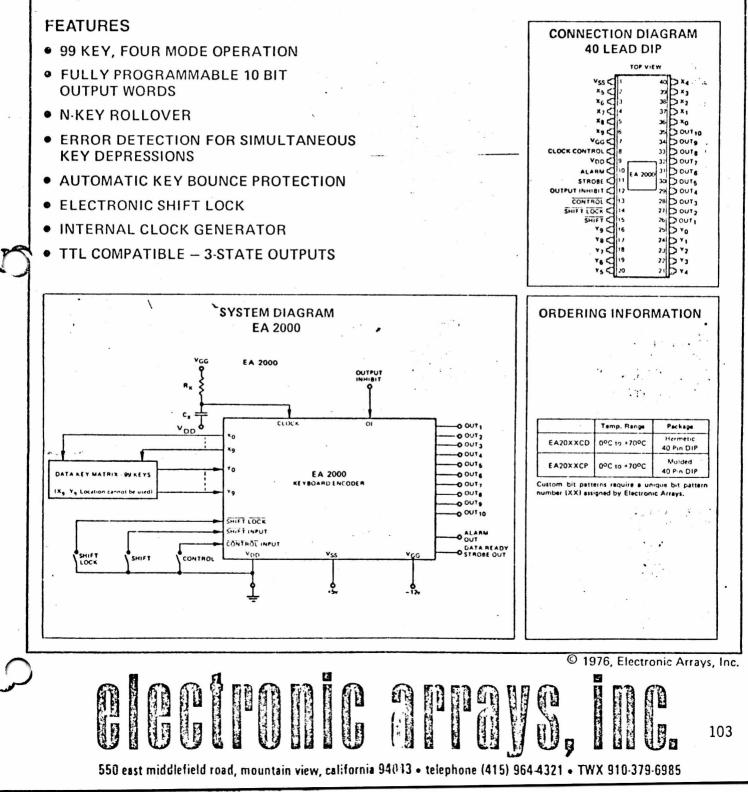

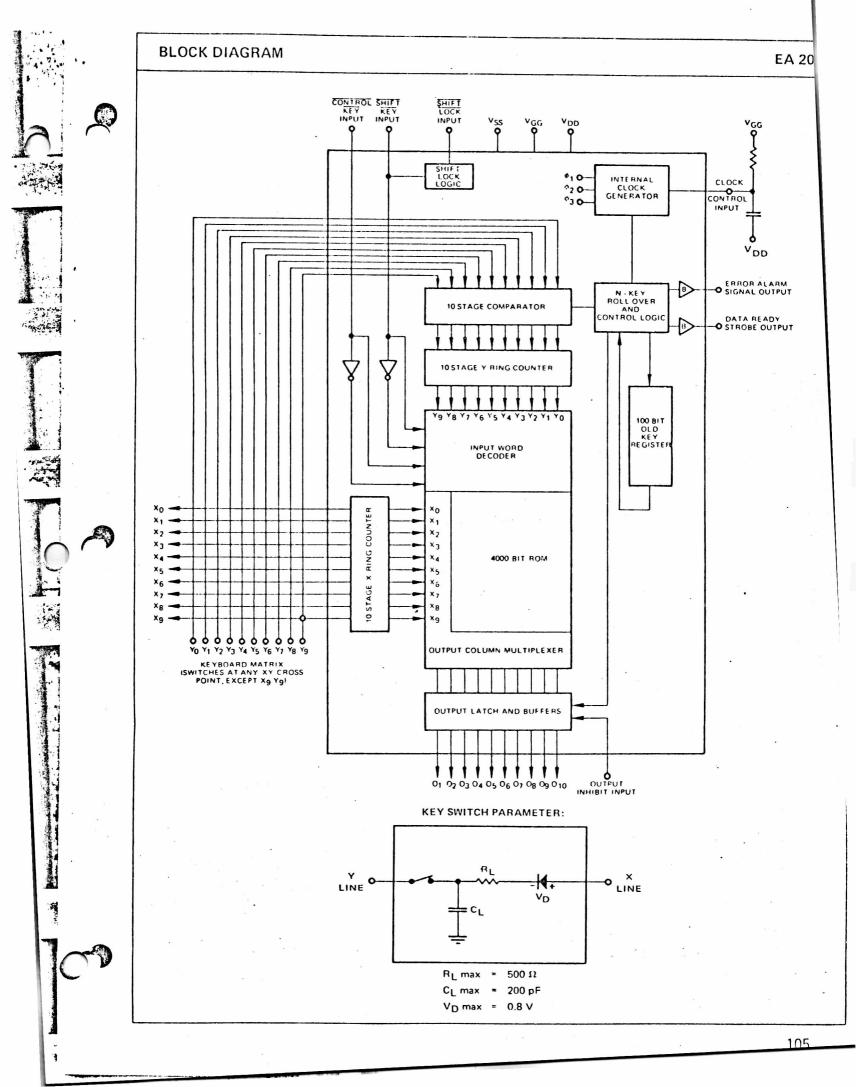

| Appendix F | EA 2000 Keyboard Encoder         | 103     |

| Appendix G | Omitted                          | -       |

| Appendix H | Western Digital 1781 Data Sheets | 111     |

| Appendix J | SMC CRT5027 VTAC Data Sheet      | 131     |

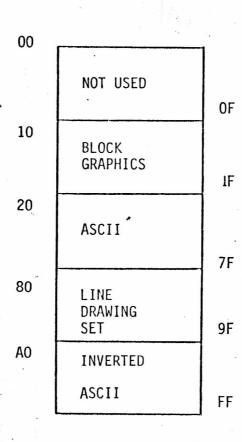

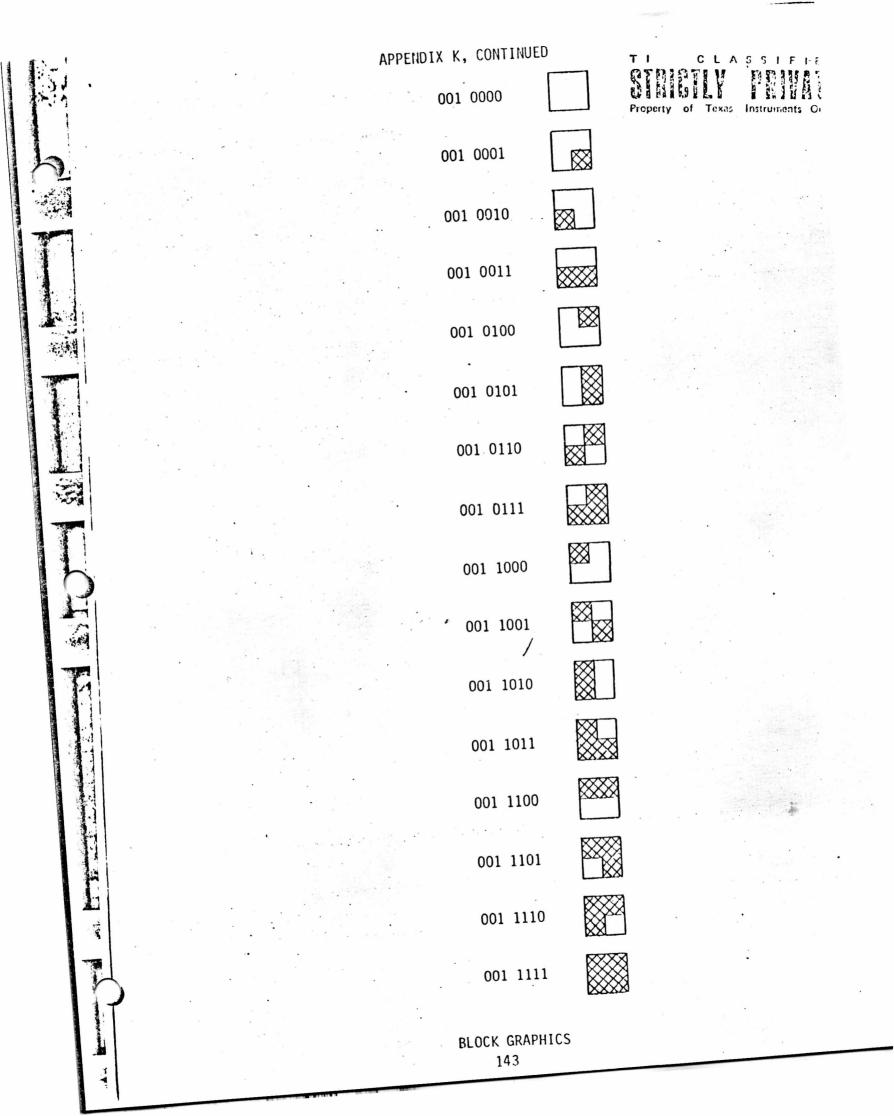

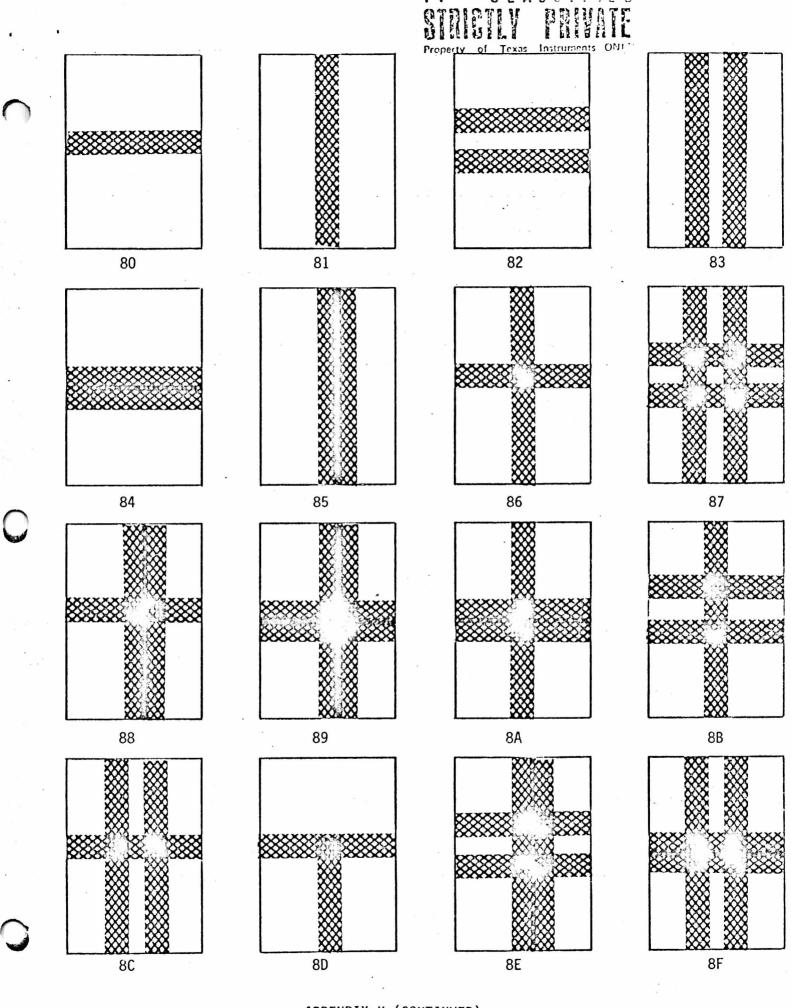

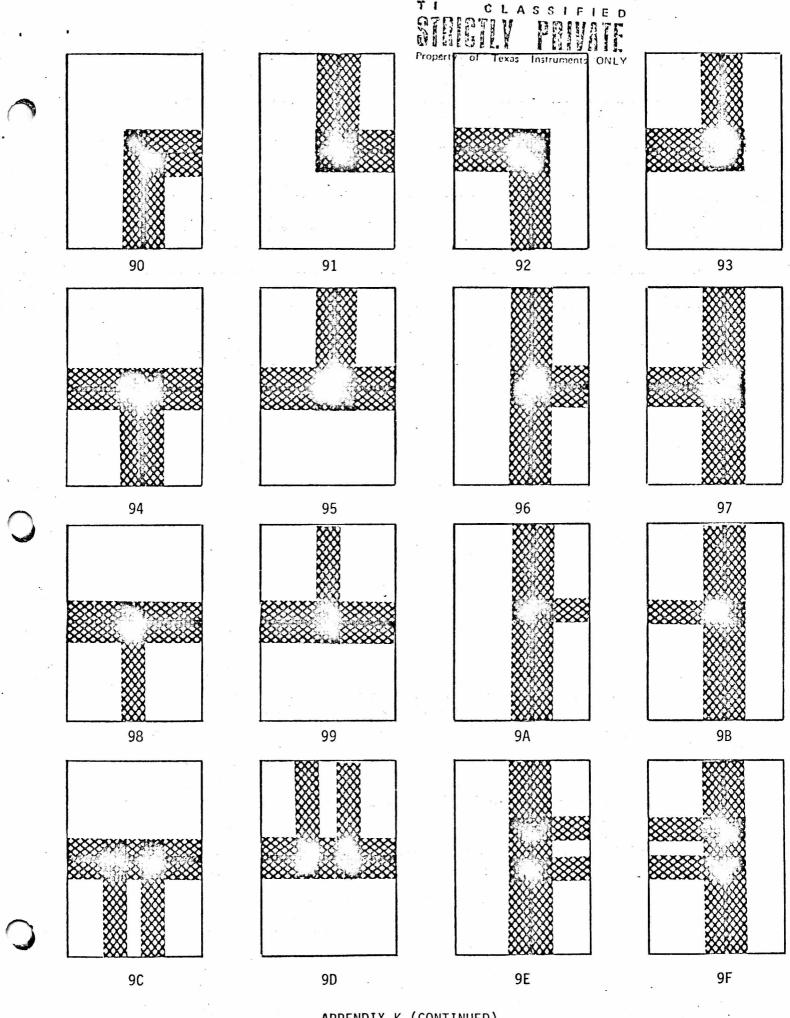

| Appendix K | Video ASCII Code Definitions     | 139     |

| Appendix L | TMC 0350 specification           | 147     |

TI CLASSIFIE TI CLASSIFIE Property of Texas Instruments ONL

| LIST | OF | FI | GL | JRES |

|------|----|----|----|------|

|------|----|----|----|------|

|            | •             |                                                     |            |

|------------|---------------|-----------------------------------------------------|------------|

| 0          | FIGURE<br>3.1 | SR-70 Memory Map                                    | PAGE<br>14 |

|            | 3.4.2         | Basic CPU LOAD-ON-RESET Timing                      | 24         |

|            | 3.5           | System Block Diagram                                | 25         |

|            | 3.6.1         | MLB1 Block Diagram                                  | 27         |

|            | 3.6.1.2       | DRAM Early Write Timing                             | 28         |

|            | 3.6.2         | MLB2 Basic Block Diagram                            | 31         |

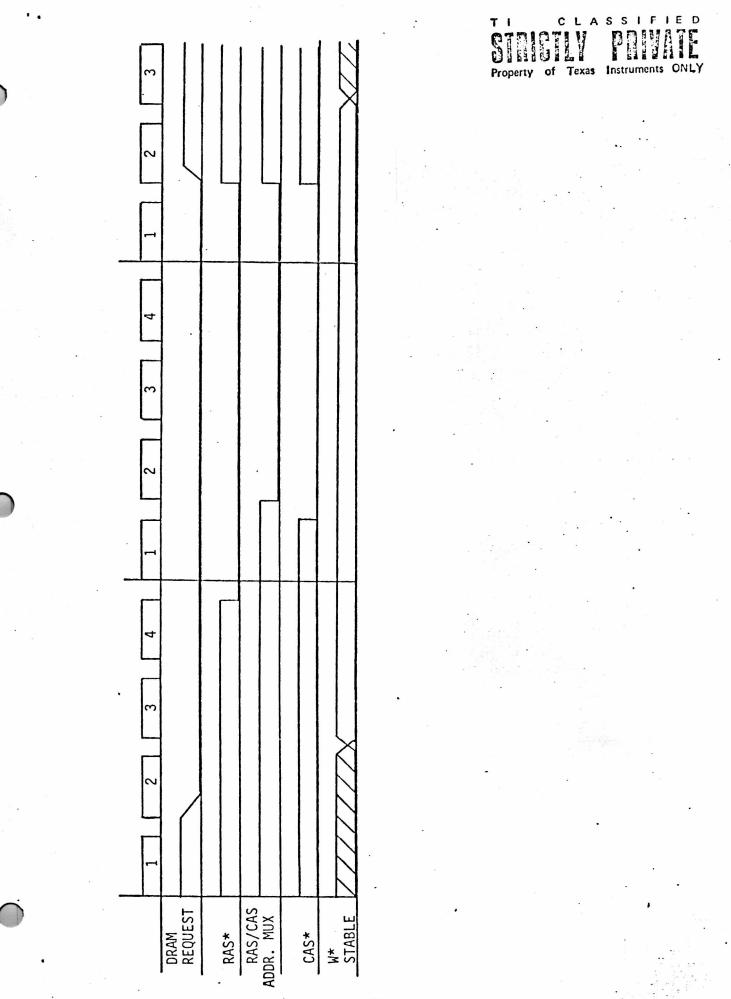

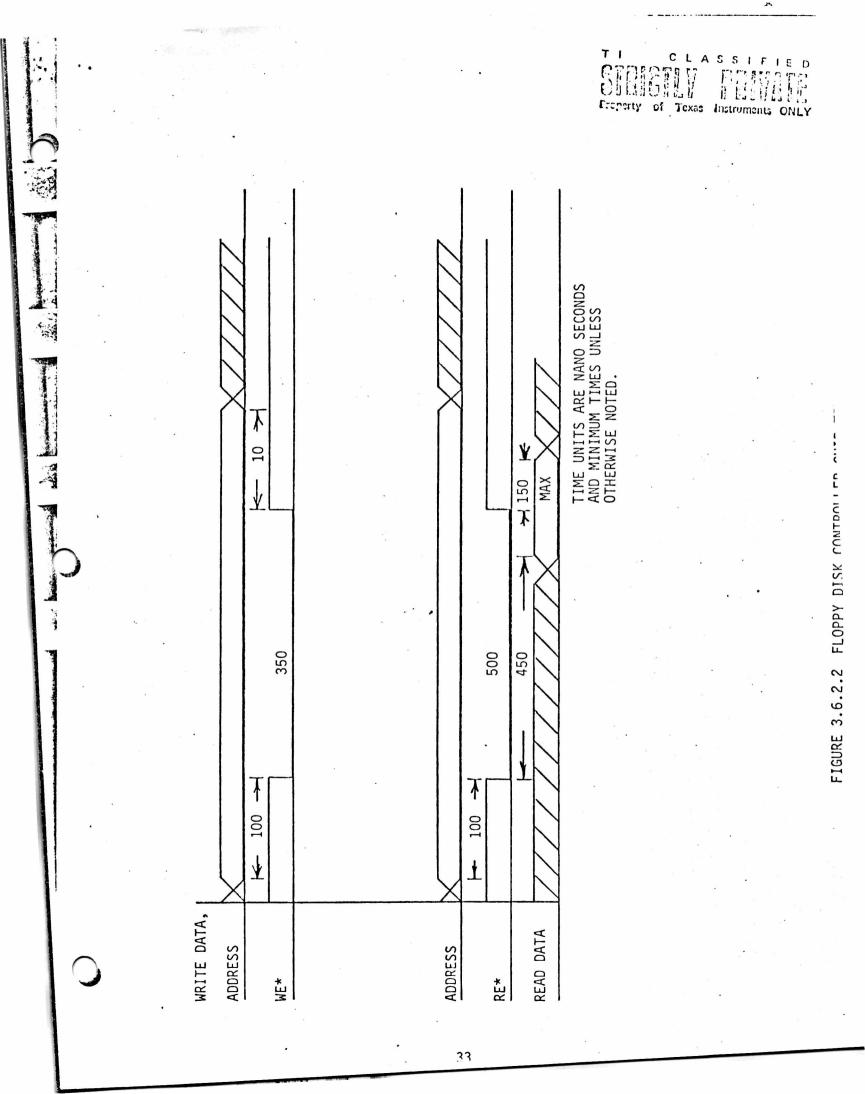

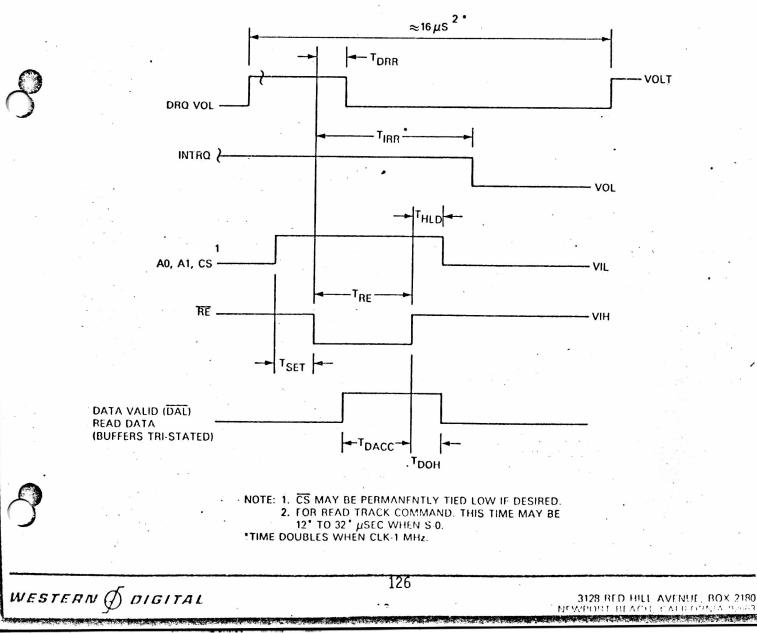

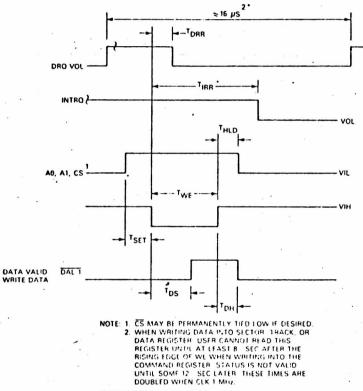

|            | 3.6.2.2       | Floppy Disk Controller Chip Timing                  | 33         |

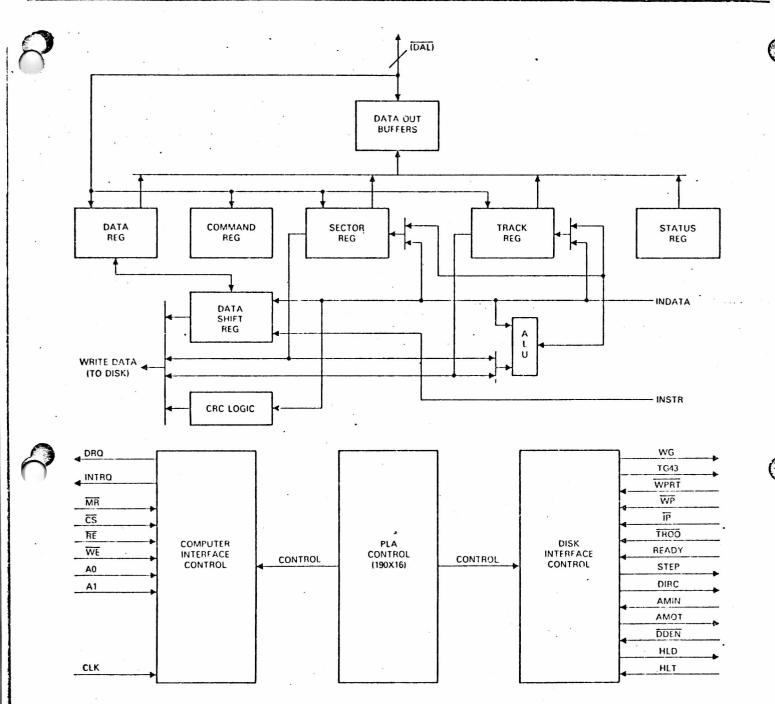

|            | 3.6.2.3       | MFM Disk Controller Block Diagram                   | 35         |

|            | 3.6.3.1       | MLB3 Basic Block Diagram                            | 39         |

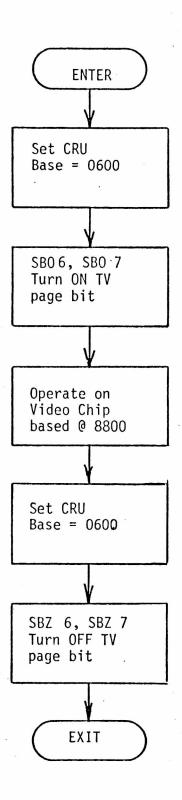

|            | 3.6.3.2       | Basic Flow Chart for CRT5027 Access                 | 40         |

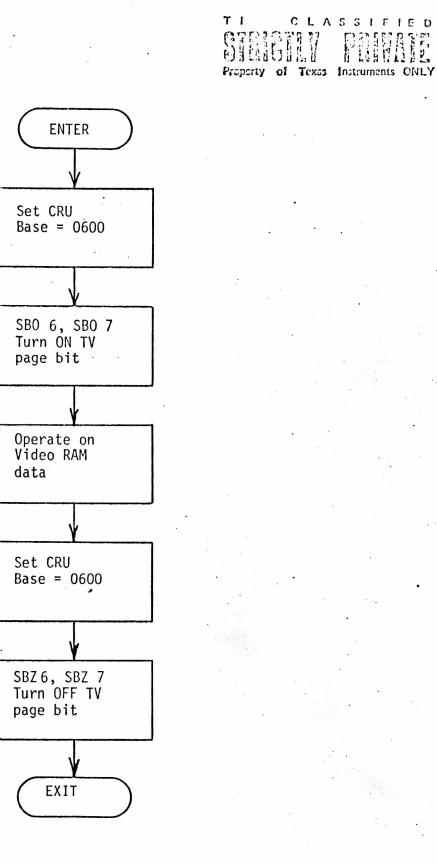

|            | 3.6.3.3       | Basic Flow Chart for Video RAM Access               | 41         |

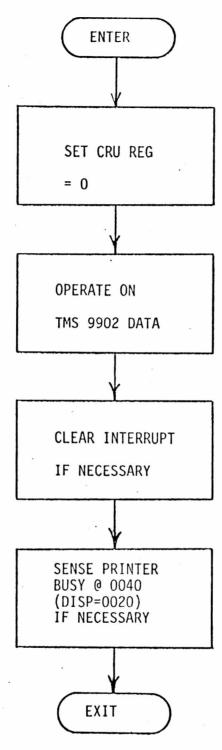

|            | 3.6.3.4       | Basic TMS 9902 Service Flow Chart                   | 43         |

| $\bigcirc$ | 3.6.4.1       | Basic MLB4 Block Diagram                            | 45         |

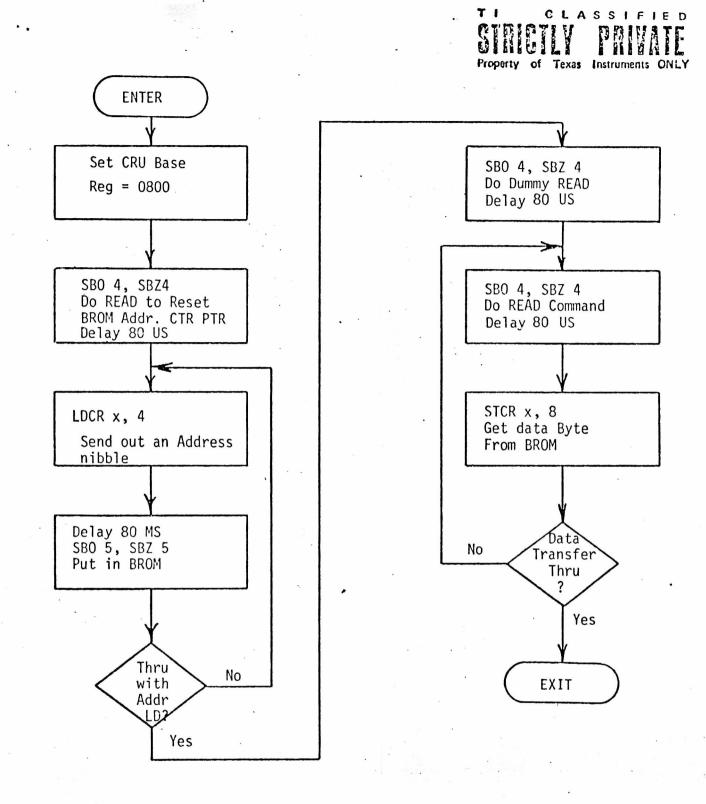

|            | 3.6.4.3       | Basic BROM Access Flow Chart                        | 46         |

|            | 3.7.1         | Keyboard Basic Block Diagram .                      | 50         |

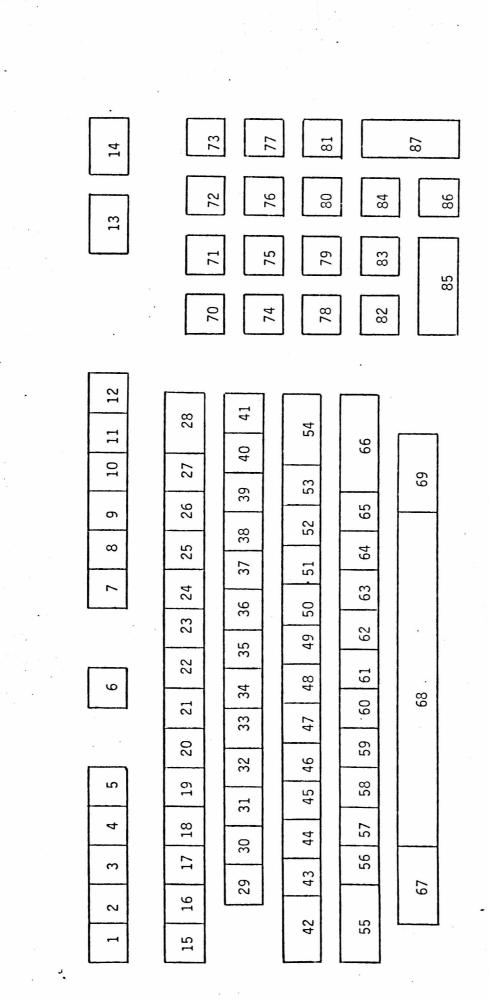

|            | 3.7.2.5       | Keyboard Key Positions                              | 53         |

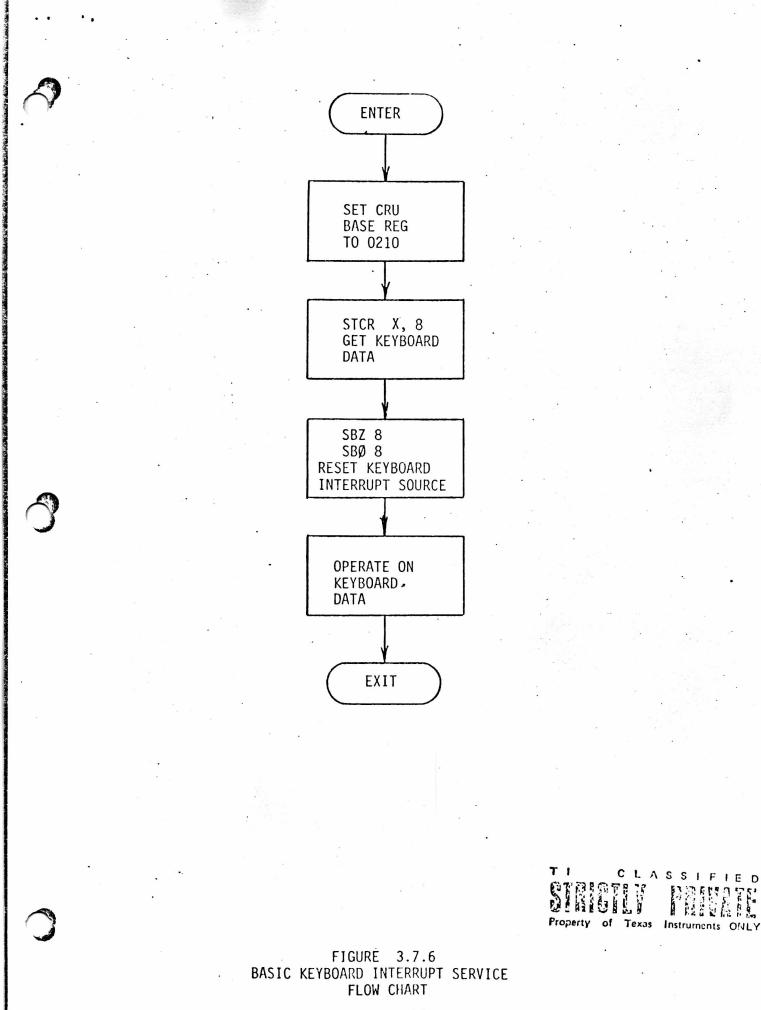

|            | 3.7.6         | Basic Keyboard Interrupt Service Flow Chart         | 56         |

|            | 3.8.1         | Printer Basic Block Diagram                         | 58         |

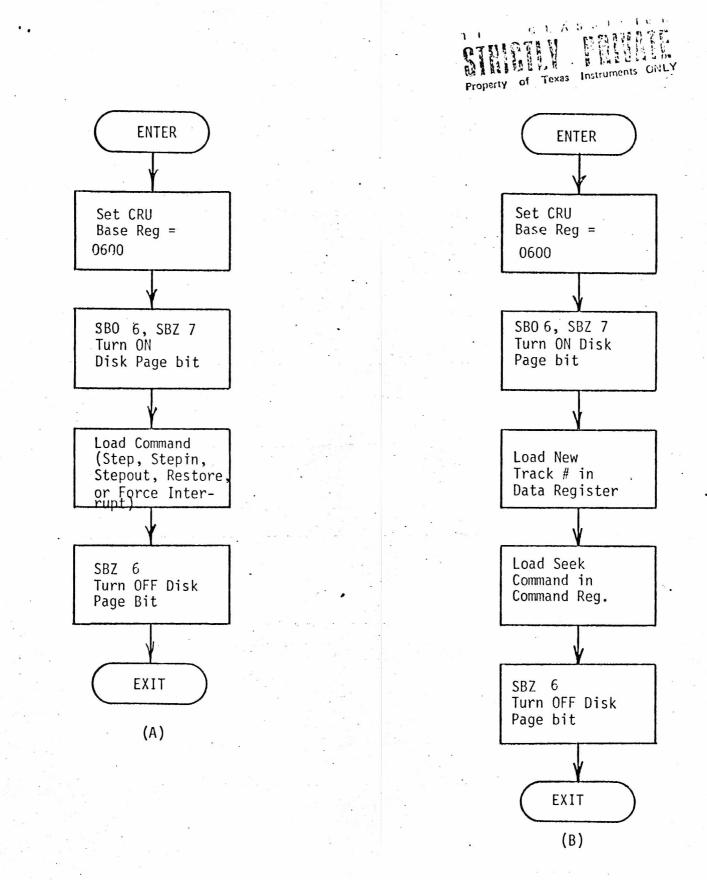

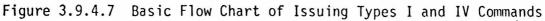

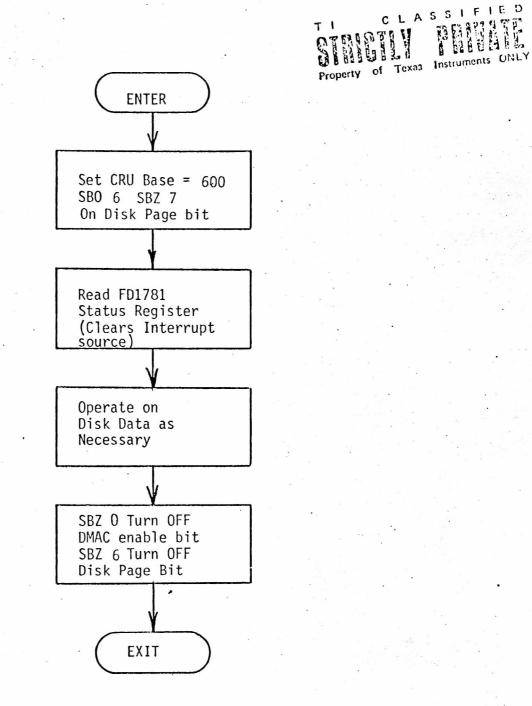

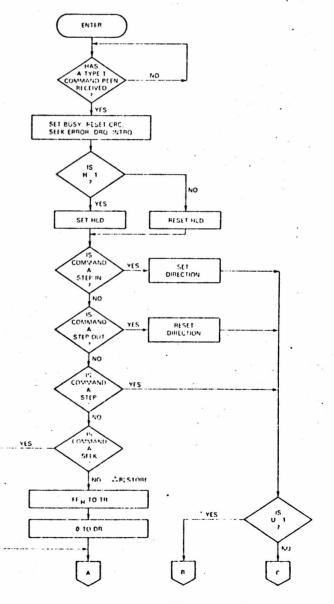

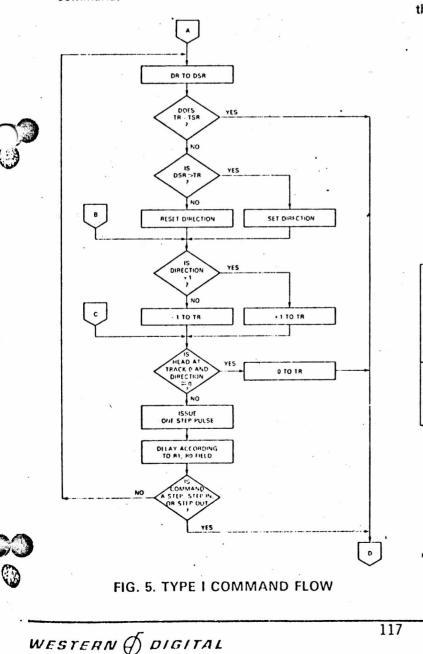

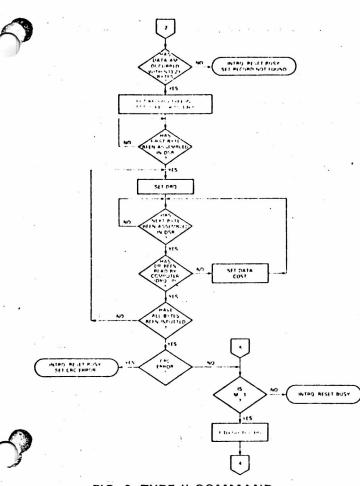

|            | 3.9.4.7       | Basic Flow Chart of Issuing Types I and IV Commands | 70         |

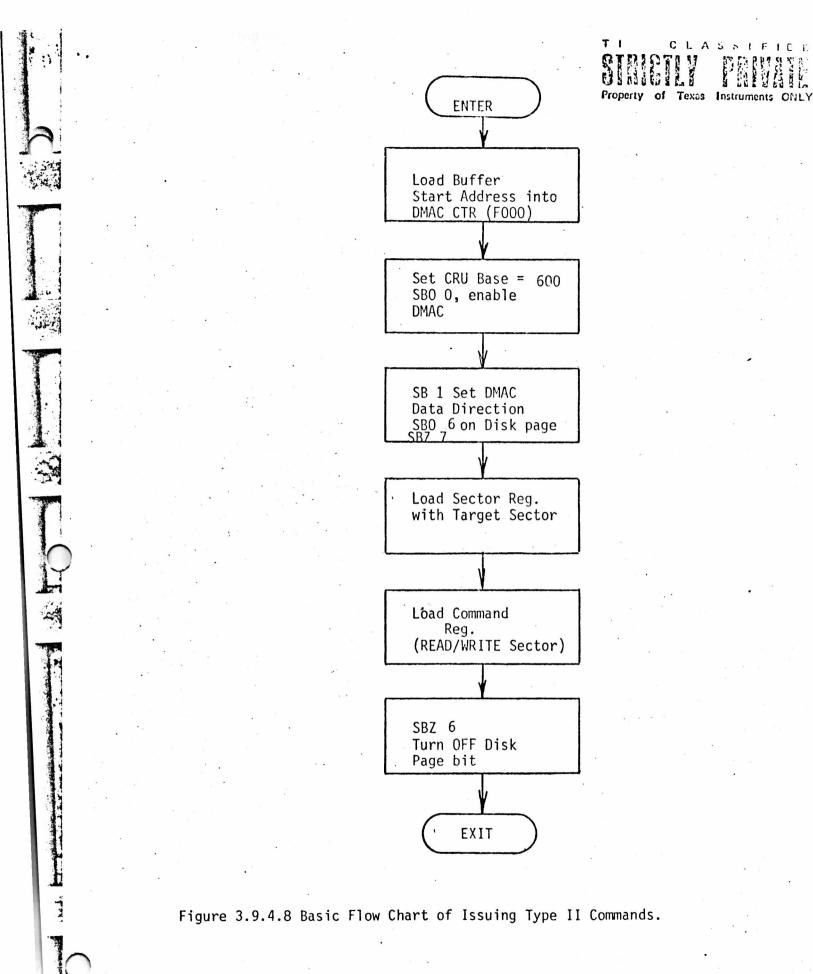

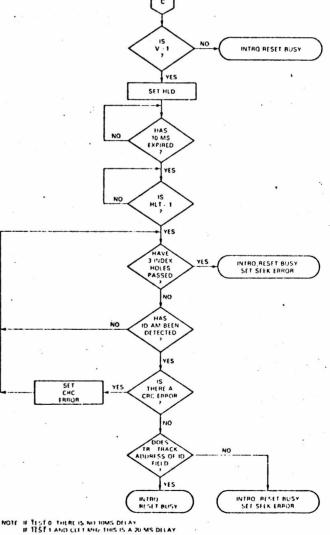

|            | 3.9.4.8       | Basic Flow Chart of Issuing Type II Commands        | 71         |

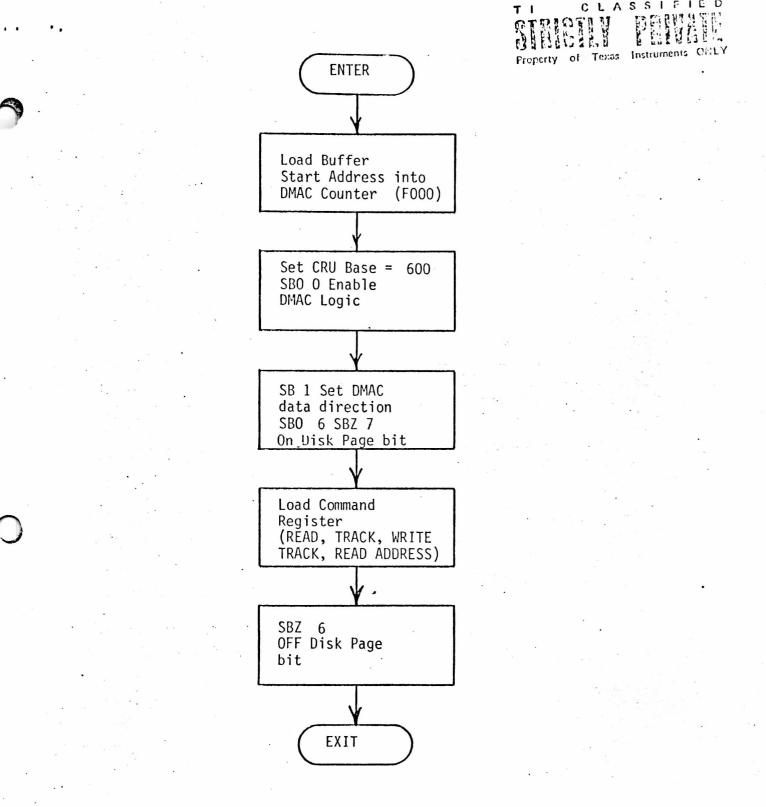

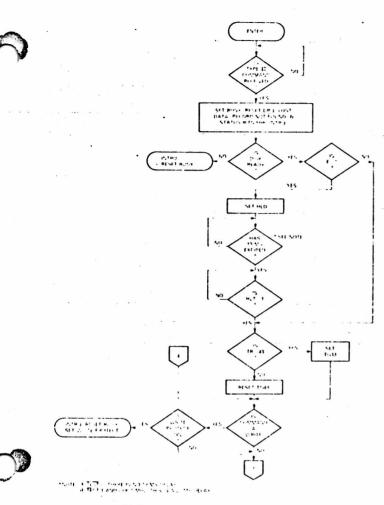

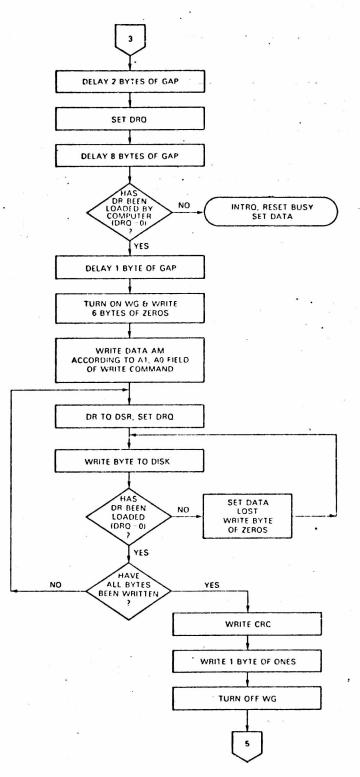

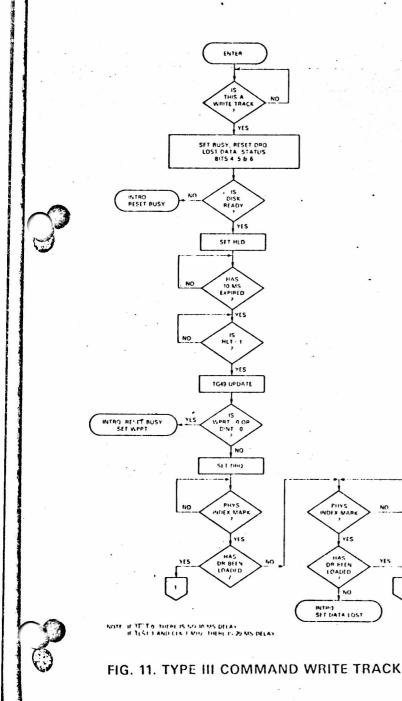

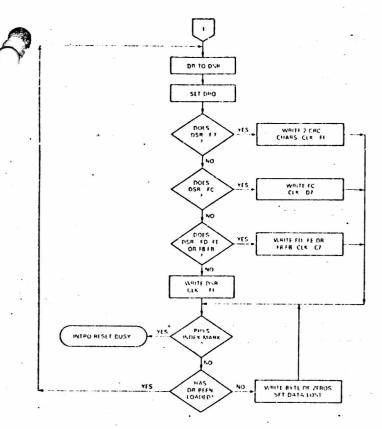

|            | 3.9.4.9       | Basic Flow Chart on Initiating a Type III Command   | 72         |

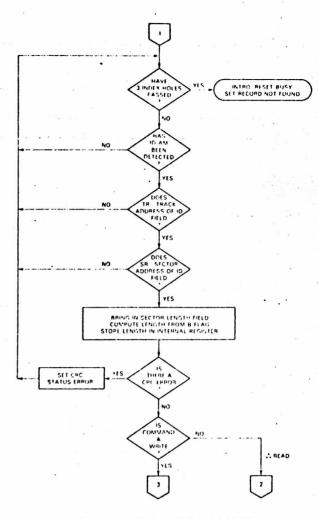

|            | 3.9.4.10      | Basic Flow Chart of Disk Interrupt Service          | 73         |

|            | 3.10.20       | Power Supply Power OFF/ON Characteristics           | 77         |

|            | 3.10.26       | Case Dimensions                                     | 80         |

# LIST OF TABLES

TI

53

CLAS FIV F

Property of Texas Instruments ONLY

S

IF

ED

|                |                                                         | PAG             |

|----------------|---------------------------------------------------------|-----------------|

| Table 3.3      | Interrupt Level Definition, TMS 9901 Controlled         | 22              |

| Table 3.6.1    | Keyboard CRU Definition                                 | 29              |

| Table 3.6.4.3A | BROM CRU Bit Definitions                                | 47              |

| Table 3.6.4.3B | BROM Control Bit Definitions                            | 47              |

| Table 3.7.2.5  | Key Code Definitions                                    | 51              |

| Table 3.8.1    | Printer Command Definition                              | 57              |

| Table 3.8.2    | Motor Stepping Sequence                                 | 59              |

| Table 3.9.4.1  | Floppy Disk Controller Register Memory Space Definition | 63              |

| Table 3.9.4.2  | Command Summary                                         | 64              |

| Table 3.9.4.3  | Command Suggested Parameters                            | 65              |

| Table 3.9.4.4  | Type I Command Status Bit Definitions                   | <sup>-</sup> 65 |

| Table 3.9.4.5  | READ Class Command Status Bit Definitions               | 66              |

| Table 3.9.4.6  | WRITE Class Command Status Bit Definitions              | 66              |

| Table 3.12.1   | RS-232-C Port Pin Definitions                           | 84              |

| Table 3.12.2   | CRU Port Pin Definitions                                | 85              |

| Table 3.12.3   | Monitor Port Pin Definitions                            | 85              |

| Table 3.12.4   | GPIB Pin Definitions                                    | 86              |

| Table 6.1      | Devices Which Require 100% Preassembly Testing          | 94              |

TI CLASSIFIED OTHOTAL DATE Property of Texas Instruments ONLY

# Introduction

1.0

The SR-70 is a small business oriented machine that has the following characteristics:

ULAUSIFIED

Instruments

**Fexas**

- 0 A TMS 9900 Microprocessor based system

- 0 32K bytes of Dynamic RAM

- 0 32K bytes of ROM

- 0 Dual, single-sided, MFM floppy disk drives

- 0 12" video monitor

- 0 Solid State Software library in TMC 0350 BROM's (512K bytes)

- 0 RS-232-C outside world interface

- 0 2K line CRU outside world interface

- 0 IEEE 488 bus interface option

- 0 48 column printer

- 0 QUERTY keyboard

#### Applicable Documents

- O Commercial Personal Computer Total Marketing Plan (SR-70) TI Strictly Private

- 0 Equipment Group TTL Designers Guide, Dwg 932142

- O CALD # 1031293, # 1030226 for motor drive characteristics

- 0 CALD # 101824-1 Keyboard Mechanical Definition

- O CALD **#** 1500506-4 Thermal Paper

- 0 CALD # 1018454 Printhead Specifications

## 2.1 Symbol Definition

Signal names followed by an asterix denote a Low true signal (MEMEN\*).

Since some system functions may span several clock cycles, the number of the clock cycles shall be appended to the end of the clock phase number. PH3\*(2) denotes the second PH3\* clock in the time period of interest. The CPU MEMEN\* signal will have a PH1(1) and a PH1(2) associated with it.

Standard LE and TE denote the Leading Edge and Training edge respectively of a function.

#### Symbol Definition (Continued)

All CRU and memory addresses are assumed to be hexadecimal unless otherwise designated.

7 1

CLASSIFIED

Texas Instruments

A period (.) in a logical expression denotes the AND function and the plus (+) denotes the OR function.

#### 3.0 Hardware Description

All logic design shall be done according to practices outlined in the Equipment Group # 932142 TTL Logic Designers Guide to provide a stable system. This design must also be cost effective with built in learning, producible in volume, reliable, and maintainable if the SR-70 is to be a successful product.

## 3.1 SR-70 System Memory Map

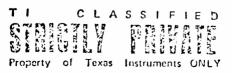

The System Memory Map is shown in FIG. 3.1, and is composed of three basic spaces. There are 32K bytes of DRAM, 8K bytes of paged space, and 24K bytes of ROM space.

The paged space is the "garbage can space" in that all memory mapped internal IO resides in this space along with any Primary ROM over 24K. This 8K byte paged space is shared between 8K bytes of ROM and two memory mapped peripherals. A pair of CRU bits are utilized as page control bits to select one desired function out of four in the 8K byte paged space.

The Floppy Disk Controller chip is accessed at a memory base of 9000 after its CRU page has been selected (060C=1 and 060E=0).

The SMC CRT5027 chip is accessed at a memory base of 8800, and the 2K byte video character buffer at 8000 after its CRU page has been selected (060C=1, 060E=1).

The 8K byte paged ROM between 8000 and 9FFF is accessed when the ROM page is selected (060C=0, 060E=0).

Any other future functions may be easily added to this space in a simi lar method utilizing existing spare (Not Assigned) CRU output bits. Static RAM's, test ROM's, etc. fall into this category.

The Primary ROM page is selected by either the Power On Clear or Software Reset.

2.1

FIGURE 3.1 SR-70 MEMORY SEGMENTATION

|         |                            |                                      | • •                                                                                                                                                                                         | CLA                    |

|---------|----------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Detail  | ed SR-70 Memo              | ory Map                              | Property of                                                                                                                                                                                 | Texas                  |

| ADDRESS | S RANGE                    | 1                                    | FUNCTION ADDRESSED                                                                                                                                                                          | 10203                  |

| 0000    | 7FFF                       |                                      | DRAM - 32K Bytes                                                                                                                                                                            | R/W                    |

| 8000    | 9FFF                       |                                      | ROM (MLB4) ROM page bit @ 602<br>must be high                                                                                                                                               | R                      |

| 8000    | 87FF                       |                                      | TV Buffer - 2K Bytes<br>TV PAGE bit @ 060E must be set                                                                                                                                      | R/W<br>high            |

| 8800    | 8FFF                       |                                      | TV Controller Chip                                                                                                                                                                          |                        |

| 8800    | 880C                       |                                      | TV Chip setup/control data<br>See Appendix J for SMC CRT 5027<br>definition                                                                                                                 | W                      |

|         | 881A N<br>881C N           | MSBY<br>MSBY<br>MSBY<br>MSBY         | Cursor row position (set)<br>Cursor column position (set)<br>Cursor row position (sense)<br>Cursor column position (sense)<br>TV PAGE is selected when the bit:<br>@ 060C and 060E are High | W<br>W<br>R<br>R<br>3  |

| 9000    | 9FFF N                     | MSBY                                 | Floppy Disk Controller Chip                                                                                                                                                                 |                        |

|         | 9000 M<br>9002 M<br>9004 M | MSBY<br>MSBY<br>MSBY<br>MSBY<br>MSBY | Status Register<br>Command Register<br>Track Register (R=900A)<br>Sector Register (R=900C)<br>Data Register (R=900E)<br>Disk PAGE is selected for CRU bit<br>060C=1 and 060E=0              | R<br>W<br>W<br>W<br>ts |

| A000    | FFFE                       |                                      | ROM (MLB4A,B)                                                                                                                                                                               | R                      |

ΤI

CLASSIFIED

Instruments ONLY

## SR-70 System CRU Map

3.1.1

3.2

The SR-70 Communications Register Unit (CRU) space is divided in half with the lower 2K bit serving the SR-70 internal functions. This 2K space is in turn decoded into 256 bit spaces, and these blocks serve the various functions with no further upper address decode (multiple addresses for the same function within the 256 bit block). The TMS 9902 RS-232-C controller space is an exception to this type of decode.

The upper 2K bits form the basis for the CRU Port for Outside World use. The user who implements his own logic on this port determines bit definitions.

0

# Detailed SR-70 CRU Map

uments Inst Texas Prope

CLASSIFIED

ONLY

All CRU Address spaces (but the one at 0000) utilized for internal machine control have an address span of 1FE, and functions are not uniquely decoded in this span (multiple addressing for the same function is possible). An example of this for a CRU base of OEOO is that the DMAC enable bit found at OE40. Address shown in this map shall be used exclusively to provide for future expansion.

NAME

### Base Address

Displacement

ADDRESS<sub>2</sub>

0 1 2 3 4

01000

Function

DESCRIPTION

Not used (always = 0)

RBR7-RBR0 Receive Buffer Register

TMS 9902 ACC Input Bit Address Assignments

TI

0000

|                | 1   | 1 | 1 | 1 | 1     | 31 | INT    | Interrupt                      |

|----------------|-----|---|---|---|-------|----|--------|--------------------------------|

|                | 1   | 1 | 1 | 1 | 0     | 30 | FLAG   | Register Load Control Flag Set |

|                | . 1 | 1 | 1 | 0 | 1     | 29 | DSCH   | Data Set Status Change         |

|                | 1   | 1 | 1 | 0 | 0     | 28 | CTS    | Clear To Send                  |

| •              | 1   | 1 | 0 | 1 | 1     | 27 | DSR    | Data Set Ready                 |

| 김 귀엽 없을 좀 한 것. | 1   | 1 | 0 | 1 | 0     | 26 | RTS    | Request To Send                |

|                | 1   | 1 | 0 | 0 | 1     | 25 | TIMELP | Timer Elapsed                  |

|                | 1   | 1 | 0 | 0 | 0     | 24 | TIMERR | Timer Error                    |

| TMS 9902       | 1   | 0 | 1 | 1 | 1     | 23 | XSRE   | Transmit Shift Register Empty  |

| (MLB3)         | 1   | 0 | 1 | 1 | 0     | 22 | XBRE   | Transmit Buffer Register Empty |

|                | . 1 | 0 | 1 | 0 | 1     | 21 | RBRL   | Receive Buffer Register Loaded |

|                | 1   | 0 | 1 | 0 | 0     | 20 | DSCINT | Data Set Status Change Interr. |

|                | 1   | 0 | 0 | 1 | 1     | 19 | TIMINT | Timer Interrupt                |

|                | 1   | 0 | 0 | 1 | 0     | 18 |        | Not used (always = 0)          |

|                | 1   | 0 | 0 | 0 | 1     | 17 | XBINT  | Transmitter Interrupt          |

|                | 1   | 0 | 0 | 0 | 0     | 16 | RBINT  | Receiver Interrupt             |

|                | 0   | 1 | 1 | 1 | 1     | 15 | RIN    | Receiver Input                 |

|                | 0   | 1 | 1 | 1 | 0     | 14 | RSBD   | Receiver Start Bit Detect      |

|                | 0   | 1 | 1 | 0 | 1     | 13 | RFBD   | Receive Full Bit Detect        |

|                | 0   | 1 | 1 | 0 | 0     | 12 | RFER   | Receive Framing Error          |

|                | 0   | 1 | 0 | 1 | 1     | 11 | ROVER  | Receive Overrun Error          |

|                | 0   | 1 | 0 | 1 | 0     | 10 | RPER   | Receive Parity Error           |

|                | 0   | 1 | 0 | 0 | 1     | 9  | RCVERR | Receive Error                  |

|                | -   |   | - |   | 1.001 | -  |        |                                |

8

7-0

ADDRESS<sub>10</sub>

3.2.1

# 3.2.1

Detailed SR-70 CRU Map (Continued)

Property of Texas Instruments ONLY

CL

S S

ΕD

ä

Base Address

Displacement

# Function

ΤI

0000

TMS 9902 ACC Output Bit Address Assignments

| ADDRESS,     | ADDRESS <sub>10</sub> |             |                                         |                        |

|--------------|-----------------------|-------------|-----------------------------------------|------------------------|

| 0 1 2 3 4    | 10                    | NAME        | DESCRIPTION                             |                        |

| 11111        | 31                    | RESET       | Reset device                            |                        |

|              | 30-22                 | -           | Not used                                |                        |

| 10101        | 21                    | DSCENB      | Data Set Status Cha<br>Interrupt Enable | nge                    |

| 10100        | 20                    | TIMENB      | Timer Interrupt Ena                     | ble                    |

| 10011        | 19                    | XBIENB      | Transmitter Interru                     | pt Enable              |

| 10010        | 18                    | RIENB       | Receiver Interrupt                      |                        |

| 10001        | 17                    | BRKON       | Break On                                |                        |

| 10000        | 16                    | RTSON       | Request To Send On                      |                        |

| 0 1 1 1 1    | 15                    | TSTMD       | Test Mode                               |                        |

| 0 1 1 1 0    | 14                    | LDCTRL      | Load Control Regist                     | er                     |

| 01101        | 13                    | LDIR        | Load Interval Regis                     | ter                    |

| 01100        | 12                    | LRDR        | Load Receiver Data                      | Rate Regis.            |

| 01011        | 11                    | LXDR        | Load Transmit Data                      | Rate Regis.            |

|              | 10-0                  |             | Control, Interval,                      | -                      |

|              |                       |             | Data Rate, Transmit                     |                        |

|              |                       |             | & Transmit Buffer R                     |                        |

| Displacement | Miscellan             | eous CRU In | put Bit Assignment                      | Test Only              |

| 0            | External<br>BUSY      | Printer (or | RS-232-C port)                          | 1 = BUSY,<br>0 = Ready |

| 1            | Not Assig             | ned         |                                         | -                      |

| 2            | Not Assig             |             |                                         |                        |

| 3            | Not Assig             |             |                                         |                        |

| 4            | -                     |             | nnect to out bit at                     | 0606                   |

|              | Not Assig             |             |                                         |                        |

| 5<br>6       | Not Assig             |             |                                         |                        |

| 7            | Not Assig             |             |                                         |                        |

|              | U U                   |             |                                         |                        |

# 3.2.1

Detailed SR-70 CRU Map (Continued)

Property of Texas Instruments ONLY

TI

CLASSIFIED

| Base Address | Displacen  | ient         | Function                               |           |        |  |

|--------------|------------|--------------|----------------------------------------|-----------|--------|--|

| 0200         | 0<br>1     | CR=0         | Control bit (CR)                       |           | R/W    |  |

|              | े <u>1</u> | m m          | INT1*- Power Going Down<br>INT1 - Mask |           | R<br>W |  |

|              | 2          | 11           | INT2*- Keyboard                        |           | R      |  |

|              | 2          | 11           | INT2 - Mask                            |           | W      |  |

|              | 3          | 11           | INT3*- Interval Timer                  |           | R      |  |

|              | 3          | 11           | INT3 - Mask                            |           | Ŵ      |  |

|              | 4          | Ħ            | INT4*- Not Assigned                    |           | R      |  |

| TMS 9901     | 4          | 11           | INT4 - Mask                            |           | W      |  |

| (MLB1)       | 5          | 19           | INT5*- Disk                            |           | R      |  |

|              | 5          | 11           | INT5 - Mask                            |           | Ŵ      |  |

|              | 6          | n            | INT6*- CRU Port I1                     |           | R      |  |

|              | 6          | 11           | INT6 - Mask                            |           | W      |  |

|              | 7          | 11           | INT7*- UART 9902                       |           | R      |  |

|              | 7          | _ <b>n</b>   | INT7 - Mask                            |           | W      |  |

|              | 8          | п            | INT8*- Print Complete                  |           | R      |  |

|              | 8          | 11           | · INT8 – Mask                          |           | W      |  |

|              | 9          | 11           | INT9*- Not Assigned                    |           | R      |  |

|              | 9          | 11           | INT9 - Mask                            |           | W      |  |

|              | A          | 11           | INT10*- CRU Port I2                    | ·         | R      |  |

|              | A          | <b>n</b> .   | INT10 - Mask                           |           | W      |  |

|              | В          | n            | INT11*- CRU Port I3                    |           | R      |  |

|              | В          | Ħ            | INT11 - Mask                           |           | W      |  |

|              | С          | n            | INT12*- CRU Port I4                    |           | R      |  |

|              | C          | n<br>        | INT12 - Mask                           |           | W      |  |

|              | D          | "            | INT13*- CRU Port 15                    |           | R      |  |

|              | D          | ·            | INT13 - Mask                           |           | W      |  |

|              | E          | 1            | Assigned to KBD Data                   |           | -      |  |

|              | F<br>10 C  | R=Don't Care | Assigned to KBD Data                   |           | <br>D  |  |

|              | 10 0       | n=Don't Care | KBD Receive Data, LSB<br>KBD Data      |           | R<br>R |  |

|              | 12         | 11           | KBD Data                               |           | R      |  |

|              | 12         | 11           | KBD Data                               |           | R      |  |

|              | 14         | 11           | KBD Data                               |           | R      |  |

|              | 15         | 11           | KBD Data                               |           | R      |  |

|              | 16         | n            | KBD Data                               |           | R      |  |

|              | 10         | n            | KBD Data MSB                           |           | R      |  |

|              | 18         | n            | KBS Interrupt Reset Bit                | (KBIRST*) | W      |  |

|              | 10         |              | low to Reset KBD Interr                |           |        |  |

|              |            |              | KBD Interrupt(source                   |           |        |  |

|              |            |              | disabled when this bit :               |           |        |  |

|              |            |              |                                        |           |        |  |

TMS 9901 Programmable Real Time CLock The clock consists of a 14 bit counter that decrements at a rate that results in a maximum interval of 349 ms with a resolution of 21.3 us, and can be used as either an interval timer or as an event timer.

The clock is accessed by writing a one into the control bit to force CRU bits 1-15 to clock mode. Writing a nonzero value into the clock register then enables the clock and sets its frequency. The clock functions as an interval timer by decrementing to zero, issuing an interrupt, and

#### 3.2.1 Detailed SR-70 CRU Map (Continued)

Property of Texas Instruments ONLY

C L A S S I F I E D

ΤI

TMS 9901 Programmable Real Time Clock (Con't) restarting at the programmed start value. When the clock interrupt is active, the clock mask (mask bit 3) must be written into (with either a "1" or a "0") to clear the interrupt.

If a value other than that initially programmed is required, a new 14-bit clock start value is similarly programmed by executing a CRU write operation to the same locations. During programming the decrementer is restarted with the current start value after each start value bit is written. A timer restart can be easily implemented by writing a single bit to any of the clock bits.

The clock is disabled by a system reset by writing a zero value into the clock register. Enabling the clock programs the third priority interrupt (INT3\*) as the clock interrupt and disables generation of interrupts from the INT3\* input pin. When accessing the clock all interrupts should be disabled to ensure that system integrity is maintained.

The clock can also function as an event timer since whenever the device is switched to the clock mode, by writing a one to the control bit, the current value of the clock is stored in the clock read register. Reading this value, and thus the esapsed event time, is accomplished by executing a 14 bit CRU read operation (addresses 1-14 displaced from 0200).

The current status of the machine can always be obtained by reading the control (address zero) bit. A "O" inidicates the machine is in a interrupt mode. A "1" read on the control bit indicates that the TMS 9901 is in the clock mode.

A software reset RST2\* can be performed by writing a "1" to the control bit followed by writing a "1" to bit 15 (displaced from 0200), which forces all I/O ports to the input mode.

| Base Ac | ldress | Displacement | Function                                     |             |

|---------|--------|--------------|----------------------------------------------|-------------|

|         | 0400   |              | To be used for future ADDs control           |             |

|         | 0600   | 0<br>1<br>2  | Not Assigned<br>Not Assigned<br>Not Assigned | W<br>W<br>W |

|         |        | 2            | NOU ASSIGNED                                 | n           |

|   | '.<br>.2.1 Deta | ailed SR-70 CRU                                | Map (Contin | uued)                                                                                                                                                                                                 | TI CLA<br>STRIGTLY<br>Property of Texas                                                                                             | PAWATE                                         |

|---|-----------------|------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| B | ase Address     | Displacemen                                    | <u>it</u>   | F                                                                                                                                                                                                     | unction                                                                                                                             |                                                |

| 0 | 0600            | 3                                              |             | -<br>CRU Test Loop                                                                                                                                                                                    | CRU OUT bit 3 is<br>conected to CUR<br>IN bit 4 @ 0048<br>to provide a test                                                         | W                                              |

|   |                 | 4                                              |             | signali<br>require<br>a zero                                                                                                                                                                          | ible device for<br>ng the operator, ar<br>s a one to be on ar<br>to be off. A 50% o<br>n a 1 sec period is                          | W<br>nd<br>nd<br>duty                          |

|   |                 | 5<br>6,7<br>NOTE: ALL                          |             | Print Request<br>Page select bi<br>is primary ROM<br>is not assigne<br>is Disk page,<br>the TV page.                                                                                                  | (ON, OFF Protocol)<br>ts. bit 6=0, bit 7<br>page, bit 6=0, bit<br>d page, bit 6=1, bi<br>and bit 6=1, bit 7=<br>by Power On Clear c | t 7=1<br>t 7=0<br>1 is                         |

|   |                 | Soft                                           | ware Reset  |                                                                                                                                                                                                       |                                                                                                                                     |                                                |

|   | 0800            | 0<br>0<br>1                                    |             | Address Nibble<br>BROM data Byte<br>Address Nibble<br>BROM Data Byte                                                                                                                                  | bit #l LSB<br>bit #2                                                                                                                | W<br>R<br>W<br>R                               |

|   |                 | 2                                              |             | Address Nibble<br>BROM Data Byte                                                                                                                                                                      | bit # 3<br>bit # 3                                                                                                                  | W<br>R                                         |

| • |                 | 3<br>3<br>4<br>5<br>5<br>6<br>6<br>7<br>7<br>7 |             | Address Nibble<br>BROM Data Byte<br>BROM IO Contro<br>BROM Data Byte<br>BROM Data Byte<br>BROM Data Byte<br>BROM Group Sele<br>BROM Group Sele<br>BROM Data Byte<br>See table 3.6.9<br>functional def | bit # 4<br>l Line<br>bit # 5<br>l Line<br>bit #6<br>ect LSB<br>bit #7<br>ect MSB<br>bit # 8 MSB<br>5.4B for I1, I0                  | W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W<br>R |

|   | 0000            |                                                |             | Not Assigned                                                                                                                                                                                          |                                                                                                                                     |                                                |